Diferență între revizuiri ale paginii „CID Lab Lucrarea 0”

De la WikiLabs

Jump to navigationJump to search| Linia 23: | Linia 23: | ||

** Inversoarele de pe placă au deja conectate intrările la porțile ȘI-NU/SAU-NU asociate, deci pinii de pe intrarile inversoarelor nu pot fi folosiți pentru a lega intrarea inversoarelor cu ieșirea unei alte porți de pe placă. | ** Inversoarele de pe placă au deja conectate intrările la porțile ȘI-NU/SAU-NU asociate, deci pinii de pe intrarile inversoarelor nu pot fi folosiți pentru a lega intrarea inversoarelor cu ieșirea unei alte porți de pe placă. | ||

* Nu se vor lega ieșirile porților la VCC sau masă | * Nu se vor lega ieșirile porților la VCC sau masă | ||

| + | |||

| + | Schema electrică a plăcii de dezvoltare este disponibilă aici: [[Fișier:placa_integrate_cid_proiect.pdf]] | ||

== Cerințe == | == Cerințe == | ||

Versiunea de la data 22 februarie 2015 11:30

Noțiuni și cunoștințe necesare

Placa de dezvoltare

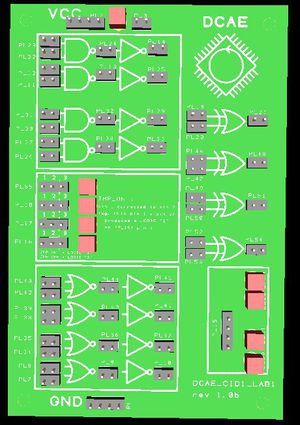

În acest laborator veti folosi o placa de dezvoltare echipată cu circuite integrate digitale ce oferă următoarele funcții logice:

- 4 porți ȘI-NU, la ale căror ieșiri sunt conectate inversoare, putând astfel fi folosite ca porți ȘI

- 4 porți SAU-NU, la ale căror ieșiri sunt conectate inversoare, putând astfel fi folosite ca porți SAU

- 4 porti XOR

- 4 intrări logice selectabile prin câte un jumper, și echipate cu câte un LED care indică valoarea logică selectată (LED aprins pentru 1 logic, stins pentru 0 logic)

- 4 conexiuni la alimentare (VCC de 5V)

- 4 conexiuni la masă

- 4 LED-uri ce pot fi folosite pentru a vizualiza valoarea logică a oricărui punct din circuit (LED aprins pentru 1 logic, stins pentru 0 logic)

Reguli de folosire a plăcii de dezvoltare:

- Placa trebuie alimentată folosind un cablu USB conectat la calculator, astfel încât LED-ul de alimentare să fie aprins

- Ieșirile unei porți pot fi conectate la intrările altei porți prin fire, ce vor fi puse la dispoziție împreună cu placa de dezvoltare

- Nu se vor lega între ele ieșirile a două porți

- Atenție, fiecare intrare de poartă pe placă are doi pini, dintre care maxim unul va fi conectat la ieșirea unei alte porți, celălalt putând fi legat la intrarea unei alte porți

- Inversoarele de pe placă au deja conectate intrările la porțile ȘI-NU/SAU-NU asociate, deci pinii de pe intrarile inversoarelor nu pot fi folosiți pentru a lega intrarea inversoarelor cu ieșirea unei alte porți de pe placă.

- Nu se vor lega ieșirile porților la VCC sau masă

Schema electrică a plăcii de dezvoltare este disponibilă aici: Fișier:Placa integrate cid proiect.pdf

Cerințe

Creați un proiect nou în Xilinx ISE, pentru dispozitivul FPGA de pe placa Nexys2. Creați un fișier sursă Verilog în cadrul proiectului, și copiați modulul următor în fisier.

module OrGate(

output out,

input in1,

input in2

);

assign out = in1 | in2;

endmodule

Creați un fișier de constrângeri și scrieți constrângerile necesare pentru ca intrările și ieșirile circuitului să fie conectate astfel:

- in1 conectat la SW0

- in2 conectat la SW7

- out conectat la LD3

Implementați proiectul pe placa Nexys și observați funcționalitatea circuitului descris de proiectul Xilinx ISE.