Diferență între revizuiri ale paginii „CID Lab Lucrarea 2”

De la WikiLabs

Jump to navigationJump to search| Linia 9: | Linia 9: | ||

== Cerințe == | == Cerințe == | ||

| − | + | Creați un proiect Xilinx ISE, descrierea Verilog și constrângerile necesare pentru a implementa pe placa Nexys2 circuitul care afișează, pe una din cifrele afișajului cu 7 segmente, primele 4 numere (0, 1, 2, 3), atunci când valoarea binară corespunzătoare este formată prin apăsarea butoanelor BTN0 și BTN2. Astfel, circuitul descris trebuie să respecte următoarele cerințe: | |

| − | + | * are o intrare numită '''binary_input''' de doi biți, bitul cel mai putin semnificativ fiind conectat la BTN0, iar bitul cel mai semnificativ fiind conectat la BTN1 | |

| − | + | * are ieșirile necesare pentru activarea afișajului cu 7 segmente, denumite '''ca''', '''cb''', '''cc''', '''cd''', '''ce''', '''cf''', '''cg''', '''cp''' | |

| − | + | * are ieșirile necesare pentru controlul aprinderii cifrei, denumite '''an0''', '''an1''', '''an2''', '''an3''' | |

| − | + | * folosește operatori logici și blocuri de tip '''assign''' | |

| − | |||

| − | |||

| − | |||

| − | |||

== Cerințe suplimentare (opționale) == | == Cerințe suplimentare (opționale) == | ||

Versiunea de la data 2 martie 2014 14:28

Noțiuni și cunoștințe necesare

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Logică booleană și sisteme de numerație

- Noțiuni de sintaxă Verilog

- Afișajul cu 7 segmente

Cerințe

Creați un proiect Xilinx ISE, descrierea Verilog și constrângerile necesare pentru a implementa pe placa Nexys2 circuitul care afișează, pe una din cifrele afișajului cu 7 segmente, primele 4 numere (0, 1, 2, 3), atunci când valoarea binară corespunzătoare este formată prin apăsarea butoanelor BTN0 și BTN2. Astfel, circuitul descris trebuie să respecte următoarele cerințe:

- are o intrare numită binary_input de doi biți, bitul cel mai putin semnificativ fiind conectat la BTN0, iar bitul cel mai semnificativ fiind conectat la BTN1

- are ieșirile necesare pentru activarea afișajului cu 7 segmente, denumite ca, cb, cc, cd, ce, cf, cg, cp

- are ieșirile necesare pentru controlul aprinderii cifrei, denumite an0, an1, an2, an3

- folosește operatori logici și blocuri de tip assign

Cerințe suplimentare (opționale)

- Descrieți în Verilog un circuit care să poată face suma sau diferența a două numere, conform unui bit de selecție, care este și el intrare a circuitului (Hint: folosiți un operator condițional). Scrieți un modul de test pentru acest circuit în care să-l testați cu câteva perechi de valori de intrare. Simulați circuitul în ModelSim. Sintetizați circuitul și programați placa FPGA disponibilă pentru a implementa fizic funcția dorită. Asignați intrările la elemente de tip switch sau button și ieșirile la elemente de tip led.

- Descrieți în Verilog un circuit care să poată face suma, diferența, produsul sau maximul a două numere, conform unei intrări de selecție. Descrieți circuitul în 3 moduri: folosind un bloc assign și operatorul condițional, folosind un bloc always și sub-blocuri if - else, și folosind un bloc always și un sub-bloc case (vezi implementarea cu blocuri always combinaționale). Scrieți un modul de test pentru acest circuit în care să-l testați cu câteva perechi de valori de intrare. Simulați circuitul în ModelSim. Sintetizați circuitul și programați placa FPGA disponibilă pentru a implementa fizic funcția dorită. Asignați intrările la elemente de tip switch sau button și ieșirile la elemente de tip led.

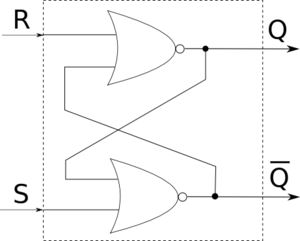

- Descrieți în Verilog o poartă NOR. Folosing acest modul, fire și blocuri de instanțiere, descrieți modulul din figura alăturată. Scrieți un modul de test în care să simulați comportamentul circuitului la tranzițiile (S=0, R=1 -> S=0, R=0 -> S=1, R=0 -> S=0, R=0). Explicați de ce, în cele două cazuri în care intrările sunt S=0, R=0, ieșirea diferă. Ce concluzii puteți trage despre comportamentul circuitului?