CID Lab Lucrarea 3

De la WikiLabs

Noțiuni și cunoștințe necesare

- Logică booleană și sisteme de numerație

- Sintaxă Verilog, instanțiere

- Utilizarea programului de simulare ModelSim

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Memorii ROM, Dispozitiv de IO: Afișajul cu 7 segmente, Decodorul

Cerințe

- Descrieți în Verilog un modul de control pentru sistemul de afișaj cu 7 segmente. Acesta primește ca intrare valoarea care se dorește afișată (între 0 și 9) și la ieșire va genera semnalele de control pentru segmente și semnalele de control AN pentru cifre. Pentru valori mai mari decât 9, se va lumina forma caracterului E urmat de punct.

- Folosiți patru switch-uri pentru selecția valorii

- Folosiți două switch-uri pentru selecția cifrei

- Se vor folosi pentru implementare structuri condiționale Verilog (if/case)

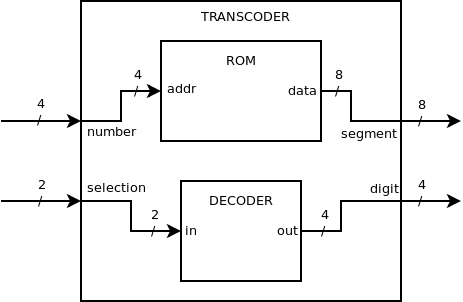

- Circuitul va avea următoarele interfețe:

- intrare number, pe 4 biți, care indică cifra afișată pe 7 segmente

- intrare selection, pe 2 biți, care indică afișajul cu 7 segmente folosit, dintre cele 4 disponibile

- ieșire segment, pe 8 biți, care activează semnalele de control pentru aprinderea segmentelor (CA - CP)

- ieșire digit, pe 4 biți, care activează semnalele de control pentru afișaj (AN0 - AN3)

- Circuitul va fi format din o memorie ROM și un decodor, instanțiate corespunzător, conform figurii:

Recomandări pentru cadrele didactice

- Nu este necesară introducerea nici unei noțiuni noi, acestea fiind deja prezentate la seminar; Eventual se poate exemplifica prima linie din blocul case asociat memoriei ROM.

- Se vor verifica următoarele noțiuni: instanțiere, blocuri condiționale

- Se va răspunde la întrebările studenților.