Diferență între revizuiri ale paginii „CID Lab Lucrarea 5”

De la WikiLabs

Jump to navigationJump to search| Linia 3: | Linia 3: | ||

* [[Introducere. Verilog HDL și ModelSim|Logică booleană și sisteme de numerație]] | * [[Introducere. Verilog HDL și ModelSim|Logică booleană și sisteme de numerație]] | ||

* Sintaxă [[Verilog]] | * Sintaxă [[Verilog]] | ||

| − | |||

* [[Introducere în sinteza pe FPGA. Xilinx ISE]] | * [[Introducere în sinteza pe FPGA. Xilinx ISE]] | ||

* Utilizarea programului de sinteză [[Tutorial Xilinx ISE|Xilinx ISE]] | * Utilizarea programului de sinteză [[Tutorial Xilinx ISE|Xilinx ISE]] | ||

Versiunea de la data 3 mai 2015 21:38

Noțiuni și cunoștințe necesare

- Logică booleană și sisteme de numerație

- Sintaxă Verilog

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Circuite secvențiale

- Memorii RAM

Exemplu

- Se va descrie în Verilog o memorie RAM 16x4b cu un port de citire-scriere sincron.

- Se vor scrie contrâgerile necesare pentru a conecta

- adresa la SW7-4 și data de intrare la SW3-0.

- semnalul de activare a scrierii la unul din butoane (BTN0 ... BTN3).

- ieșirea memoriei la LD3-0.

- intrarea de ceas a memoriei la oscilatorul plăcii Nexys 2.

- Scrieți adresele 3, 6 și 10 cu valorile 2, 1 respectiv 0, apoi citiți-le în aceeași ordine.

Exercițiu

- Descrieți în Verilog o memorie RAM 16x4b cu două porturi:

- Un port sincron de scriere (Write-Only) cu următoarele semnale:

- WR_ADDR - adresa la care se scrie

- WR_EN - comanda de scriere

- WR_DATA - datele scrise

- Un port sincron de citire (Read-Only) cu următoarele semnale:

- RD_ADDR - adresa citită

- RD_EN - comanda de citire

- RD_DATA - datele citite

- Un port sincron de scriere (Write-Only) cu următoarele semnale:

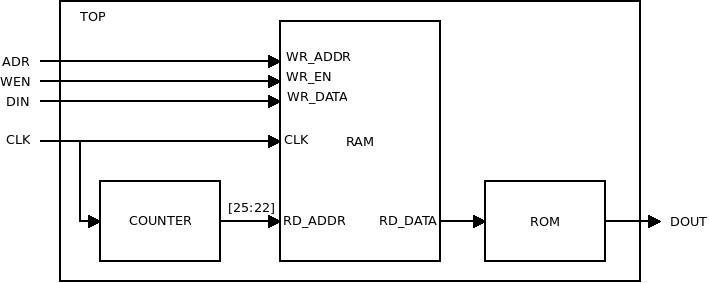

- Memoria va fi instanțiată în modulul TOP conform figurii următoare:

module COUNTER(

input clk,

output reg [31:0] cnt

);

always @(posedge clk) cnt <= cnt + 1;

endmodule

module ROM(

input [3:0] in,

output reg [3:0] out

);

always @(in)

case(in)

0: out = 4'b1010;

1: out = 4'b0110;

2: out = 4'b0011;

3: out = 4'b1110;

4: out = 4'b1011;

5: out = 4'b1111;

6: out = 4'b0111;

7: out = 4'b1100;

8: out = 4'b0001;

9: out = 4'b0101;

10: out = 4'b1101;

11: out = 4'b0000;

12: out = 4'b0010;

13: out = 4'b0100;

14: out = 4'b1000;

15: out = 4'b1001;

endcase

endmodule

- Scrieți constrângerile necesare pentru a conecta porturile modulului TOP:

- DIN la SW7-4,

- ADR la SW3-0,

- WEN la BTN3,

- DOUT la LD3-0,

- intrarea de ceas la oscilatorul plăcii Nexys 2.

- Scrieți memoria RAM cu valorile necesare pentru a produce pe DOUT o secvență de numere indicată de cadrul didactic.