Diferență între revizuiri ale paginii „CID Lab Lucrarea 5”

De la WikiLabs

Jump to navigationJump to search| Linia 16: | Linia 16: | ||

* Descrieți în Verilog un generator de impulsuri cu factor de umplere variabil folosind un registru de numărare de 8 biți. Scrieți un modul de test pentru acest circuit în care semnalul de ceas descris în modulul de test să fie aibă exact perioada ceasului prezent pe placa de dezvoltare. Simulați circuitul în Modelsim. | * Descrieți în Verilog un generator de impulsuri cu factor de umplere variabil folosind un registru de numărare de 8 biți. Scrieți un modul de test pentru acest circuit în care semnalul de ceas descris în modulul de test să fie aibă exact perioada ceasului prezent pe placa de dezvoltare. Simulați circuitul în Modelsim. | ||

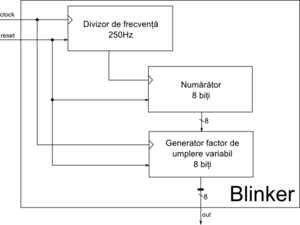

* Folosind modulele anterioare și blocuri de instanțiere, descrieți în Verilog un circuit (numit Blinker) care să respecte schema din figură. Explicați funcționarea lui. Sintetizați circuitul legând ieșirile la leduri și configurați FPGA-ul. | * Folosind modulele anterioare și blocuri de instanțiere, descrieți în Verilog un circuit (numit Blinker) care să respecte schema din figură. Explicați funcționarea lui. Sintetizați circuitul legând ieșirile la leduri și configurați FPGA-ul. | ||

| − | * | + | * Descrieți în Verilog un modul de transmisie serială a datelor pentru date de 8 biți și secvența de sincronizare 3'b101. Scrieți un modul de test în care să transmiteți cateva valori. Simulați circuitul în Modelsim. |

== Cerințe suplimentare (opționale) == | == Cerințe suplimentare (opționale) == | ||

Versiunea de la data 8 aprilie 2012 11:52

Noțiuni și cunoștințe necesare

- Logică booleană și sisteme de numerație

- Sintaxă Verilog

- Utilizarea programului de simulare ModelSim

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Circuite secvențiale, Numărătorul

- Divizorul de frecvență. Generator de impulsuri cu factor de umplere variabil. Transmisia seriala a datelor.

Cerințe

- Descrieți în Verilog un divizor de frecvență care să genereze un ceas cu frecvența de ~250Hz. Scrieți un modul de test pentru acest circuit în care semnalul de ceas descris în modulul de test să fie aibă exact perioada ceasului prezent pe placa de dezvoltare. Simulați circuitul în Modelsim.

- Descrieți în Verilog un generator de impulsuri cu factor de umplere variabil folosind un registru de numărare de 8 biți. Scrieți un modul de test pentru acest circuit în care semnalul de ceas descris în modulul de test să fie aibă exact perioada ceasului prezent pe placa de dezvoltare. Simulați circuitul în Modelsim.

- Folosind modulele anterioare și blocuri de instanțiere, descrieți în Verilog un circuit (numit Blinker) care să respecte schema din figură. Explicați funcționarea lui. Sintetizați circuitul legând ieșirile la leduri și configurați FPGA-ul.

- Descrieți în Verilog un modul de transmisie serială a datelor pentru date de 8 biți și secvența de sincronizare 3'b101. Scrieți un modul de test în care să transmiteți cateva valori. Simulați circuitul în Modelsim.