## Călin BÎRĂ

#### \_\_\_\_\_\_

## [Digital] Electronics by Example When Hardware Greets Software

## Preface

This book contains five chapters with material discussed in a simple manner. It will prove a good book for freshmen. By no means is this book exhaustive – it is only an attempt to put some order in the chaos created in the mind of regular high-school students. It touches subjects such as applied physics, packaging, programming, analog design, digital design, electronic devices, computer architecture but also delves into applied embedded system architecture, design, and implementation.

Chapter one provides an introduction into analog and digital signals and systems including computers and computer networks. Chapter two and three are an introduction into basic digital and analog components, while chapter four is a discussion regarding complexity. Finally, chapter five is a walkthrough on design and implementation of a few mixed-signal systems used in real-life. This book uses a lot of pictures, and instead of citing each of them with their source, I opted to create a table of figures, where I give credit where credit is due.

I thank my family, Paula, close friends, and I am deeply in debt to prof. G.M. Stefan, without whom, I would not have decided to pursue a career in academia. Special thanks go to my work colleagues and friends and to that BMW driver (you know who), to my Toyota Club friend, Mircea Laslău (what an epic entrance on 12<sup>th</sup> July morning!) and MD Anca Cîrstea without whom, I would not have had the time or capability to write or read, this book, during the summer of 2023...

## Table of Contents

| Preface                                                   | 2  |

|-----------------------------------------------------------|----|

| Table of Contents                                         | 3  |

| List of Figures                                           | 7  |

| List of Tables                                            | 12 |

| List of Acronyms                                          | 13 |

| 1. Brief Introduction to Digital Circuits and Programming | 19 |

| 1.1 Analog signals                                        | 19 |

| 1.2 Digital signals                                       | 19 |

| 1.3 Digit, number, and radix                              | 21 |

| 1.4 Digital systems                                       | 22 |

| 1.5 Programming a 4-loops digital system (computer)       | 23 |

| 1.6 Components of a computer                              | 23 |

| 1.7 Computer networks                                     | 31 |

| 1.8 Network services                                      |    |

| 1.9 Reaction and feedback                                 |    |

| 2. Basic hardware bricks                                  |    |

| 2.1 Binary and Boolean Logic                              |    |

| 2.2 Digital Gates and Digital Circuits                    |    |

| 2.3 Analog Elements / Devices / Circuits                  | 41 |

| 2.3.1. Resistors                                          | 41 |

| 2.3.2. Capacitors                                         | 44 |

| 2.3.3. Inductors                                          |    |

| 2.3.4. Semiconductors                                     |    |

| 2.3.4.2 Transistors                                       | 53 |

| 2.3.5 Switches                                            | 57 |

| 2.4 Prerequisites for typical analog applications         | 59 |

| 2.4.1 Prerequisites: the decibel (dB)                     | 59 |

| 2.4.2 Prerequisites: Fourier transform and Fourier series | 63 |

| 2.4.3 Prerequisites: the Doppler effect                   | 64 |

| 2.4.4 Prerequisites: the electromagnetic waves            | 65 |

| 2.5 Typical analog applications                                     | 66 |

|---------------------------------------------------------------------|----|

| 2.5.1 Filters and filtering                                         | 66 |

| 2.5.2 AC mains. Frequency. Maximum voltage, effective (rms) voltage | 68 |

| 2.5.3 Cubic power supplies                                          | 69 |

| 2.5.4 Step-up and step-down DC/DC converters                        | 71 |

| 2.6 Batteries                                                       | 75 |

| 2.7 Data transmission and conversion                                | 82 |

| 2.7.1 SPI communication protocol                                    | 83 |

| 2.7.2 I2C communication protocol                                    | 84 |

| 2.7.3 U(S)ART communication protocol                                |    |

| 2.8 Microcontrollers and processors                                 |    |

| 2.8.1 Resources: I/Os (input/output pins)                           | 90 |

| 2.8.2 Resources: Prescaler                                          | 90 |

| 2.8.3 Resources: Timer                                              | 91 |

| 2.8.3 Resources: Watchdog timer (WDT)                               | 92 |

| 2.8.4 Resources: Brown-out detect (BOD)                             | 92 |

| 2.8.5 Resources: Analog to Digital Converter (ADC)                  | 92 |

| 2.8.6 Resources: Digital to Analog Converter (DAC)                  | 93 |

| 2.8.7 Resources: Comparators                                        | 94 |

| 2.8.8 Resources: RAM memory                                         | 94 |

| 2.9 FPGAs                                                           | 95 |

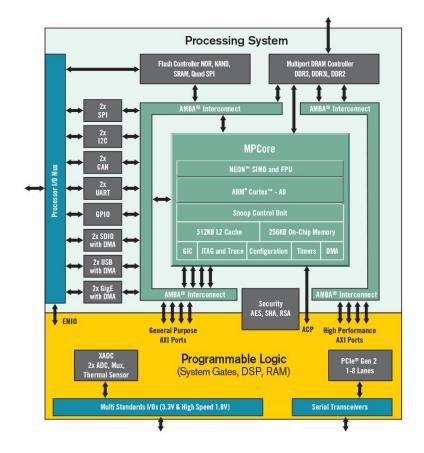

| 2.10 SOCs                                                           | 95 |

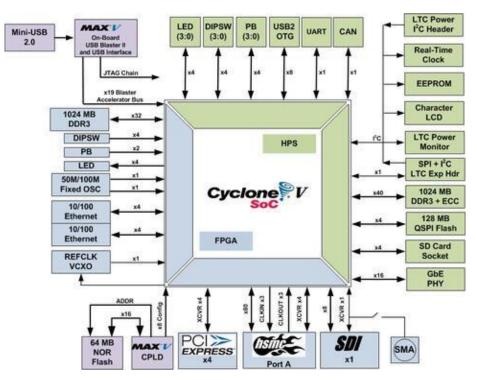

| 2.10.1 SOCs (CPU + FPGA)                                            | 95 |

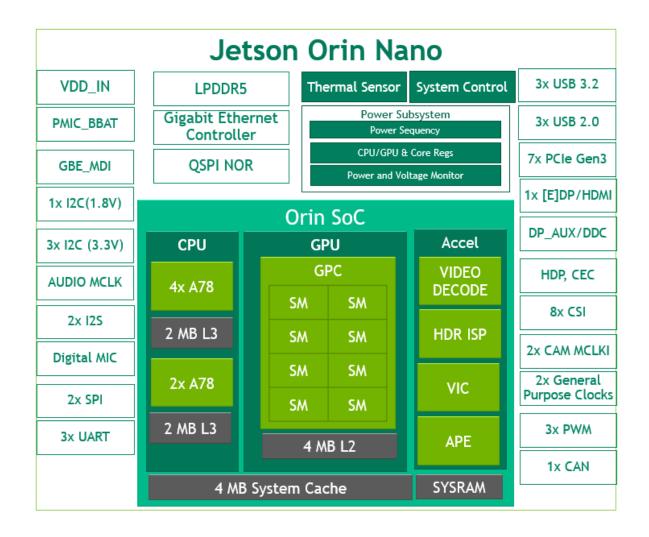

| 2.10.2 SOCs (CPU + GPU)                                             | 97 |

| 2.11 Physical package of integrated circuits                        | 98 |

| 2.12 Temperature ranges                                             |    |

| 3. Basic software bricks                                            |    |

| 3.1 Programming languages                                           |    |

| 3.2 Variables and constants                                         |    |

| 3.3. Operators                                                      |    |

| 4. Complexity                                                       |    |

|   | 4.1 Examples of algorithms and their complexities  | 109 |

|---|----------------------------------------------------|-----|

|   | 4.2 Rules in O-notation                            |     |

|   | 4.2.1 Product                                      | 111 |

|   | 4.2.2 Sum                                          | 111 |

|   | 4.2.3 Multiplication by a constant                 | 111 |

|   | 4.3 Other considerations involving Big-Oh notation | 112 |

|   | 4.4 Why does encryption (currently) work?          | 113 |

|   | 4.4.1 What is encryption?                          | 113 |

|   | 4.4.2 Symmetric-key cryptography                   | 114 |

|   | 4.4.3 Public-key cryptography                      | 119 |

| 5 | Mixed-signal application design                    | 120 |

|   | 5.1 Sensors for data acquisition                   | 121 |

|   | 5.2 Systems for data processing/storing            | 122 |

|   | 5.2.1 Embedded systems                             | 123 |

|   | 5.2.2 High-performance clusters                    | 125 |

|   | 5.2.3 Personal Computers / Small servers           | 125 |

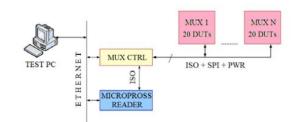

|   | 5.3 NVM cycling application design                 | 128 |

|   | 5.3.1 Problem description                          | 128 |

|   | 5.3.2. State of the art                            | 128 |

|   | 5.3.2 Specifications                               | 128 |

|   | 5.3.3 Estimations                                  | 128 |

|   | 5.3.4. Pseudocode for host                         |     |

|   | 5.3.5. Hardware design                             | 130 |

|   | 5.3.6. Software design                             | 131 |

|   | 5.3.7 Outcome                                      |     |

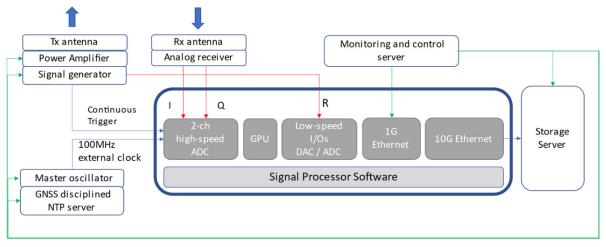

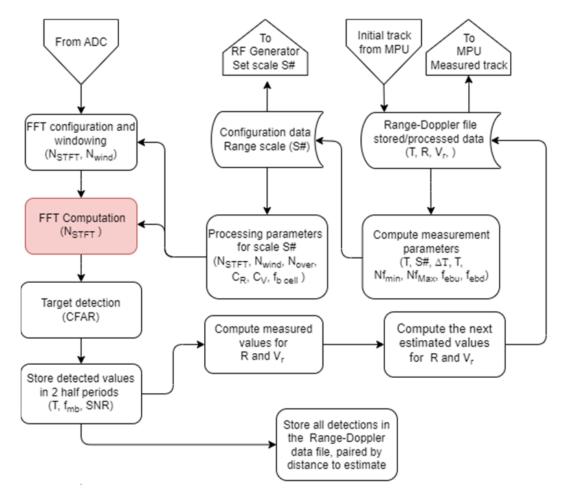

|   | 5.4 Digital signal processor for RADAR systems     | 132 |

|   | 5.4.1 Problem description                          | 132 |

|   | 5.4.2. State of the art                            | 134 |

|   | 5.4.3 Specifications                               | 134 |

|   | 5.4.4 Design /choice of the hardware               | 136 |

|   | 5.4.4 Design of the main software                  | 140 |

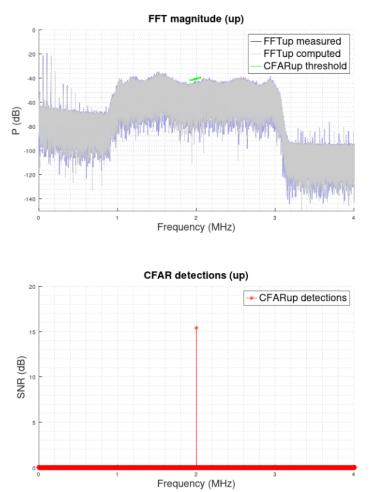

| 5.4.5 Implementation and test                                           | 140 |

|-------------------------------------------------------------------------|-----|

| 5.4.6 Conclusions                                                       | 141 |

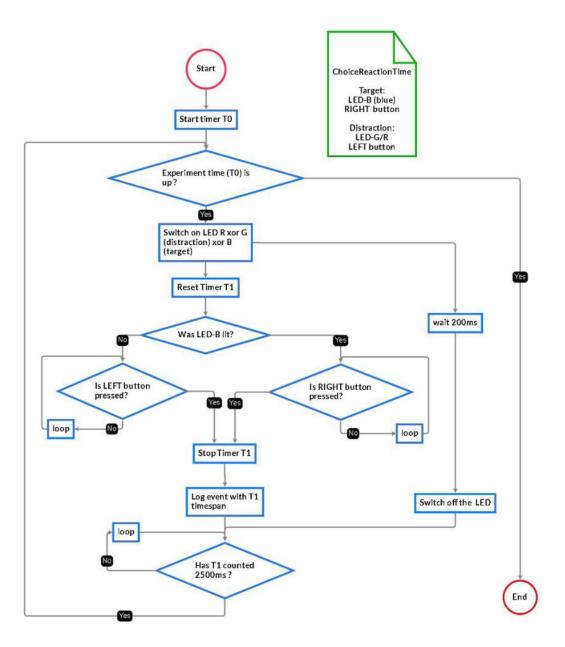

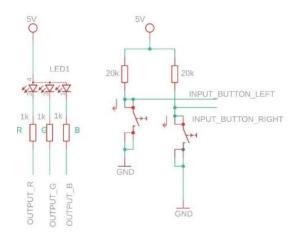

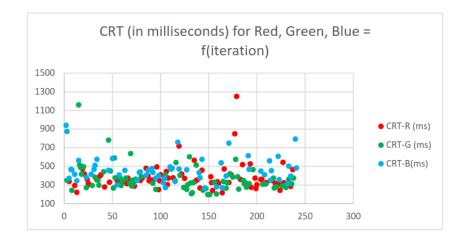

| 5.5 E-Health embedded system for choice reaction time (CRT) measurement | 142 |

| 6. Conclusions                                                          | 145 |

| Figure References                                                       | 146 |

| References                                                              | 154 |

## List of Figures

| Figure 1. A digital signal (as a result of both sampling and quantization processes)       | 19 |

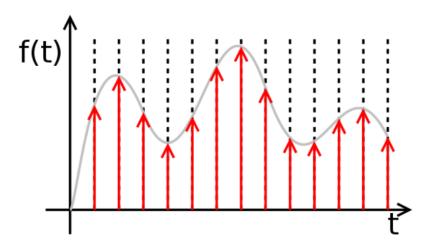

|--------------------------------------------------------------------------------------------|----|

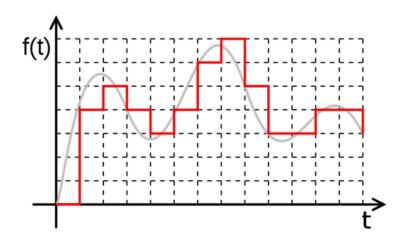

| Figure 2. A time-sampled signal (as a result of sampling process)                          | 20 |

| Figure 3. A value-sampled signal (as a result of quantization process)                     |    |

| Figure 4. AMD Athlon64 x2 CPU (left is top, right is bottom) with Socket 939               | 23 |

| Figure 5. 32GB DDR5-4800 RAM server memory with error correction code (ECC)                |    |

| Figure 6. RTX4090 GPU card with PCIexpress x16 slot, without passive and active coolin     |    |

| installed.                                                                                 | -  |

| Figure 7. A SATA-interfaced SSD (Solid State Disk) for non-volatile storage                | 25 |

| Figure 8. A PCIe-interfaced SSD for long term storage.                                     |    |

| Figure 9. A comparison between SLC, MLC, TLC and QLC cells                                 |    |

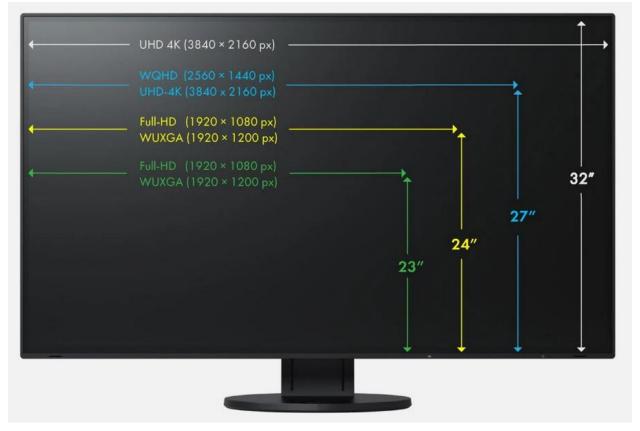

| Figure 10. A monitor with common pixel resolutions (HD = High definition).                 |    |

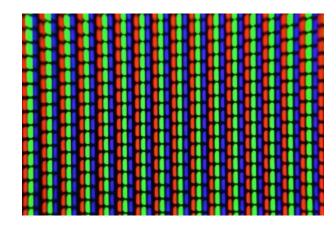

| Figure 11. RGB (red, green, blue) pixels in monitor image that spatially combine to obtair |    |

| all colors (white color is all RGB leds in that pixel lit)                                 | 27 |

| Figure 12. RAID0: high speed, no redundancy                                                | 28 |

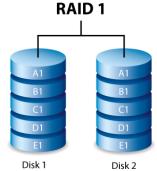

| Figure 13. RAID1 mode: data mirroring                                                      |    |

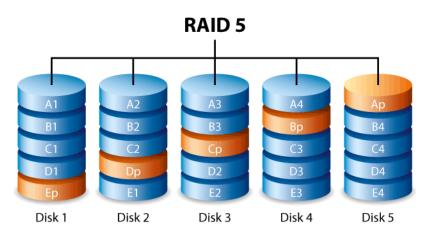

| Figure 14. RAID5 mode: single drive redundancy                                             | 29 |

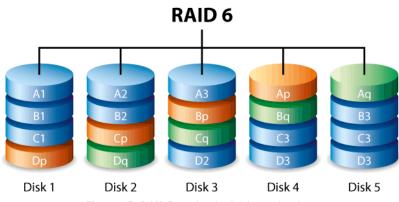

| Figure 15. RAID6 mode: dual drive redundancy                                               | 29 |

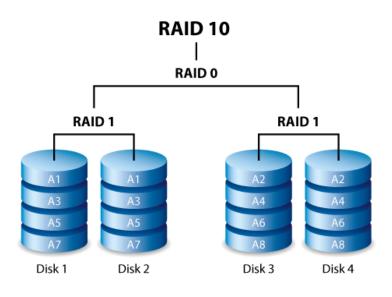

| Figure 16. RAID10: a RAID 0 of RAID1s                                                      | 30 |

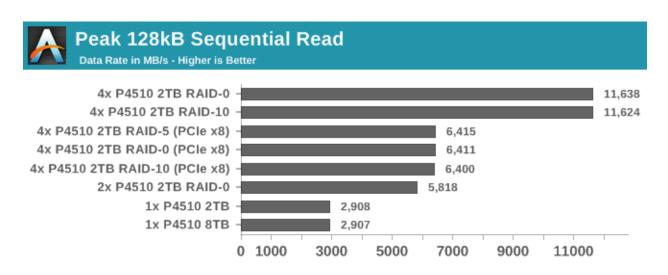

| Figure 17. Anandtech's comparison of Intel P4510 SSD (x4 PCIe) drives in various RAID      |    |

| configurations                                                                             | 30 |

| Figure 18. OSI layer model for networks                                                    | 31 |

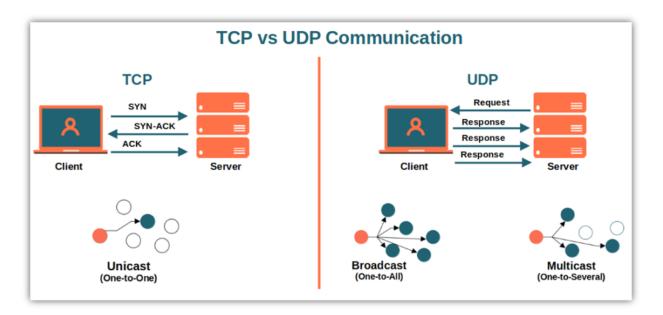

| Figure 19. TCP vs UDP in how data is transmitted an the possible types of connections      | 32 |

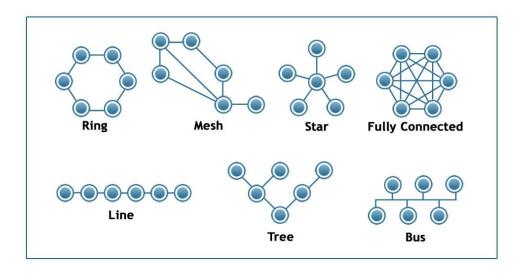

| Figure 20. Visual examples of network topologies                                           | 32 |

| Figure 21. Resolving a website's server address by using DNS hierarchy                     | 33 |

| Figure 22. Positive feedback loop (left). Negative feedback loop (right)                   | 34 |

| Figure 23. Operational amplifier (opamp)                                                   | 35 |

| Figure 24. Op-amps configured with diodes or resistors in their feedback loop to do:       |    |

| logarithmation, summation or product                                                       | 35 |

| Figure 25. NOT gate ("inverter") made of one pMOS (top) and one nMOS (bottom)              |    |

| transistor                                                                                 | 37 |

| Figure 26. ANSI / IEC [4] (right) and MIL-STD-806B [5] (left) symbols foremost common      |    |

| 7/16 dual-input logic gates (elementary), with their names                                 | 37 |

| Figure 27. The truth tables for the most commonly used logic gates                         | 38 |

| Figure 28. The 74HC00 circuit, a quad-input NAND circuit in DIP14 package                  | 38 |

| Figure 29. The 74HC04 circuit, a hex-inverter circuit in a 14-pin package (DIP14 or        |    |

| SOIC14)                                                                                    | 39 |

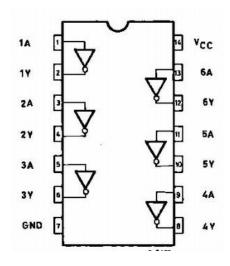

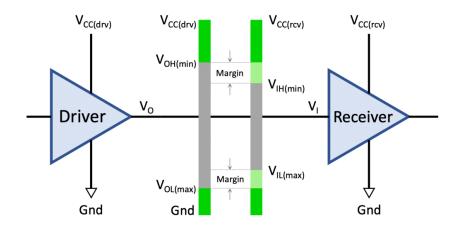

| Figure 30. Output requirements vs. input requirements                                      | 40 |

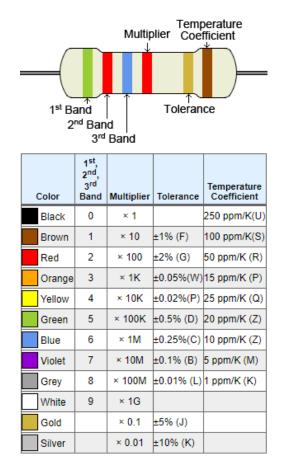

| Figure 31. Color-coded six-band THT resistor, and the table to decode it. Four bands are   |    |

| for resistance, one for tolerance and one for temperature coefficient                      | 41 |

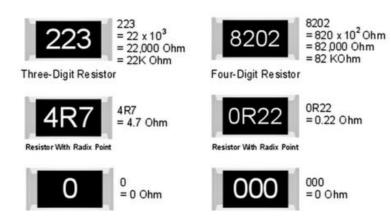

| Figure 32. Examples for SMD resistors of various resistance                               | .42 |

|-------------------------------------------------------------------------------------------|-----|

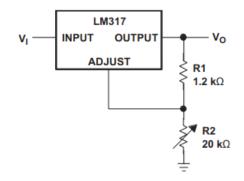

| Figure 33. LM317 adjustable regulator configuration via R2 variable resistor              | .43 |

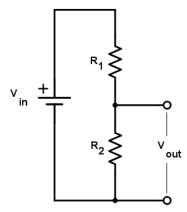

| Figure 34. Voltage divider                                                                |     |

| Figure 35. A 3.3 Ohm THT resistor manufactured to be able to disspate up to 100W          | .44 |

| Figure 36. Pictures of different types of resistors                                       | .44 |

| Figure 37. Various types of capacitors                                                    | 45  |

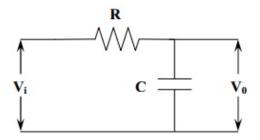

| Figure 38. The RC integrator. Vo increases to Vi after infinite time                      | 45  |

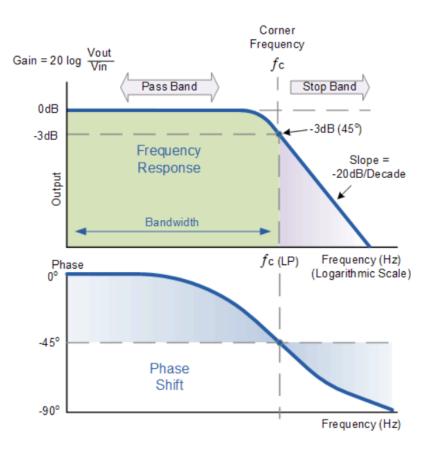

| Figure 39. RC low-pass filter Bode plots (for gain and phase)                             | .46 |

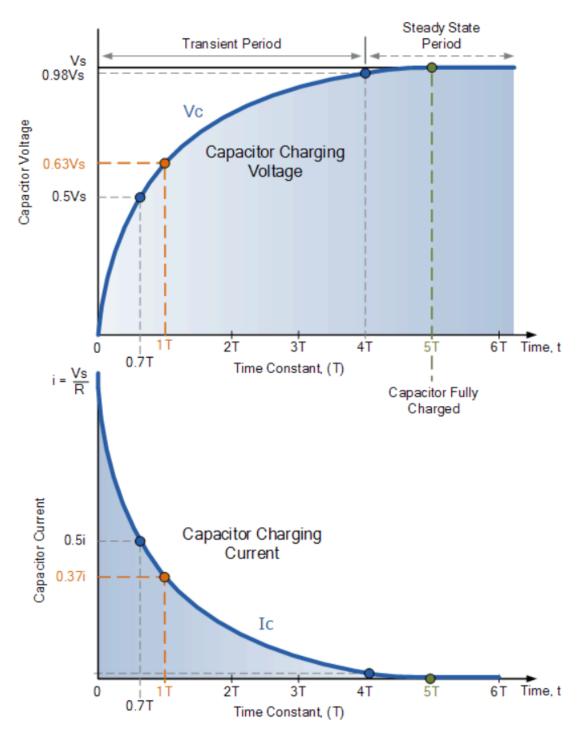

| Figure 40. The RC time constant in RC integrator circuit                                  | .47 |

| Figure 41. Various types of inductors                                                     | .48 |

| Figure 42. Various diodes formats and types                                               | .49 |

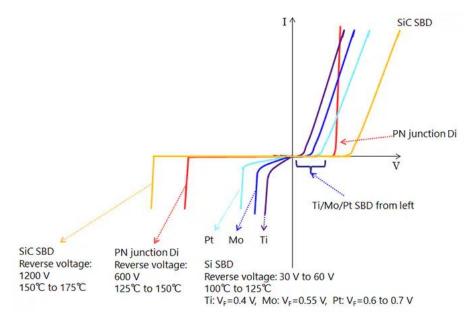

| Figure 43. U/I plot for various diodes with their reverse voltages and maximum temperate  |     |

|                                                                                           |     |

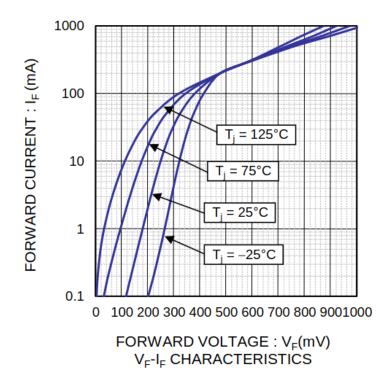

| Figure 44. The current as a function of forward voltage and temperature in RB451UM        |     |

| Schottky diode                                                                            | .50 |

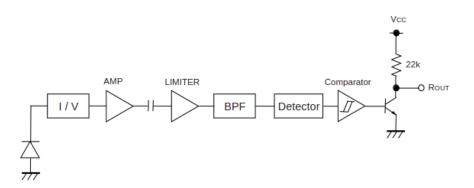

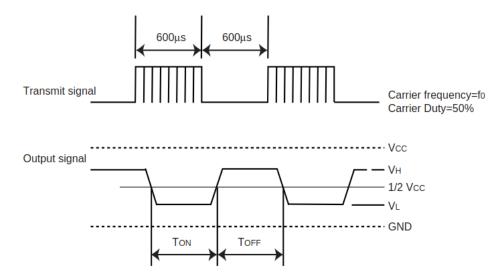

| Figure 45. The RPM7140 infrared receiver: internal block schematic: amplifier, limiter,   |     |

| band-pass filter, detector and comparator. Output is open collector with 22kOhm           |     |

| integrated pull-up resistor                                                               | 51  |

| Figure 46. The RPM7140's output signal (down) as reaction to input light (up)             | 51  |

| Figure 47. Various color temperatures and their equivalence in real-world                 | .52 |

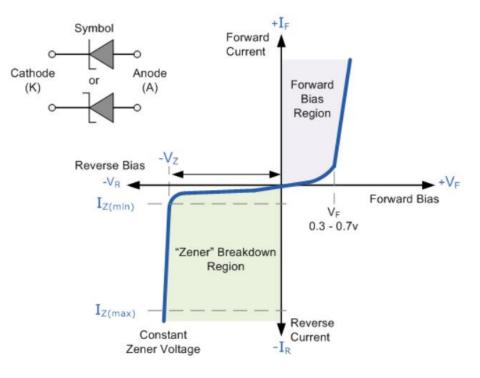

| Figure 48. Zener diode's operating regions                                                | 53  |

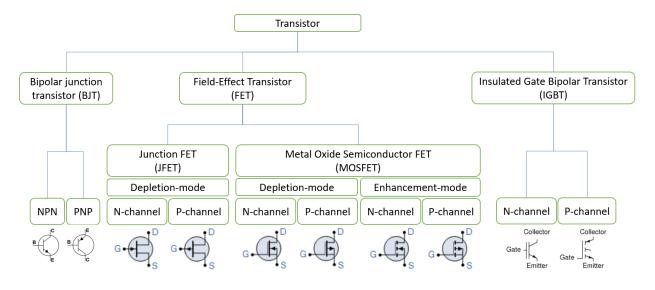

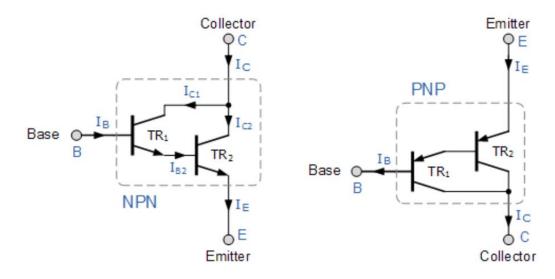

| Figure 49. Types of transistors                                                           | 54  |

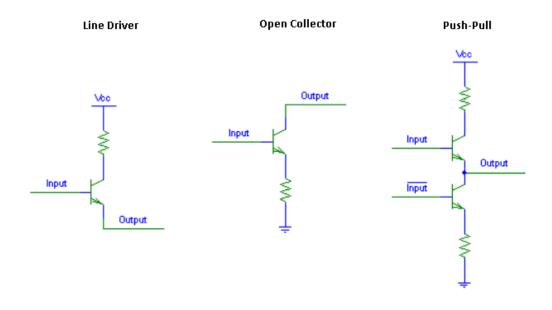

| Figure 50. Common usages for BJT: line driver, open-collector and push-pull               | 55  |

| Figure 51. Darlington transistors. The TR1 and TR2's amplification are multiplied         | 55  |

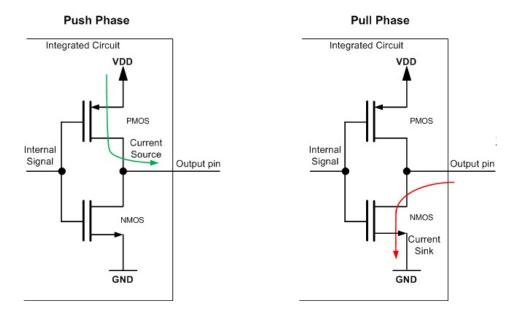

| Figure 52. Push-pull stage with FET transistors, usually found in output pads of          |     |

| microcontrollers                                                                          | 56  |

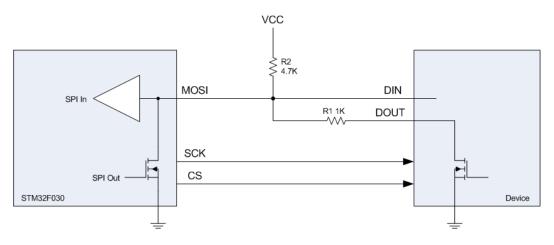

| Figure 53.Half-duplex communication between STM32 and another device                      | 56  |

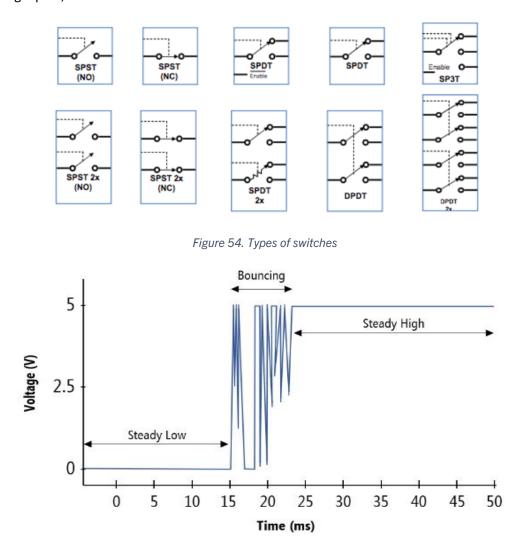

| Figure 54. Types of switches                                                              | 57  |

| Figure 55. Contact bouncing problem                                                       | 57  |

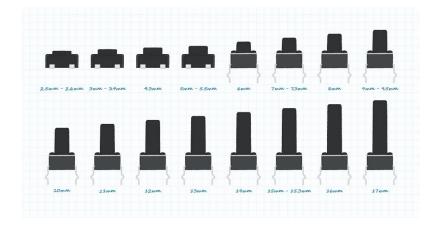

| Figure 56. Tactile switches, SMD (top left) or THT                                        | 58  |

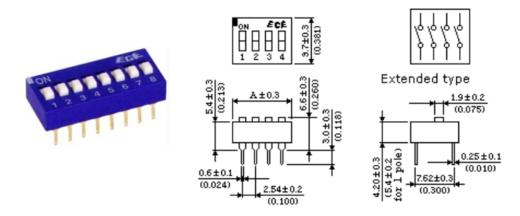

| Figure 57. Example of 8-slot DIP-switch                                                   | .58 |

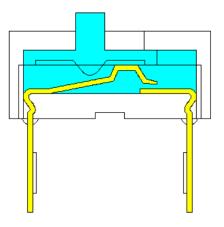

| Figure 58. Internal construction of a DIP switch                                          | 58  |

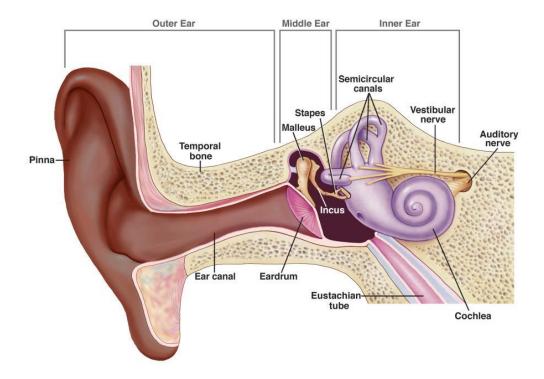

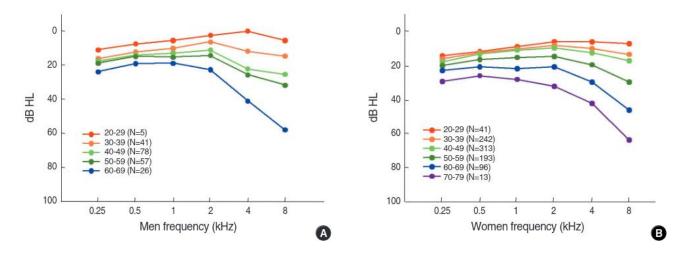

| Figure 59. Hearing for humans (source: NIH/NIDCD)                                         | .60 |

| Figure 60. Hearing loss in humans, depending on sex and age                               | .60 |

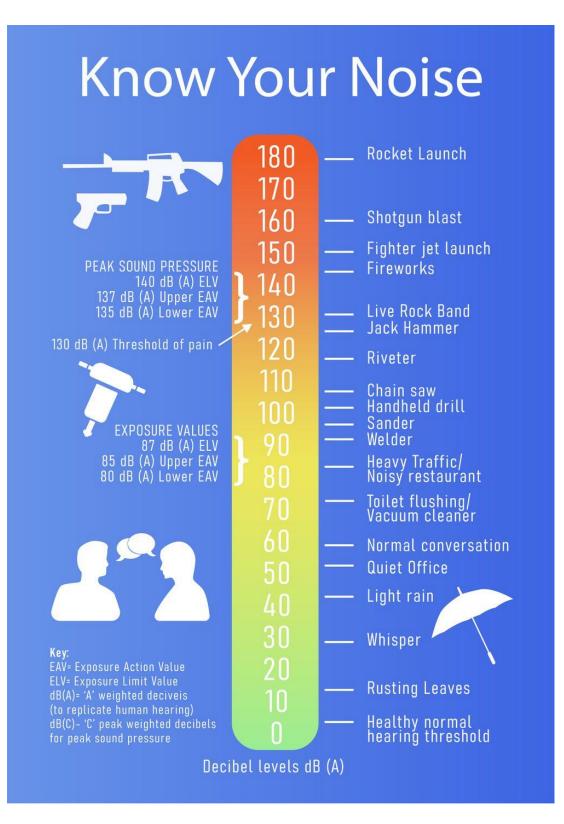

| Figure 61. Examples of noises a human may perceive                                        | 61  |

| Figure 62. Overview of dB key values and their conversion into power and voltage ratios . | .62 |

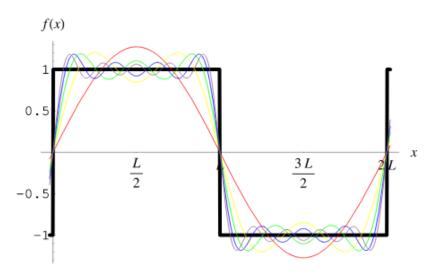

| Figure 63. The Fourier series of a function f(x)                                          |     |

| Figure 64. Decomposition of a square wave into first four terms of Fourier series         | .63 |

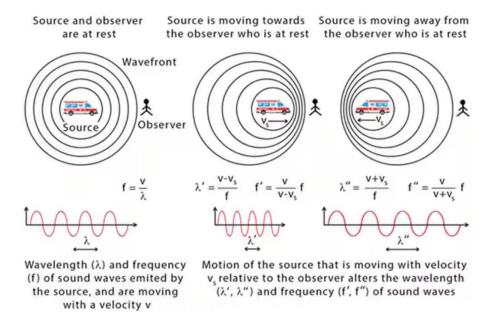

| Figure 65. Formula for observed frequency (in Doppler effect)                             |     |

| Figure 66. Doppler effect: as the source and observer move closer, the distance between     | n   |

|---------------------------------------------------------------------------------------------|-----|

| successive wave crests decreases, resulting in a rise in perceived frequency; the opposite  | Э   |

| is the case as the two move apart. (Science Facts)                                          | 64  |

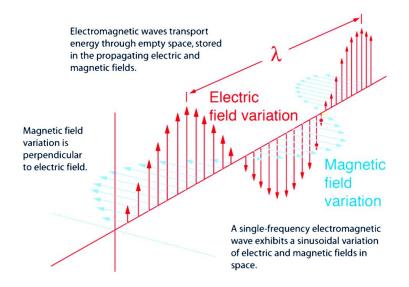

| Figure 67. The electromagnetic wave                                                         | 65  |

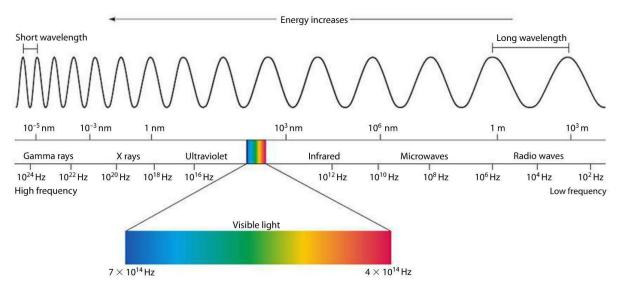

| Figure 68. The electromagnetic spectrum                                                     | 65  |

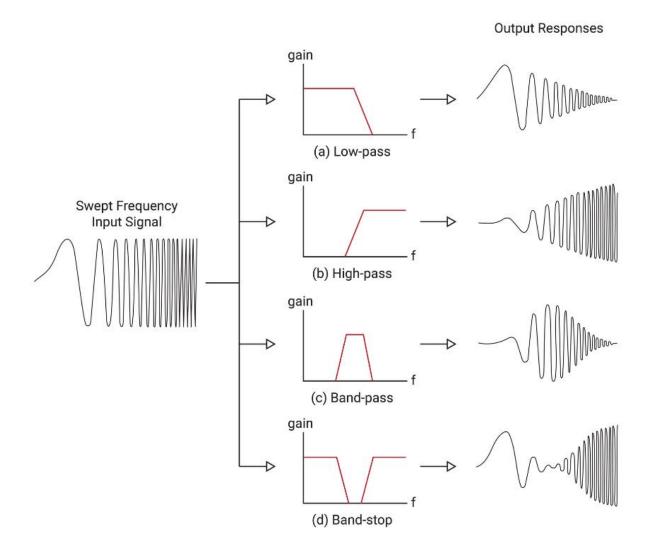

| Figure 69. Filter types and their responses                                                 |     |

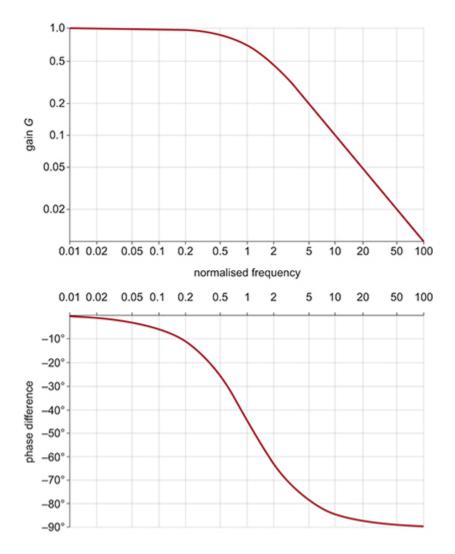

| Figure 70. First-order low-pass filter frequency response with gain and phase (Bode plots   |     |

|                                                                                             | 67  |

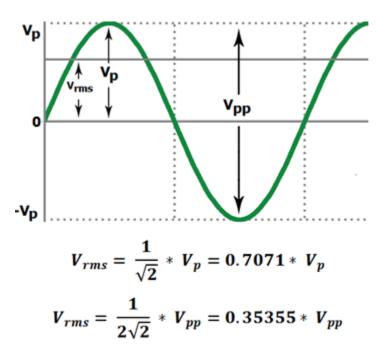

| Figure 71. The RMS value of X                                                               | 68  |

| Figure 72. The Vrms, Vpeak and Vpeak-to-peak values of a sine AC voltage                    | 68  |

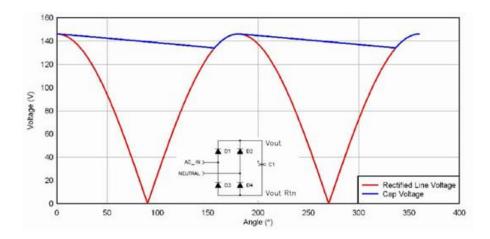

| Figure 73. A full wave AC rectifier                                                         | 69  |

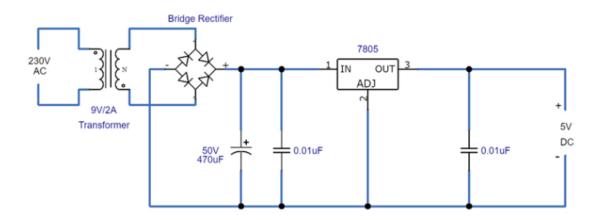

| Figure 74. 230VAC-to-5V, transformer-based power supply based on a 7805 IC                  | 69  |

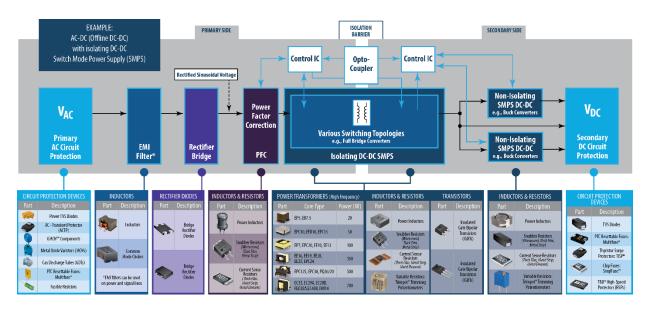

| Figure 75. Schematic of a modern PSU with possible component selection                      | 70  |

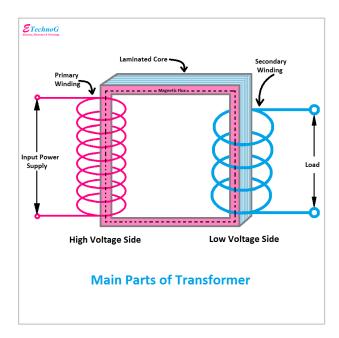

| Figure 76. Step-down AC transformer                                                         | 70  |

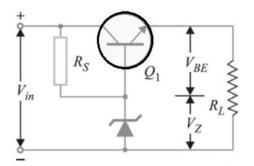

| Figure 77. Series-voltage regulator based on a transistor and Zener diode                   | 71  |

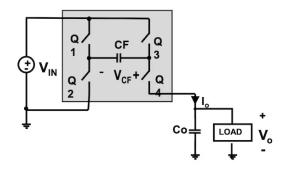

| Figure 78. The voltage doubler                                                              | 72  |

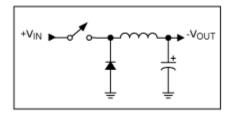

| Figure 79. The buck converter topology                                                      | 72  |

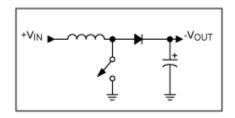

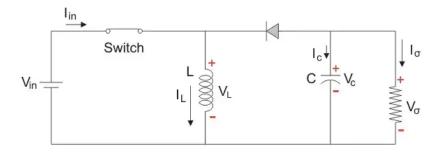

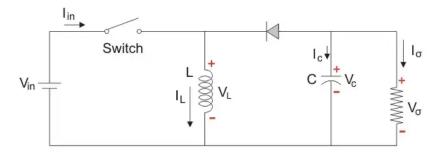

| Figure 80. The boost converter topology                                                     | 73  |

| Figure 81. Buckboost in charging stage                                                      | 73  |

| Figure 82. Buckboost in discharging stage                                                   | 73  |

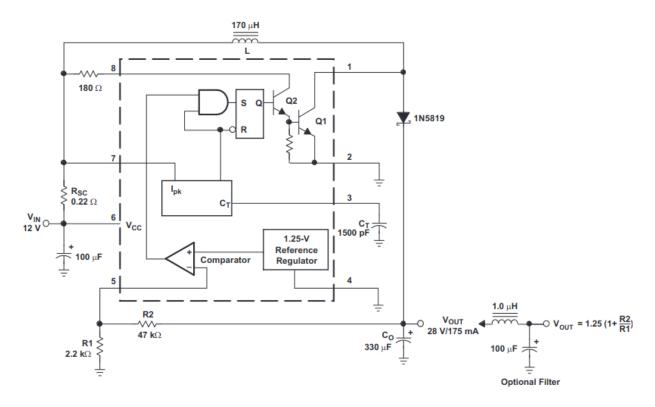

| Figure 83. Typical MC34063 usage as step-up converter. Additional output filters may be     | Э   |

| added to smooth the output                                                                  | 74  |

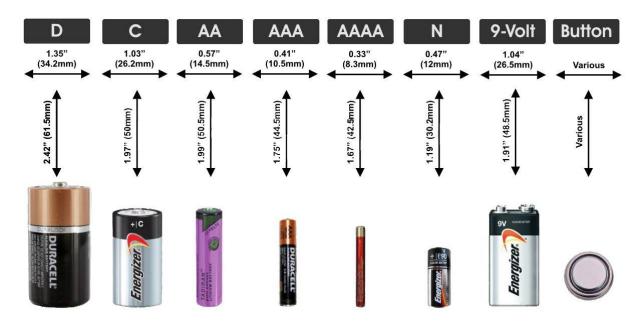

| Figure 84. GP's selection guide for cylindrical primary battery types                       | 75  |

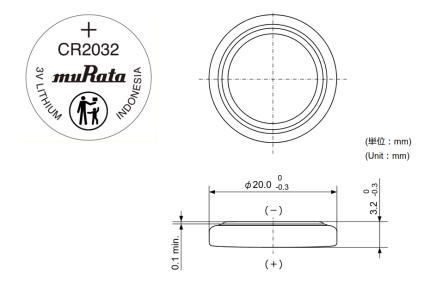

| Figure 85. CR2032 coin cell BIOS-backing battery, having 20 mm diameter and 3.2 mm          |     |

| thickness                                                                                   | 75  |

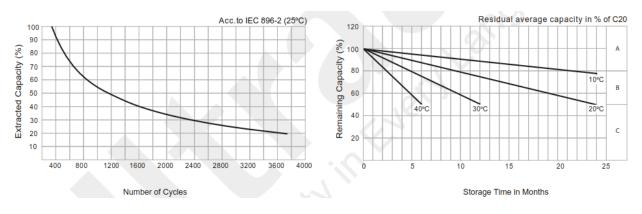

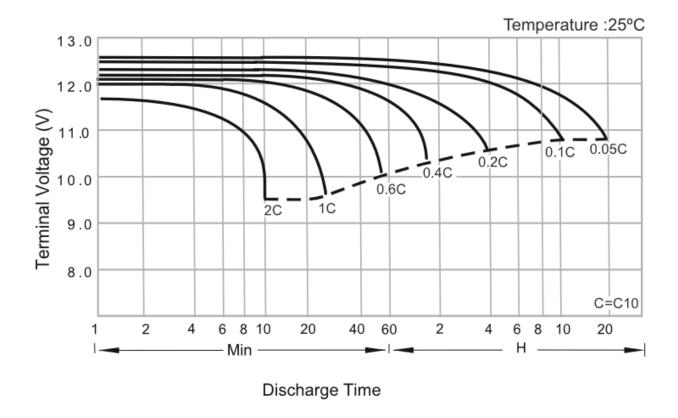

| Figure 86. Cycle life vs depth of discharge (left). Storage time vs temperature             | 77  |

| Figure 87. Effect of discharge current, on capacity in UCG100-12 lead-acid battery          | 77  |

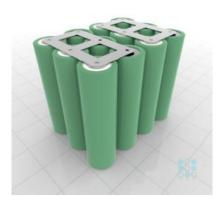

| Figure 88. 4S3P pack. Note the white top part and the grey top part                         | 78  |

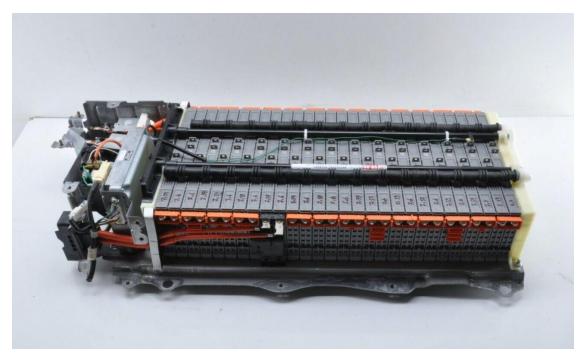

| Figure 89. Toyota Prius 2 Hybrid battery: 28 modules of 6 cells each having 1.2V and        |     |

| 6.5Ah NiMH. Total voltage: 28*6*1.2 = 201.6 V nominal. Total pack energy: 201.6 V * 6.5     | 5   |

| Ah = 1.3 kWh.                                                                               | 78  |

| Figure 90. Snapshot of Dr. Prius app, which reads voltages across all 14 battery packs of   |     |

| Prius 3, in order to diagnose "bad" cells                                                   | 79  |

| Figure 91. Very common laptop-battery element (li-Ion 18650 format)                         | 79  |

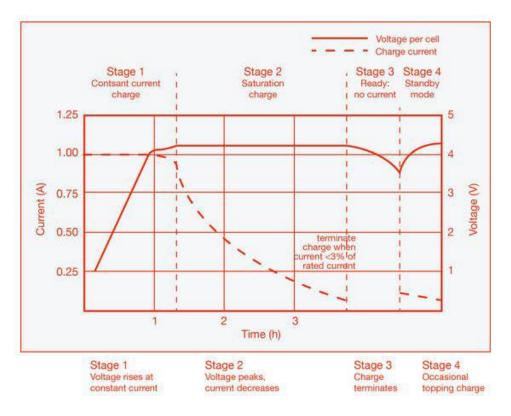

| Figure 92. A typical algorithm for charging Li-Ion batteries. Constant current, then consta | ant |

| voltage                                                                                     | 80  |

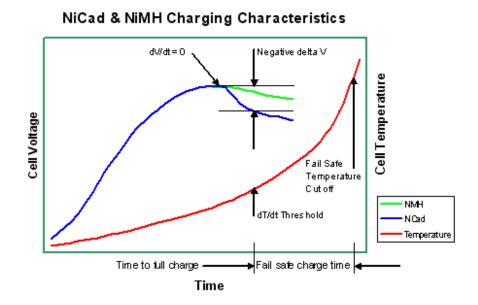

| Figure 93. NiCd and NiMH dv/dt and dT/dt marking the end of charge                          | 80  |

| Figure 94. Common physical formats for batteries                                            | 81  |

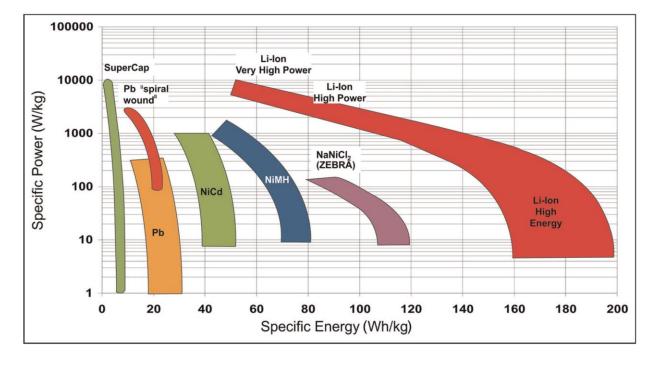

| Figure 95. Summary for specific energy and specific power across all common battery         |     |

| chemistries                                                                                 | 81  |

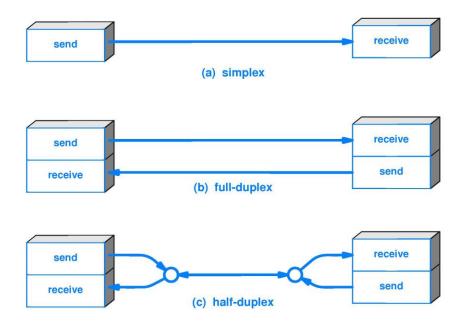

| Figure 96. Data transmission types                                                          | 82  |

| Figure 97. Parallel vs Serial interfaces                                                    | 83  |

|---------------------------------------------------------------------------------------------|-----|

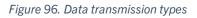

| Figure 98. Example of a SPI communication (8-bit per frame)                                 | 83  |

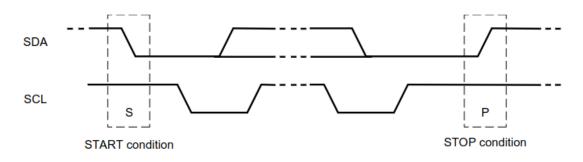

| Figure 99. START and STOP conditions on I2C bus                                             | 85  |

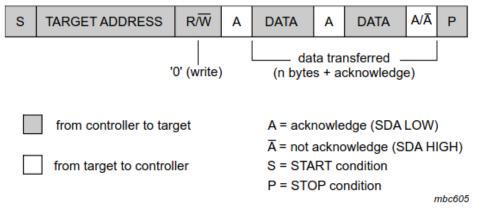

| Figure 100 Master sends data to slave (write frame) with 7-bit address                      | 85  |

| Figure 101. Master reads data from slave, with 7-bit address (read frame)                   | 86  |

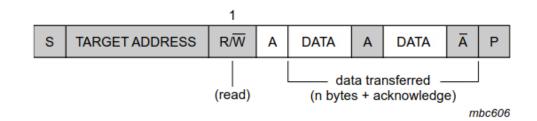

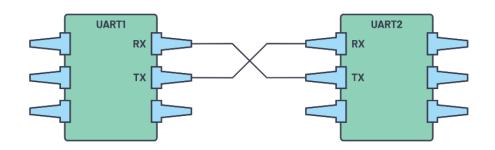

| Figure 102. Two partners exchanging data over a full-duplex UART bus. GND is tied           |     |

| together, but not shown                                                                     | 87  |

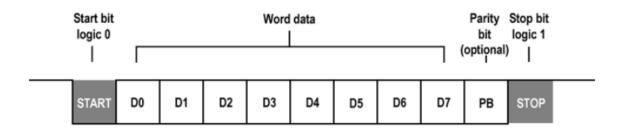

| Figure 103. UART data frame                                                                 | 87  |

| Figure 104. A UART data frame with START bit, 8 data bits, one parity bit and STOP bit.     | 87  |

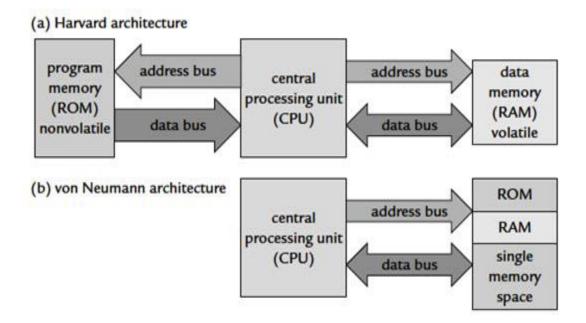

| Figure 105. Von Neumann and Harvard Architectures                                           | 88  |

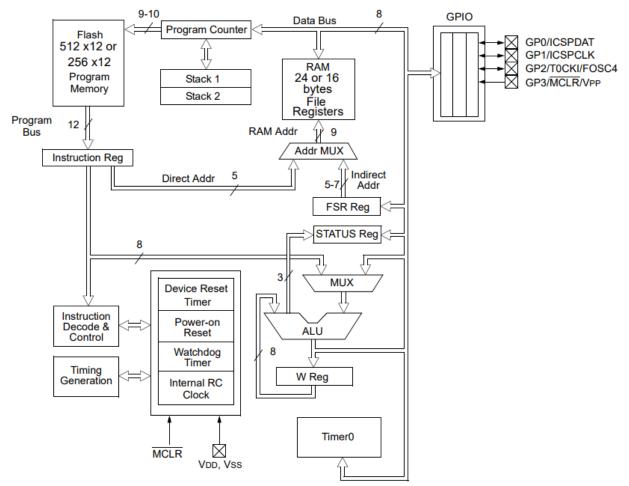

| Figure 106. PIC10F2xx internal block diagram                                                |     |

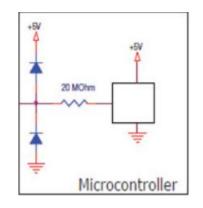

| Figure 107. Clamping diodes protect the I/O on the left                                     | 90  |

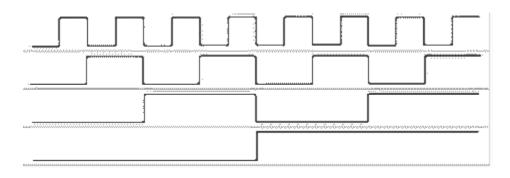

| Figure 108. Prescaler input (top), and output for 1:2, 1:4 or 1:8 setting                   | 90  |

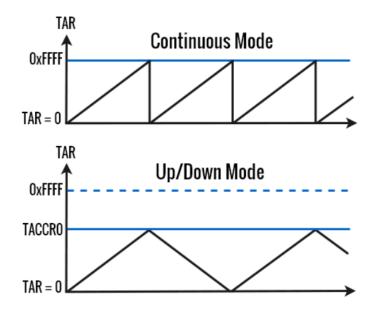

| Figure 109. MSP430 MCU timer modes of operation                                             | 91  |

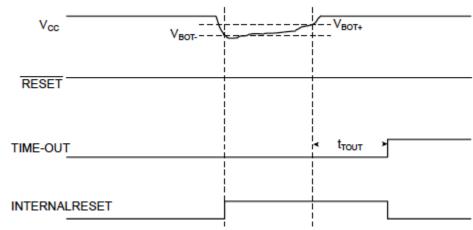

| Figure 110. Brown-out detector scenario                                                     |     |

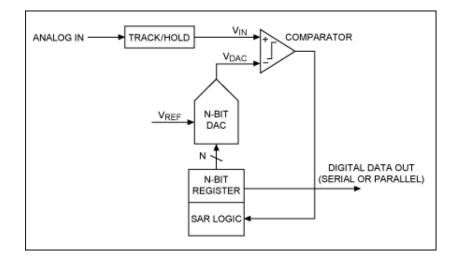

| Figure 111 N-bit SAR ADC architecture                                                       |     |

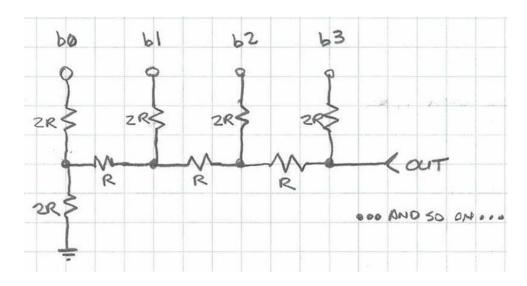

| Figure 112 R2R DAC architecture                                                             |     |

| Figure 113. AMD/Xilinx Zynq 7000 SoC chip family                                            |     |

| Figure 114. Intel/Altera Cyclone V SoC                                                      | 96  |

| Figure 115. NVIDIA Jetson Nano SoC                                                          | 97  |

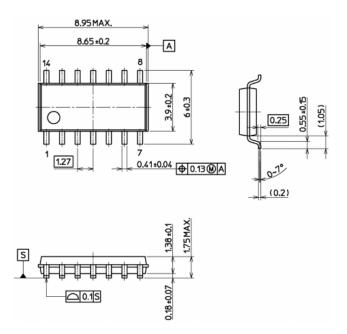

| Figure 116. SOIC-14-N (narrow) package, having P (pin-to-pin distance) of 1.27mm (tha       | t   |

| is 0.05 inch, or 50 mils)                                                                   |     |

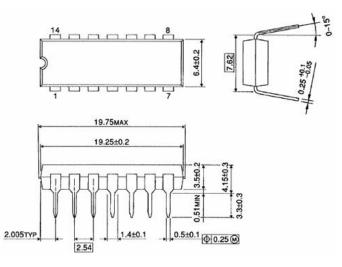

| Figure 117. DIP14 package, having pin-to-pin distance of 2.54 mm (0.1 inch)                 |     |

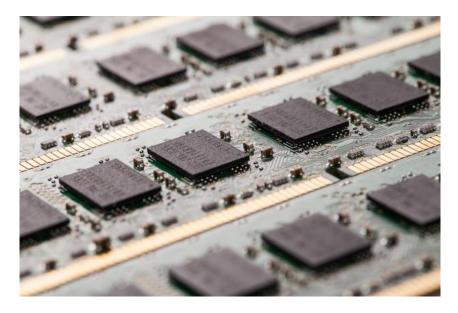

| Figure 118. A PCB (printed circuit board) with multiple SMD components                      |     |

| Figure 119. A PCB with SMD capacitors                                                       |     |

| Figure 120. A PCB with multiple components in THT (diodes, resistors, ICs)1                 |     |

| Figure 121. A 3D rendering of a simplified PC motherboard                                   |     |

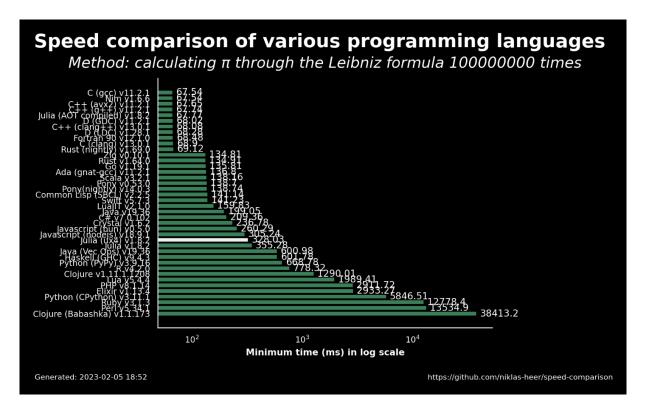

| Figure 122. A comparison of speed of intensive computation across multiple languages.       |     |

| C/C++ is fastest when compiled with optimizing compiler (gcc) 1                             | .04 |

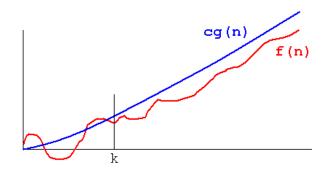

| Figure 123. Representing a g(n) function which asymptotically dominate f(n) function1       |     |

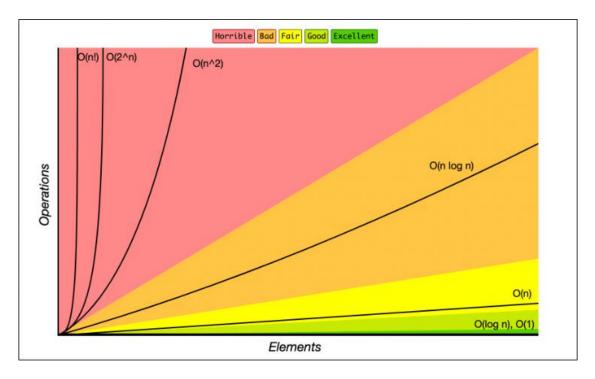

| Figure 124. The O-notation complexity increase with the number of elements processed.       |     |

| O(1) and O(logn) are usually excellent complexities, O(n) is fair, and O(n*logn) is usually |     |

| considered almost decent in algorithms and circuits1                                        |     |

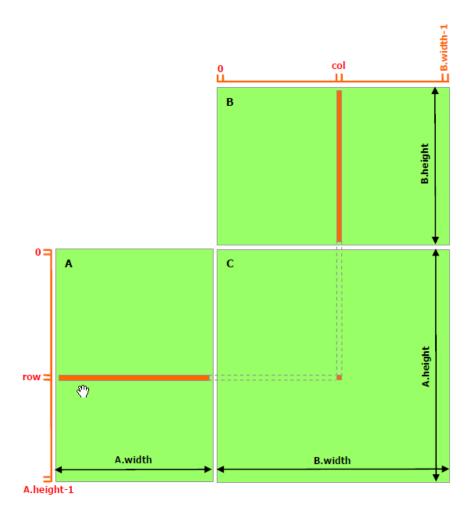

| Figure 125. Matrix-matrix multiplication (naïve-approach)1                                  |     |

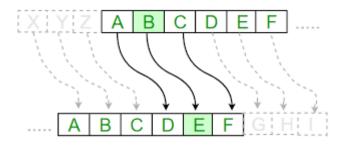

| Figure 126. Caesar cipher exemplified, for a distance of 31                                 |     |

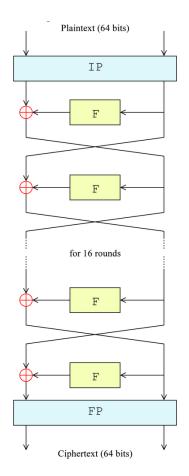

| Figure 127. DES encryption where F is a Feistel one-way function1                           |     |

| Figure 128. One round of DES encryption, Sx are the 6-bit to 4-bit substitution boxes 1     | .15 |

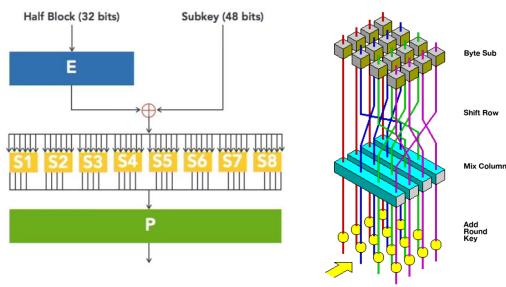

| Figure 129. One AES round, expressed graphically in 3D1                                     |     |

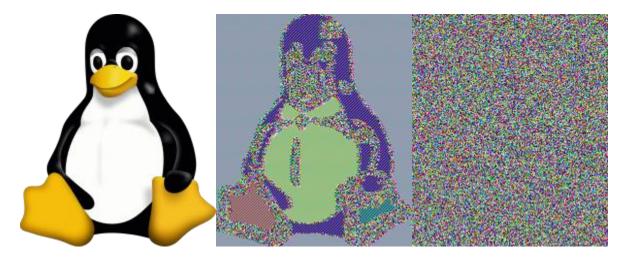

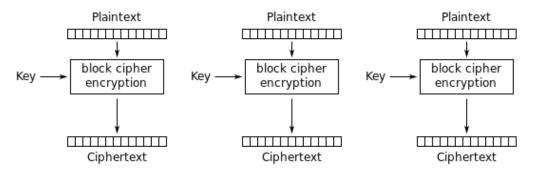

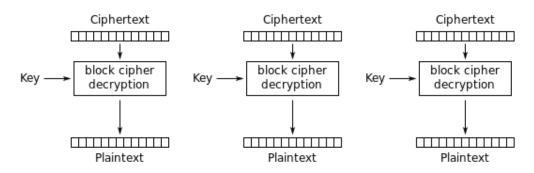

| Figure 130. Left is the original image, middle is ECB mode cryptotext and right is CTR1     | .16 |

| Figure 131. Top is ECB encryption and bottom is ECB description: great for parallel         |     |

| processing but very weak in hiding data1                                                    | .17 |

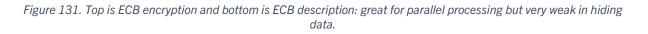

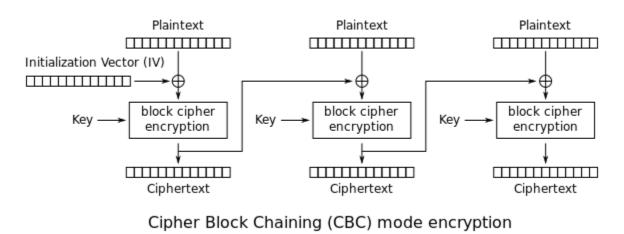

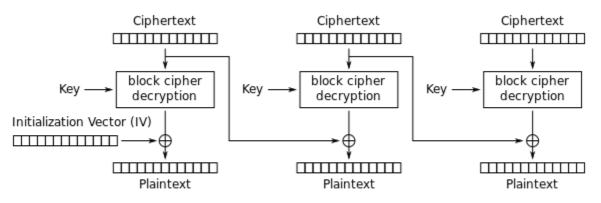

| Figure 132. Top is CBC encryption and bottom is CBC decryption. CBC is hard to     |     |

|------------------------------------------------------------------------------------|-----|

| parallelize in encryption, but it is suitable for parallel decryption              | 118 |

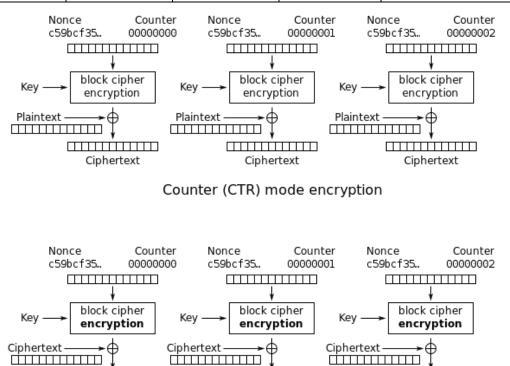

| Figure 133. CTR mode encryption (top) and decryption (bottom).                     | 119 |

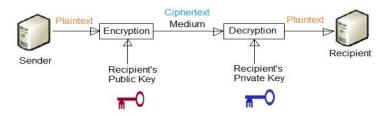

| Figure 134 Public-key cryptography (encryption and decryption)                     | 120 |

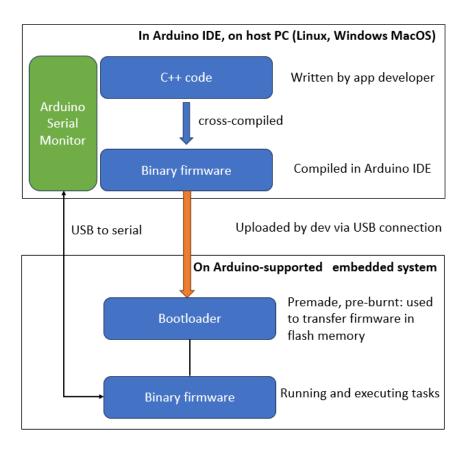

| Figure 135 Arduino environment for developing apps                                 | 121 |

| Figure 136 Synology DS223j NAS unit                                                | 123 |

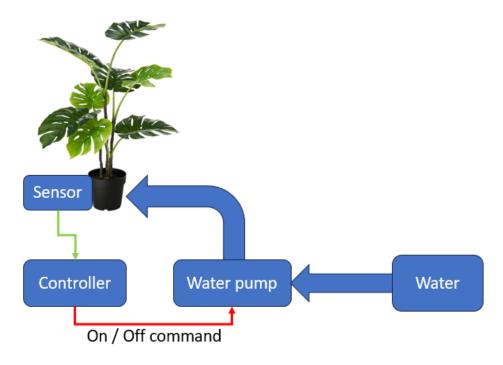

| Figure 137. Automatic plant watering system                                        | 124 |

| Figure 138. A cluster organized in cooled racks                                    | 125 |

| Figure 139. Examples of various-sized 19"racks                                     | 126 |

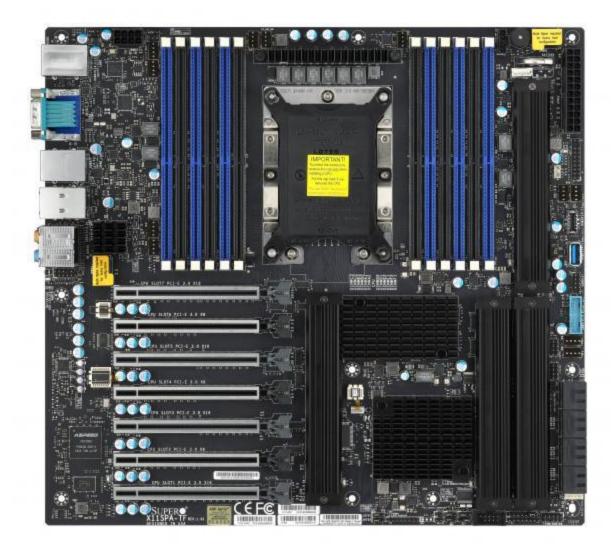

| Figure 140 The Supermicro X11SPA-T motherboard                                     | 127 |

| Figure 141. Host-side pseudocode                                                   | 129 |

| Figure 142. Votsch temperature test chamber                                        | 130 |

| Figure 143. The finished hardware test setup                                       | 130 |

| Figure 144. Block schematic of the system                                          | 131 |

| Figure 145. Common orbits around Earth                                             | 132 |

| Figure 146. Cheia1 RADAR's antenna (32 meters wide, 309 tons of weight)            | 133 |

| Figure 147. System schematic of the RADAR                                          | 135 |

| Figure 148. The FSM of the signal processor                                        | 140 |

| Figure 149. Data processed in SP compared against Octave (top). Peak detection aft | er  |

| CFAR (bottom)                                                                      | 141 |

| Figure 150. FSM of the CRT system (without data sending)                           | 143 |

| Figure 151. CRT equivalent electrical schematic                                    | 144 |

| Figure 152. CRT (ms) for each color as function of iteration                       | 144 |

## List of Tables

| Table 1. Multiples of bits / bytes according to JEDEC [1]. IEC 80000-13 standard char     | iges |

|-------------------------------------------------------------------------------------------|------|

| the name for the power of two, by inserting a "bi" in the name: Kibibyte, Mebibyte,       |      |

| Gibibyte                                                                                  | 21   |

| Table 2. Common RAID modes and their minimum requirements                                 | 27   |

| Table 3. Comparison between positive and negative feedback in electronics                 | 34   |

| Table 4. A (general) logic operation's truth table                                        | 36   |

| Table 5. Truth tables for AND, OR and NOT operations                                      | 36   |

| Table 6. Truth tables for AND, OR and NOT operations (seen as 1-bit operations)           | 36   |

| Table 7. A few common 74HC integrated circuits                                            | 39   |

| Table 8. Common packages for 16-pin IC 74HC595                                            | 40   |

| Table 9. Recommended operating conditions for 54HC595 / 74HC595 ICs                       | 40   |

| Table 10. Decoding table depending on number of bands painted on THT resistors            |      |

| Table 11. The impact of time in the evolution of capacitor voltage, in RC integrator circ |      |

| Table 12. LED color depending on wavelength and chemistry for Kingbright KPA-2107         |      |

| KA-3021SYCKT* /F3** LED                                                                   |      |

| Table 13. Types of white light (by color temperature)                                     |      |

| Table 14. Regions of operation for BJT transistors                                        |      |

| Table 15. Explanation of BJT regions                                                      |      |

| Table 16. Other types of decibels (dB)                                                    |      |

| Table 17. I2C protocol speeds                                                             |      |

| Table 18. 4-bit R2R DAC output                                                            | 93   |

| Table 19. Temperature ranges                                                              | 101  |

| Table 20. Hello world written in C and C++ language                                       | 103  |

| Table 21. Hello world written in C# and Java language                                     | 104  |

| Table 22. Hello world written in JavaScript and Python language                           | 104  |

| Table 23. Most common variable types in C/C++ languages                                   | 105  |

| Table 24. TIOBE index [13] for programming languages                                      | 106  |

| Table 25. Common operators in languages                                                   |      |

| Table 26. An example of algorithm complexity impact on running time, as a function o      |      |

| data size (green)                                                                         | 111  |

| Table 27. Block ciphers mode of operation with their attributes regarding parallel        |      |

| processing and strength                                                                   |      |

| Table 28. Planned (by design) scales for the RADAR                                        |      |

| Table 29. FFT measurements in CPU and GPU setups                                          |      |

| Table 30. Benchmarking all operations for 2M samples in CPU and GPU setups                | 139  |

## List of Acronyms

| AACS                                  | Advanced Access Content System                                                       |

|---------------------------------------|--------------------------------------------------------------------------------------|

| AC                                    | Alternative Current                                                                  |

| AC                                    | Akemative current                                                                    |

| ACK                                   | Acknowledge<br>Analog to digital converter                                           |

| ADC                                   |                                                                                      |

|                                       | Advanced Encryption Standard                                                         |

| AGM                                   | Absorbent Glass Mat                                                                  |

| AMD                                   | Advanced Micro Devices                                                               |

| ANSI                                  | American National Standards Institute                                                |

| ARPA                                  | Advanced Research Projects Agency                                                    |

| ARPANET                               | Advanced Research Projects Agency Network                                            |

| ASIC                                  | Application Specific Integrated Circuit                                              |

| BIOS                                  | Basic Input-Output System                                                            |

| BJT                                   | Bipolar Junction Transistor                                                          |

| BOD                                   | Brown-out detect                                                                     |

| CBC                                   | Cipher Block Chaining                                                                |

| CD                                    | Compact Disk                                                                         |

| CDIP                                  | Ceramic Dual Inline Package                                                          |

| CERN                                  | Conseil Européen pour la Recherche Nucléaire / European Council for Nuclear Research |

| CFB                                   | Cipher Feedback Mode                                                                 |

| CMOS                                  | Complementary Metal-Oxide Semiconductor                                              |

| COBOL                                 | Common Business-Oriented Language                                                    |

| СРНА                                  | Clock Phase                                                                          |

| CPOL                                  | Clock Polarity                                                                       |

| CPU                                   | Central Processing Unit                                                              |

| CRT                                   | Cathode-Ray Tube                                                                     |

| CS                                    | Chip Select                                                                          |

| CSNET                                 | Computer Science Network                                                             |

| CTFT                                  | Continuous Time Fourier Transform                                                    |

| CTR                                   | Counter                                                                              |

| CUDA                                  | Compute Unified Device Architecture                                                  |

| CV                                    | Computer Vision                                                                      |

| DAC                                   | Digital to Analog Converter                                                          |

| DC                                    | Direct Current                                                                       |

| DDR                                   | Double Data Rate                                                                     |

| DES                                   | Data Encryption Standard                                                             |

| DHCP                                  | Dynamic Host Configuration Protocol                                                  |

| DIP                                   | Dual In-line Package                                                                 |

| DNA                                   | Deoxyribonucleic Acid                                                                |

| DNS                                   | Domain Name Service                                                                  |

| · · · · · · · · · · · · · · · · · · · |                                                                                      |

| DRAM  | Dynamic Random Access Memory                                    |

|-------|-----------------------------------------------------------------|

| DUT   | Device Under Test                                               |

| EB    | Exabyte                                                         |

| ECB   | Electronic Code Book                                            |

| ECC   | Error Correction Code                                           |

| EMES  | Engineering of Modern Electric Systems                          |

| FET   | Field-Effect Transistor                                         |

| FIFO  | First-In First-Out                                              |

| FIPS  | Federal Information Processing Standard                         |

| FM    | Frequency Modulation                                            |

| FTP   | File Transfer Protocol                                          |

| GB    | Gigabyte                                                        |

| GHz   | Gigahertz                                                       |

| GND   | Ground                                                          |

| GP    | General Purpose                                                 |

| GPIO  | General Purpose Input/Output                                    |

| GPU   | Graphical Processing Unit                                       |

| GUI   | Graphical User Interface                                        |

| HD    | High Definition                                                 |

| HDD   | Hard Disk Drive                                                 |

| HDL   | Hardware Description Language                                   |

| HTML  | Hypertext Markup Language                                       |

| I2C   | Inter-integrated circuit                                        |

| IC    | Integrated circuit                                              |

| ICPSC | International Conference on Signal Processing and Communication |

| IDE   | Integrated development environment                              |

| IEC   | International Electrotechnical Commission                       |

| IEEE  | Institute of Electrical and Electronics Engineers               |

| IIC   | Inter-integrated circuit                                        |

| IOP   | I/O operation                                                   |

| IP    | Internet Protocol                                               |

| IPMI  | Intelligent Platform Management Interface                       |

| IR    | Infrared                                                        |

| ISO   | International Organization for Standardization                  |

| JBOD  | Just a Bunch of Disks                                           |

| JEDEC | Joint Electron Device Engineering Council                       |

| JS    | JavaScript                                                      |

| KB    | Kilobyte                                                        |

| kHz   | Kilohertz                                                       |

| LAN   | Local Area Network                                              |

| LASER | Light Amplification by Stimulated Emission of Radiation         |

| LCCC    | Leaded Chip Carrier ceramic                    |  |  |  |  |

|---------|------------------------------------------------|--|--|--|--|

| LED     | Light-emitting diode                           |  |  |  |  |

| LIDAR   | Light Detection and Ranging                    |  |  |  |  |

| LSB     | Least Significant Bit/Byte                     |  |  |  |  |

| MATLAB  | Matrix Laboratory                              |  |  |  |  |

| MB      | Megabyte                                       |  |  |  |  |

| MCU     | Microcontroller Unit                           |  |  |  |  |

| MHz     | Megahertz                                      |  |  |  |  |

| MIL-STD | Military Standard                              |  |  |  |  |

| MISO    | Master In Slave Out                            |  |  |  |  |

| MIT     | Massachusetts Institute of Technology          |  |  |  |  |

| MOhm    | Megohm                                         |  |  |  |  |

| MOS     | Metal-Oxide Semiconductor                      |  |  |  |  |

| MOSI    | Master Out Slave In                            |  |  |  |  |

| MSB     | Most Significand Bit/Byte                      |  |  |  |  |

| MW      | Megawatt                                       |  |  |  |  |

| NACK    | Not Acknowledge                                |  |  |  |  |

| NAND    | Not AND                                        |  |  |  |  |

| NAS     | Network-Attached Storage                       |  |  |  |  |

| NC      | Normal Closed                                  |  |  |  |  |

| NI      | National Instruments                           |  |  |  |  |

| NIC     | Network Interface Card                         |  |  |  |  |

| NIH     | National Institute of Health                   |  |  |  |  |

| NIMH    | Nickel-metal hydride (battery)                 |  |  |  |  |

| NIST    | National Institute of Standards and Technology |  |  |  |  |

| NO      | Normal Open                                    |  |  |  |  |

| NOM     | Nominal                                        |  |  |  |  |

| NOR     | Not OR                                         |  |  |  |  |

| NP      | Non-polynomial                                 |  |  |  |  |

| NSF     | National Science Foundation                    |  |  |  |  |

| NTC     | Negative Temperature Coefficient               |  |  |  |  |

| NTP     | Network Time Protocol                          |  |  |  |  |

| NVM     | Non-Volatile Memory                            |  |  |  |  |

| OFB     | Output Feedback Mode                           |  |  |  |  |

| OOK     | On/Off Keying                                  |  |  |  |  |

| OP      | Operation                                      |  |  |  |  |

| OSI     | Open Systems Interconnection Model             |  |  |  |  |

| OTP     | One Time Password                              |  |  |  |  |

| OUT     | Output                                         |  |  |  |  |

| PB      | Petabyte                                       |  |  |  |  |

| PC      | Personal Computer                              |  |  |  |  |

| PCB     | Printed Circuit Board                             |

|---------|---------------------------------------------------|

| PCBC    | Propagating or Plaintext Cipher-Block Chaining    |

| PCI     | Peripheral Component Interconnect                 |

| PDIP    | Plastic Dual Inline Package                       |

| PHP     | PHP: Hypertext Preprocessor                       |

| PIR     | Passive Infrared                                  |

| PN      | Part Number                                       |

| PTC     | Positive Temperature Coefficient                  |

| PTP     | Picture Transfer Protocol                         |

| QSPI    | Quad SPI                                          |

| R,G,B   | Red, Green, Blue                                  |

| RADAR   | Radio Detection and Ranging                       |

| RAID    | Redundant Array of Independent Disks              |

| RAM     | Random Access Memory                              |

| RC      | Remote Control                                    |

| RDS(on) | Resistance from drain to source, when in on state |

| RF      | Radio Frequency                                   |

| RFC     | Request for Comments                              |

| RFID    | Radio Frequency Identification                    |

| RGB     | Red Green Blue                                    |

| RH      | Relative humidity                                 |

| RMS     | Root Means Square                                 |

| RNA     | Ribonucleic Acid                                  |

| RSA     | Rivest-Shamir-Adleman (Encryption)                |

| RX      | Receiver or reception                             |

| SAR     | Successive approximative register                 |

| SATA    | Serial Advanced Technology Attachment             |

| SCK     | Serial Clock                                      |

| SCL     | Serial Clock                                      |

| SCR     | Silicon controlled rectifier                      |

| SD      | Secure Digital                                    |

| SDA     | Serial Data                                       |

| SDRAM   | Synchronous Dynamic Random Access Memory          |

| SFTP    | Secure File Transfer Protocol                     |

| SMD     | Surface Mount Device                              |

| SNTP    | Simple Network Time Protocol                      |

| SOIC    | Small Outline Integrated Circuit                  |

| SPDT    | Single Pole Double Throw                          |

| SPI     | Serial Peripheral Interface                       |

| SPST    | Single Pole Single Throw                          |

| SQL     | Structured Query Language                         |

| SRAM  | Static Random Access Memory                             |

|-------|---------------------------------------------------------|

| SS    | Slave Select                                            |

| SSD   | Solid State Drive                                       |

| SSH   | Secure Shell                                            |

| STFT  | Short Term Fourier Transform                            |

| ТВ    | Terabyte                                                |

| ТСР   | Transmission Control Protocol                           |

| TCR   | Temperature Coefficient of Resistance                   |

| TDP   | Thermal Design Power                                    |

| THT   | Through Hole Technology                                 |

| TIOBE | The Importance Of Being Earnest                         |

| TTL   | Transistor-to-transistor logic                          |

| TV    | Television                                              |

| TVS   | Transient Voltage Suppressors                           |

| TWI   | Two Wire Interface                                      |

| ТХ    | Transmitter / Transmission                              |

| UART  | Universal Asynchronous Receiver/Transmitter             |

| UDIMM | Unbuffered Dual In-Line Memory Module                   |

| UDP   | User Datagram Protocol                                  |

| UHF   | Ultra-High Frequencies                                  |

| URL   | Uniform Resource Locator                                |

| US    | United States                                           |

| USA   | United States of America                                |

| USART | Universal Synchronous/Asynchronous Receiver/Transmitter |

| USB   | Universal Serial Bus                                    |

| UV    | Ultraviolet                                             |

| V     | Volt                                                    |

| VHDL  | VHSIC Hardware Description Language                     |

| VHF   | Very High Frequency                                     |

| VI    | Input Voltage                                           |

| VIH   | Input Voltage (high, minimum)                           |

| VIL   | Input Voltage (low, maximum)                            |

| VO    | Output Voltage                                          |

| VOH   | Output Voltage (high, minimum)                          |

| VOL   | Output Voltage (low, maximum)                           |

| WAN   | Wide-Area Network                                       |

| WDT   | Watchdog Timer                                          |

| WWW   | World-Wide Web                                          |

| XOR   | Exclusive OR                                            |

| YB    | Yottabyte                                               |

| ZB    | Zettabyte                                               |

[Digital] Electronics by Example: When Hardware Greets Software

# 1. Brief Introduction to Digital Circuits and Programming

#### 1.1 Analog signals

All the studied systems in high-school's physics classes were composed from analog equipment/devices (voltage supplies, current supplies, resistors, capacitors, inductors, lightbulbs etc.). They are circuits where, for example, the voltage varies continuously within some limits. A default system is an analog audio amplifier, which takes an analogue audio signal, amplifies it (keeps the shape, but delivers more power from the supply) and sends it to the speakers. Analogue signals are hard to store and process, so lately, digital signals are used increasingly.

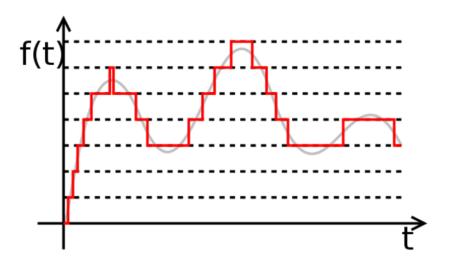

Figure 1. A digital signal (as a result of both sampling and quantization processes)

#### 1.2 Digital signals

A digital signal is a signal which is discrete (as opposed to continuous) in both time and value. To create a time-discrete signal, one samples a continuous one. To create a value-discrete signal, one quantizes a continuous one.

The number of samples taken in a unit of time is called sampling rate (e.g., 44100 Hz == samples per second, CD-quality). The number of bits (0 or 1 symbols) required to express the amplitude is linked directly to the number of quantization steps (e.g., 16-bit for 2 to the power of 16 = 65536 steps, in the case of CD-audio quality)

Figure 2. A time-sampled signal (as a result of sampling process)

Figure 3. A value-sampled signal (as a result of quantization process)

Digital signals are used because their expression uses numbers, which allows easy storage, copying (without loss) and processing. Immunity to noise can be obtained using mathematical instruments like error-detection and error-recovery processes. In addition, the quality (how similar it looks to the source analogue signal) can be chosen as a compromise. The more quantization steps we use (e.g. infinite) the more accurate the value is to the source signal's value: however, these systems are usually used for the comfort of human life, so the trade-off will take into consideration human hearing or human sight etc. which will not push the quantization step too high (e.g. audio signals are good enough when using 64k steps, that is 16-bits per sample; video signals are good enough when colors are represented with 256 steps of Red, Green and Blue, therefore 3x 8-bits are enough for a pixel) Regarding

the recovery of a continuous signal from the time-sampled signal, we have the sampling theorem which demonstrates that we can fully recover the original, as long as the sampling rate is at least twice the maximum frequency contained in the original signal. For example, if one wants to recover up to 22 kHz audio signals (more than what the common human ear can hear), one should use 44 kHz sampling rate.

#### 1.3 Digit, number, and radix

A radix-10 number uses a dictionary of 10 symbols (the ten digits) to express any number. For example, number 123 is made of 1 \* 100 + 2 \* 10 + 3. The radix of 10 is not the only known radix but is the most used by humans (arguably because we have ten fingers and can count easily using them). However, to use radix of 10, one must distinguish between 10 different symbols (0-9). Digital electronics use radix of 2 because it is easier to distinguish between only two symbols, therefore it is easier to store information in this form. The trade-offs that same number expressed in radix of 10 is around 3.5 times shorter that a radix of 2. For example, 9 is expressed in radix 2 with the sequence 1001, the number 127 is 1111111 etc. The symbols available for the radix of 2 are 0 and 1, and they are called Blnary digiTS, in short bits. Using 2 digits we can express numbers from 0 to 39 (that is, 100 different numbers). Using 2 bits we can express numbers from 0 to 3 (that is, 4 different numbers). Most common radices are 2 (binary), 8 (octal), 16 (hex), 10 (dec) and 256. We will mark numbers in radix 2, as prefixed with 0b e.g.: 0b1001 is number 9 in radix 10. The hexadecimal number will be prefixed with 0x e.g.: 0x10 is 16 in radix 10.

| Memory Unit (JEDEC)      | Memory unit (IEC) | Description         |

|--------------------------|-------------------|---------------------|

| Bit                      | Bit               | Binary Digit 1 or 0 |

| Kbit                     | Kibibit           | 1024 bits           |

| Mbit                     | Mebibit           | 1024 Kbits          |

| Byte                     | Byte              | 8 bits              |

| KiloByte(KB)             | KibiByte (KiB)    | 1024 Bytes          |

| MegaByte(MB)             | MebiByte (MiB)    | 1024 КВ             |

| GigaByte(GB)             | Gibibyte (GiB)    | 1024 MB             |

| TeraByte(TB)             | Tebibyte (TiB)    | 1024 GB             |

| PetaByte(PB)             | Pebibyte (PiB)    | 1024 TB             |

| HexaByte or exaByte (EB) | Exbibyte (EiB)    | 1024 PB             |

| ZettaByte (ZB)           | Zebibyte (ZiB)    | 1024 EB             |

| YottaByte (YB)           | Yobiibyte (YiB)   | 1024 ZB             |

Table 1. Multiples of bits / bytes according to JEDEC [1]. IEC 80000-13 standard changes the name for the power of two, by inserting a "bi" in the name: Kibibyte, Mebibyte, Gibibyte.

#### 1.4 Digital systems

Digital systems are designed to store and process and exchange information in digital form. They are found in a wide range of applications, including process control, communication systems, digital instruments, and consumer products. These systems/circuits may be classified by the number of *appropriate* loops enclosed within [3]; more loops will mean more autonomy, therefore *smarter* circuits.

0 - loop circuits: contain only combinational circuits (logic gates)

1 - loop circuits: the memory circuits, with behavioral autonomy in their own internal states; they are mainly used for *storing*

2 - loops circuits: the automata, with the behavioral autonomy in their own state space, performing mainly the function of *sequencing*

3 - loops circuits: the processors, with the autonomy in interpreting their own internal states; they perform the function of *controlling*

4 - loops circuits: the computers, which interpret autonomously the programs according to the internal *data*

n-loop circuits: systems in which the information is interpenetrated with the physical structures involved in processing it; the distinction between *data* and *programs* is surpassed and the main novelty is the *self-organizing* behavior.

Any k-loop circuit can do everything any k-1 loop circuit can do.

While 0 – loop circuits (combinational logic circuits) are quite easy to grasp as they are very simple in structure and behavior, the more evolved circuits, containing sequential circuits (with the clock signal driving them) are the ones used to handle complexity.

Some common 0-loop circuits are: logic gates, multiplexers (sends the selected digital input to the output), demultiplexers (send the input to the selected output), decoders (sends logic 1 to the selected output), adders, subtractors, ALUs (arithmetical-logical units), equality comparators, magnitude comparators etc.

Some common sequential circuits are flip-flops (FFs), registers, counters/timers, and FSMs.

For an in-depth discussion on this subject, refer to book [3].

#### 1.5 Programming a 4-loops digital system (computer)

Writing a program for a computer requires describing steps to be performed in a specific order. The description is done in a "programming language" usually containing keywords in English language (like C, Java, Python), written in a source file, then interpreted or compiled and ran on a computer.

#### 1.6 Components of a computer

Motherboard: the mainboard that electrically links all high-speed components of the PC

- CPU: central processing unit, the "brain" of the computer

- GPU: graphical processing unit, which renders images to be shown on the monitor.

- RAM: random-access memory, is used while running programs

- Storage: long-term storage (non-volatile storage) where operating systems / applications / files reside

- Usual peripherals:

- Monitor (display) where people may see visually the output of the computer.

- Mouse (hand-held pointing device, that detects 2D relative movement on a surface)

- Keyboard (key-based input device, usually holds all 26 English letters, 0-9 digits and punctuation marks)

Figure 4. AMD Athlon64 x2 CPU (left is top, right is bottom) with Socket 939

[Digital] Electronics by Example: When Hardware Greets Software

Figure 5. 32GB DDR5-4800 RAM server memory with error correction code (ECC)

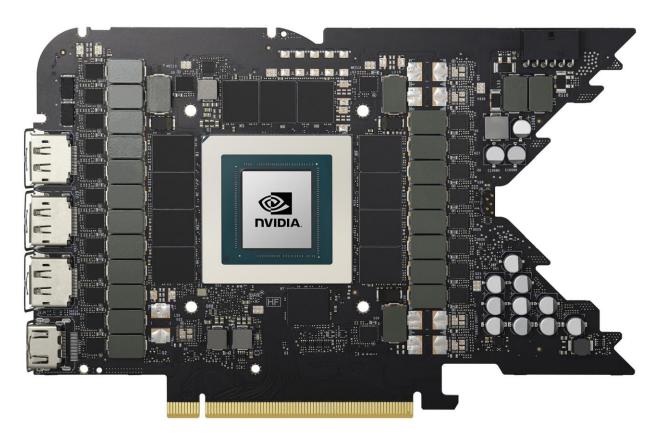

Figure 6. RTX4090 GPU card with PCIexpress x16 slot, without passive and active cooling installed.

The GPU chip is the largest square chip, the black vertical parts (10+) are coils for the power lines and the 12 black chips around the GPU are memory chips

[Digital] Electronics by Example: When Hardware Greets Software

Figure 7. A SATA-interfaced SSD (Solid State Disk) for non-volatile storage.

Data rate (read and write speed) is limited by the SATA3 interface at up to 550 MB/s, making them slower than the PCIexpress versions. As a transfer rate, they can go up to 7 GB/s for both read and write)

Figure 8. A PCIe-interfaced SSD for long term storage.

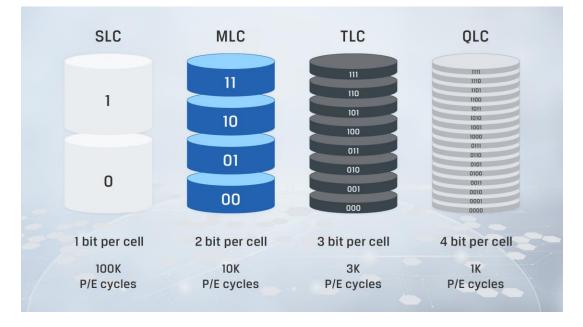

Figure 9. A comparison between SLC, MLC, TLC and QLC cells

Random access non-volatile storage is provided by electro-mechanical or electronic storage. While the mechanical hard drives had their advantages in capacity, nowadays, electronic storage caught up and enable movement-free information storage. There are multiple types of cells used in solid-state drives, each having their compromise between cost, capacity and endurance. High endurance cells (SLC) allow only one bit of data to be stored in a cell (which provides large noise margin), whereas all other cells decrease the noise margin to increase data density. A common SLC memory allows over 100K cycles of programming (set to 0) or erase (set to 1), whereas QLC only handles thousands.

Monitors advanced from the CRT (cathode-ray tube) technology where a electrons emitted from a source are directed using electromagnets towards the surface of the screen, to flattube technologies where light is either backlight is let pass through a controllable array of pixels, or the very pixels (picture elements) are composed of individual LEDs which are powered on and off selectively, by the same commands (as CRTs) coming from a video card.

Figure 10. A monitor with common pixel resolutions (HD = High definition).

The monitor surface is composed of pixels (individual light sources/sinks, that are lit independently according to the image sent by the software using the video card, via video interface). For 4K monitors, there are about 8 million pixels in each image. To create the effect of a moving picture, the images are time-spaced at 33 milliseconds (30 frames per second), 16.6ms (60 fps) or less, for gaming setups (where higher fps allows faster reactions)

[Digital] Electronics by Example: When Hardware Greets Software

Figure 11. RGB (red, green, blue) pixels in monitor image that spatially combine to obtain all colors (white color is all RGB leds in that pixel lit)

#### RAID

The RAID (Redundant array of independent/inexpensive disks) is a way of grouping drives into more flexible setups for larger storage, higher speed or higher redundancy. In the past, when SSD were not present, mechanical drives were the only way for large non-volatile, random-access storage. This implies that mechanical movement of the read and write head, limited the read/write speed of the drive. The server drives were smaller in diameter (to allow a smaller movement) and higher in speed (regular drives were 5400 or 7200 rpms, whereas server drives were 10k or 15k rpms). The emergence of SSDs with their electronic storage cancels the speed advantages of the RAID arrays using mechanical drives, however enthusiasts may still group SSDs into RAID arrays for data redundancy purposes.

| RAID mode | Minimum number of disks  |

|-----------|--------------------------|

| JBOD      | 1                        |

| RAID 0    | 2                        |

| RAID 1    | 1 (no data protection)   |

|           | 2 (with data protection) |

| RAID 5    | 3                        |

| RAID 6    | 4                        |

| RAID 10   | 4                        |

Table 2. Common RAID modes and their minimum requirements

#### 1.6.1.1 JBOD (Just a bunch of disks)

JBOD is a configuration where data is stored sequentially: data not fitting the first disk is automatically overflown into second disk etc.

Advantage: sum of the disks space is the total available disk space. Disadvantage: any one drive fails implies data will be lost Total capacity of N drives with C storage capacity each: N \* C

#### 1.6.1.2 RAID 0 (data striping)

The RAID 0 mode is the fastest RAID mode as it writes data consecutive data blocks on different disks, which, in mechanical drives means the access time is decreased, therefore increasing the read and write data rate. It is the preferred choice for gamers.

Figure 12. RAIDO: high speed, no redundancy

Advantage: high read/write/data speed, higher that single-drive Disadvantage: if one drive fails, the array fails Total capacity of N drives with C storage capacity each: N \* C

#### 1.6.1.3 RAID 1 (data mirroring)

The RAID 1 mode mirrors all data on all drives. Assuming the array is made of N drives of C storage capacity each, the available capacity of the array is C but the reliability is very high, with some speed improvements when reading a lot of small files.

Advantage: for N-drive array, all N drives must break to break the array Disadvantage: expensive (high cost per available storage capacity) Total capacity of N drives with C storage capacity each: C

Figure 13. RAID1 mode: data mirroring

#### 1.6.1.4 RAID5

The RAID5 is a compromise between the speed and reliability. A parity block is written consecutively on each drive, along a series of data blocks. The parity block allows data reconstruction if any one drive fails.

Figure 14. RAID5 mode: single drive redundancy

Advantage: one drive may fail and the array will still not lose data Disadvantage: a drive's capacity is not available in the array, since it is reserved for parity Total capacity of N drives with C storage capacity each: (N-1) \* C

#### 1.6.1.4 RAID6

As opposed to RAID5, where only one parity block is written per each set of data blocks, in RAID6, two parity blocks are written: this increased redundancy but decreases the available storage space.

Advantage: two drives are allowed to fail and the array will not lose data Disadvantage: two drives' capacity is not available since it is reserved for parity Total capacity of N drives with C storage capacity each: (N-2) \* C

Figure 15. RAID6 mode: dual drive redundancy

#### 1.6.1.5 RAID10

RAID10 is a combination of RAID1 and RAID0 to increase performance yet having high data redundancy. It is used mainly for increasing performance in accessing small files and keeping high reliability of the array.

Advantage: speed, and up to half of the drives are allowed to fail and the array might not lose data Disadvantage: half of storage space is unusable

Total capacity of N drives with C storage capacity each: (N/2) \* C

Figure 16. RAID10: a RAID 0 of RAID1s

Figure 17. Anandtech's comparison of Intel P4510 SSD (x4 PCIe) drives in various RAID configurations

#### 1.7 Computer networks

Computer networks are based on a layered model, where each level does its job requested by the higher layer and forwards new work to the lower layer. This ensures that no layer is too complicated, and multiple technologies of the same type may be mixed and matched easily.

| Layer                                                                                                                                       | Application/Example                                                                                                                                                                                                                                                                           | Central Device/<br>Protocols |                     |                  | DOD4<br>Model |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------------------|---------------|

| Application (7)<br>Serves as the window for users and<br>application processes to access the network<br>services.                           | End User layer Program that opens what<br>was sent or creates what is to be sent<br>Resource sharing - Remote file access - Remote printer access -<br>Directory services - Network management                                                                                                | User<br>Applications<br>SMTP |                     |                  |               |

| Presentation (6)<br>Formats the data to be presented to the<br>Application layer. It can be viewed as the<br>"Transilator" for the network. | Syntax layer encrypt & decrypt (if needed)<br>Character code translation • Data conversion • Data compression •<br>Data encryption • Character Set Translation<br>PICT                                                                                                                        |                              | G                   | Process          |               |

| Session (5)<br>Allows session establishment between<br>processes running on different stations.                                             | Synch & send to ports (logical ports)     Logical Ports       Session establishment, maintenance and termination - Session support - perform security, name recognition, logging, etc.     RPC/SQL/NFS NetBIOS names                                                                          |                              |                     |                  |               |

| Transport (4)<br>Ensures that messages are delivered<br>error-free, in sequence, and with no<br>losses or duplications.                     | TCP Host to Host, Flow Control F P L T   Message segmentation • Message acknowledgement • A C T T T   Message traffic control • Session multiplexing K R T T   Packets ("letter", contains IP address) K R R Routers   Routing • Subnet traffic control • Frame fragmentation • G IP/IPX/ICMP |                              | E<br>W<br>A         | Host to<br>Host  |               |

| Network (3)<br>Controls the operations of the subnet,<br>deciding which physical path the<br>data takes.                                    |                                                                                                                                                                                                                                                                                               |                              | Y<br>Can be<br>used | Internet         |               |

| Data Link (2)<br>Provides error-free transfer of data frames<br>from one node to another over the<br>Physical layer.                        | Frames ("envelopes", contains MAC address)<br>[NIC card — Switch — NIC card] (end to end)<br>Establishes & terminates the logical link between nodes - Frame<br>traffic control - Frame sequencing - Frame acknowledgment - Frame<br>elelimiting - Frame second bedia access control          |                              | Land<br>Based       | on all<br>layers | Natural       |

| Physical (1)<br>Concerned with the transmission and<br>reception of the unstructured raw bit stream<br>over the physical medium.            | Physical structure Cables, hubs, etc. Hub<br>Data Encoding • Physical medium attachment •<br>Transmission technique - Baseband or Broadband •<br>Physical medium transmission Bits & Volts                                                                                                    |                              |                     |                  | Network       |

Figure 18. OSI layer model for networks

Hardware components of a computer network are the ones implementing Layer 1 (cables, connectors), Layer 2 (switches), Layer 3 (routers). From Layer 4 upwards, the software running on a computer, will take over.

Software components of a computer network are the ones implementing Layer 4 (data protocols), Layer 5 (ports/sockets), Layer 6 and Layer 7 (applications)

The tiered approach allows a network to change for example the physical layer, by replacing the NIC (network interface card) from one implementing copper wires to fiberoptics for example, without changing the upper layers (including the application).

Common transport protocols for sending data are: TCP (Transport Control Protocol, see RFC 9293) and UDP (Unified Datagram Protocol, see RFC 768). TCP has the advantage of guaranteeing delivery and the order of the packets (by error detection and correction via

checksum, ack and timeout) and is used for example if file transfers, whereas UDP has the advantage of low-latency (and is mainly used when obsolete data that was not transmitted is not important, e.g. webcam streaming)

Figure 19. TCP vs UDP in how data is transmitted an the possible types of connections

Multiple computers may be connected in the same network using a plethora of architectures like: bus, ring, mesh, star, tree, hybrid...

Figure 20. Visual examples of network topologies

#### 1.8 Network services

The Internet network is a computer network where each communication partner has its own unique (public IP) address. Started in 1969 as ARPANET by ARPA (Advanced Research Projects Agency), it provided a decentralized network (destroying one node will not bring down the network) for military usage, and assured only three network services: telnet (remote login), file transfer (by FTP) and remote printing.

Civilian usages started to become apparent with the 1970s to 1980s, when the universities joined it, while operational control was transferred to various entities and it was expanded with CSNET, then while plans were made for decommission, another similar network, the NSFNET funded by National Science Foundation, (NSF) became the backbone of the Internet.

Most known service is WWW (World Wide Web) [22], invented by Tim Berners-Lee in 1989 while working at CERN [21]. The web-pages may be found in the Internet according to a wenaddress (URL – Uniform Resource Locator), and are requested by a client (usually a webbrowser) from a server (web-server) using the http (Hypertext Transfer Protocol).

Other services include remote connection (telnet, SSH), file transfer protocol (via FTP, SFTP), time services (NTP, SNTP, PTP), directory services (DNS), automatic network address configuration (DHCP), and network management services (ping, traceroute).

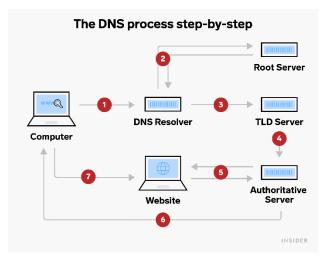

A special mention for the DNS service which allows one to access using a website using a name, while the server has in OSI Level 3 an IP address. The DNS resolver does this conversion from name to address as seen in figure below

Figure 21. Resolving a website's server address by using DNS hierarchy.

Request 1 is via name and is answered using message 6; request 7 is using public IP address.

#### 1.9 Reaction and feedback

In the world of electronics, reaction is the change seen at the output of a system, as a consequence of a change made at the input of the system.

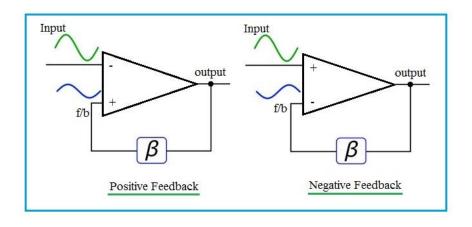

Feedback refers to the process of returning a part of the signal output back to the input of the system. If the feedback is made in such a way to oppose change (increase of input produces increase of the output which produces the decrease of the input), we will say that negative feedback occurred. If the change on the input produces a change of the output which produces a change encouraging the input, then we will say a positive feedback occurred.

Negative feedback loops are useful for making and keeping a system stable.

Positive feedback loops are useful for making oscillators.

Figure 22. Positive feedback loop (left). Negative feedback loop (right)

Table 3. Comparison between positive and negative feedback in electronics

| Parameter                       | Positive Feedback   | Negative Feedback   |

|---------------------------------|---------------------|---------------------|

| Input and output voltage, noise | increases due to fb | Decreases due to fb |

| Fb signal and input signal      | in phase            | out of phase        |

| Gain                            | increases           | decreases           |

| Stability                       | poor                | better              |

| applications or use             | oscillators         | amplifiers          |

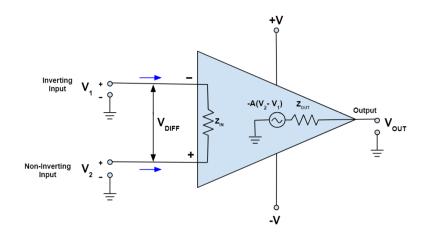

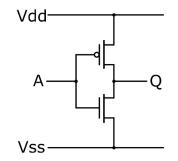

The triangle-shaped picture is called "operational amplifier", is analog circuit block, and is used to output a single-ended voltage (that is, referred to the GND), Vout, as the product of Amplification (A) and input voltage differential (Vdiff =  $V_+ - V_-$ ). It is used in digital designs

to improve output current capacity in a configuration where A = 1. In analog designs is used in filters or amplifiers. Input impedance is much higher than output imp ( $Z_{in} >> Z_{out}$ )

Figure 23. Operational amplifier (opamp)

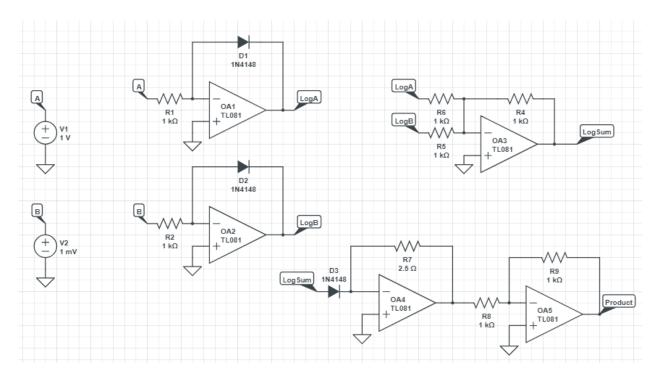

Just before switching to digital electronics, analog computers were used for calculations. It is obvious how a subtraction could be made using op-amps since in the above example, Vo = A(V2 - V1), but how about multiplication of two voltages? (V2\*V1) is usually done by summation of logarithms: logV2 + logV1 = log(V2\*V1) and then exponentiation.

Figure 24. Op-amps configured with diodes or resistors in their feedback loop to do: logarithmation, summation or product

### 2. Basic hardware bricks

#### 2.1 Binary and Boolean Logic

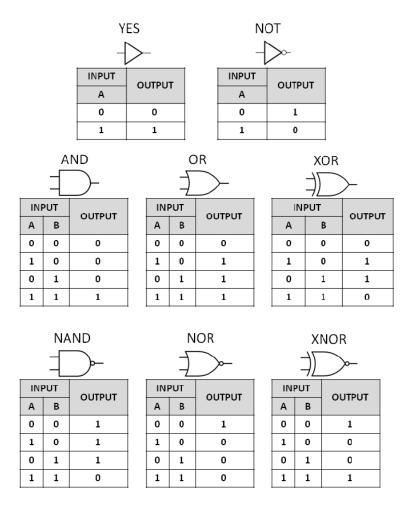

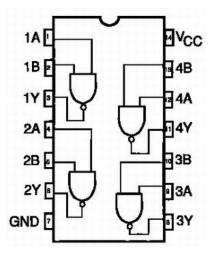

Boolean algebra is a branch of algebra, where the values of the variables are truth values (true and false) usually coded as 1 and 0 and uses logical operators such as AND (conjunction), OR (disjunction), NOT (negation). It was introduced by English mathematician George Boole in the book "The Mathematical Analysis of Logic" in 1847.

A logical operation is a function of two variables and may be expressed using a truth table as below:

| А     | В     | OP (A, B) |

|-------|-------|-----------|

| FALSE | FALSE | ?         |

| FALSE | TRUE  | ??        |

| TRUE  | FALSE | ???       |

| TRUE  | TRUE  | ????      |

Table 4. A (general) logic operation's truth table

There are 16 dual-input single-output logical operations, 3 of which are most used (hence named). Their truth table is as below:

| А     | В     | A and B | A or B | Not A |

|-------|-------|---------|--------|-------|

| FALSE | FALSE | FALSE   | FALSE  | TRUE  |

| FALSE | TRUE  | FALSE   | TRUE   | TRUE  |

| TRUE  | FALSE | FALSE   | TRUE   | FALSE |

| TRUE  | TRUE  | TRUE    | TRUE   | FALSE |