### Călin BÎRĂ

\_\_\_\_\_

=========

# Digital Electronics by Example

When Hardware greets Hardware

#### **Preface**

This book is an educational book and provides examples and exercises for the students in  $2^{nd}$  year of bachelor's degree path, regarding the Digital Electronics topic.

Chapter one provides an introduction into analog and digital signals and systems and is similar to the introduction in [1]

Chapter two starts with exercises regarding 0-loop circuits (CLCs).

### **Table of Contents**

| Preface                                                   | 2  |

|-----------------------------------------------------------|----|

| Table of Contents                                         | 3  |

| List of Figures                                           | 5  |

| List of Tables                                            | 8  |

| List of Acronyms                                          | 8  |

| 1. Brief Introduction to Digital Circuits and Programming | 13 |

| 1.1 Analog signals                                        | 13 |

| 1.2 Digital signals                                       | 13 |

| 1.3 Digit, number, and radix                              | 15 |

| 1.4 Digital systems                                       | 16 |

| 1.5 The advantages of using digital systems               | 17 |

| 2. The FPGA (Field Programmable Gate Array)               | 18 |

| 2. Zero-loop systems                                      | 22 |

| 2.1 Prerequisites                                         | 22 |

| 2.1.1 Binary and Boolean Logic                            | 22 |

| 2.1.2 Digital Gates                                       | 23 |

| 2.1.3 Voltage levels (VI / VO)                            | 25 |

| 2.1.4 Logic gates components                              | 26 |

| 2.1.5 Complexity in digital circuits                      | 27 |

| 2.1.6 Complexity classes                                  | 27 |

| 2.1.7 Verilog syntax                                      | 30 |

| 2.1.7 VHDL syntax                                         | 32 |

| 2.1.8 Simulation                                          | 34 |

| 2.1.9 Our first digital circuit - the switch tester       | 34 |

| 2.2 Theory & Exercises                                    |    |

| 2.2.1 Multiple-input gates                                | 37 |

| 2.2.2 Elementary multiplexer                              |    |

| 2.2.3 Elementary decoder and 2-to-4 decoder               |    |

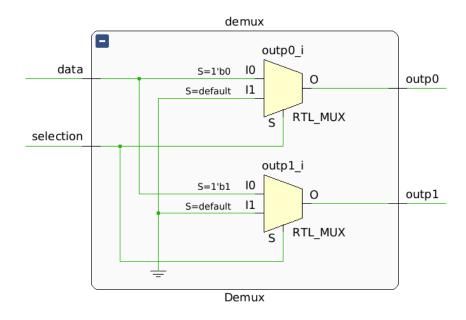

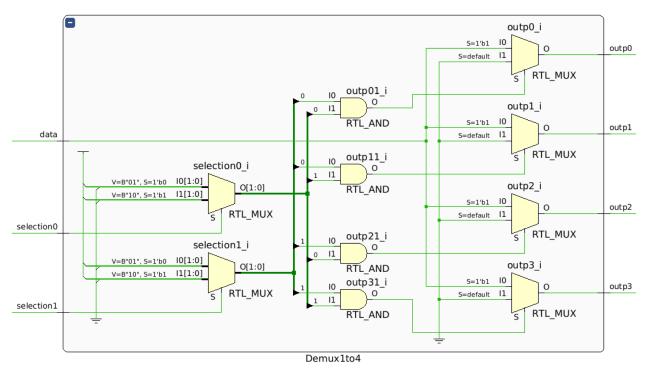

| 2.2.4 Elementary demultiplexer and 1-to-4 demux                    | 47 |

|--------------------------------------------------------------------|----|

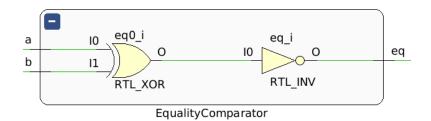

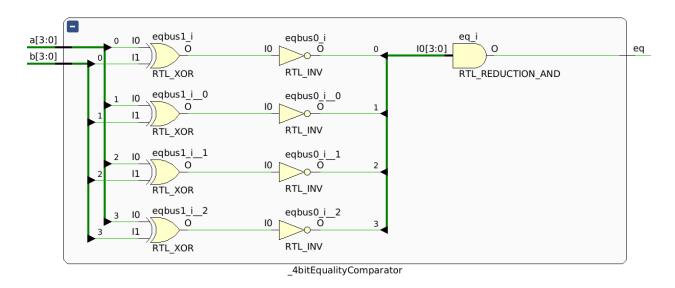

| 2.2.5 Elementary equality comparator and N-bit equality comparator | 48 |

| 2.2.6 Magnitude comparator                                         | 50 |

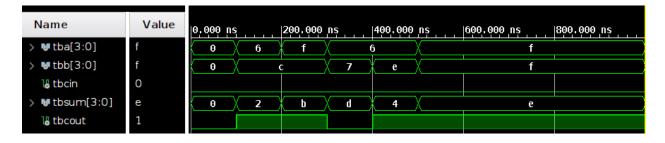

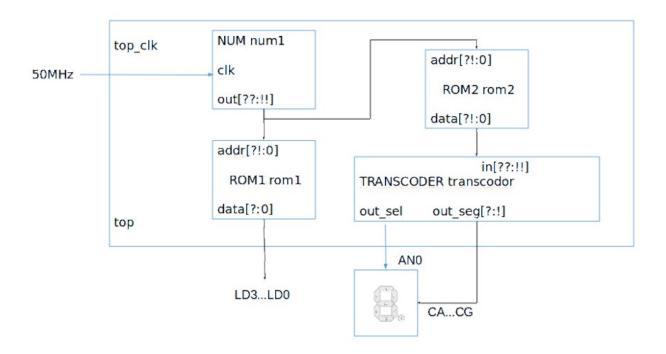

| 2.2.7 The 7-segment display transcoder                             | 53 |

| 3. One-loop systems                                                | 67 |

| 4. Two-loop systems (automata)                                     | 67 |

| 4.1 Prerequisites                                                  |    |

| 4.2 Theory                                                         | 67 |

| 4.3 TODO: other exercises                                          | 67 |

| Figure References                                                  | 78 |

| References                                                         | 82 |

### List of Figures

| Figure 1. A digital signal (as a result of both sampling and quantization      |     |

|--------------------------------------------------------------------------------|-----|

| processes)                                                                     | 13  |

| Figure 2. A time-sampled signal (as a result of sampling process)              | 14  |

| Figure 3. A value-sampled signal (as a result of quantization process)         | 14  |

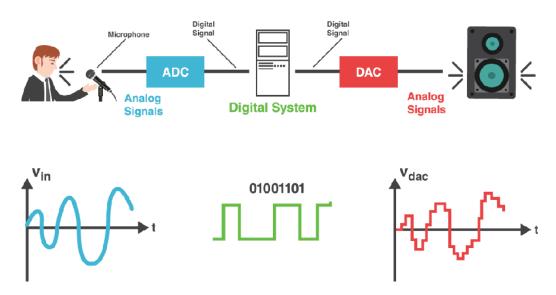

| Figure 4. Analog to digital conversion, digital processing and digital to anal | og  |

| conversion example                                                             | .17 |

| Figure 5. Generic FPGA Architecture Overview                                   | .18 |

| Figure 6. Xilinx CLB. Blue blocks are multiplexers, violet blocks are FFs and  |     |

| dark-green blocks are LUTs (look-up tables)                                    | 18  |

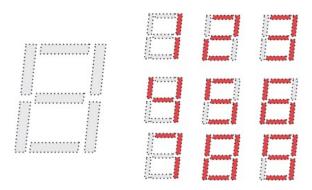

| Figure 7. FPGA development flow                                                | 19  |

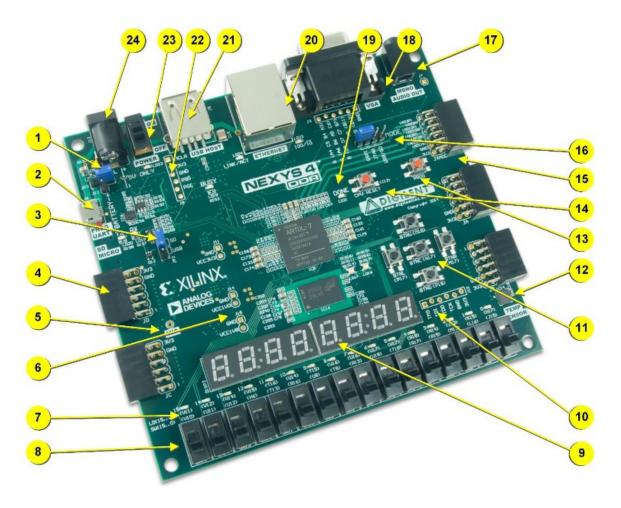

| Figure 8. The Nexys 4 DDR FPGA board                                           | 20  |

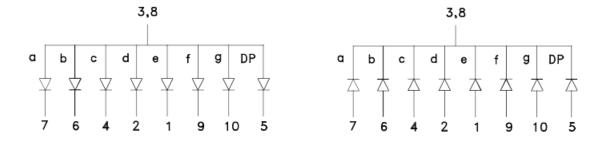

| Figure 9. Nexys 4 DDR board features                                           |     |

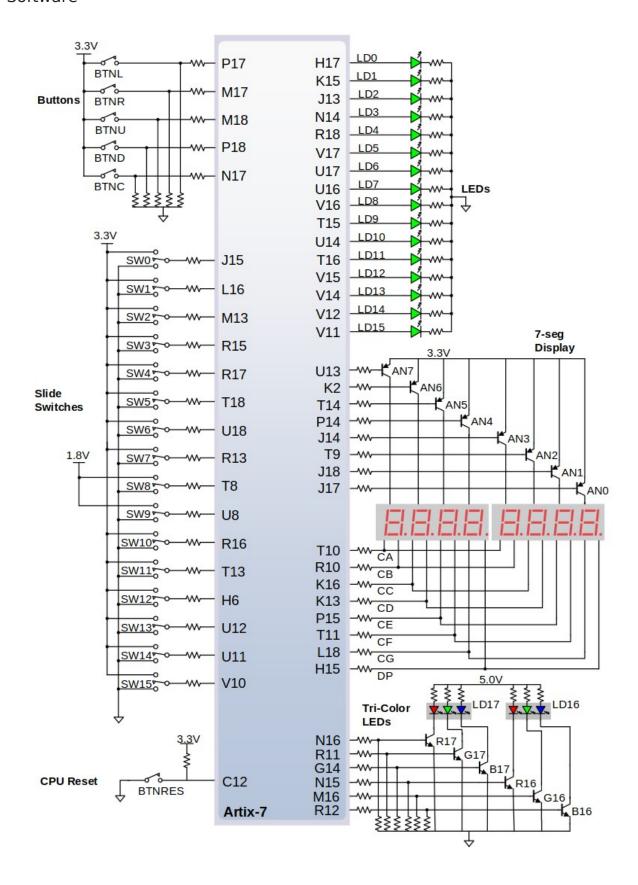

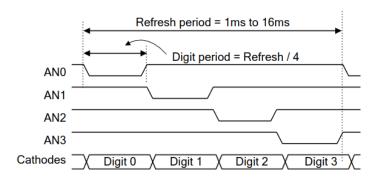

| Figure 10. GPIO devices on the Nexys4 DDR FPGA board                           | 21  |

| Figure 11. NOT gate ("inverter") made of one pMOS (top) and one nMOS           |     |

| (bottom) transistor                                                            | .23 |

| Figure 12. ANSI / IEC [6] (right) and MIL-STD-806B [7] (left) symbols foremore | st  |

| common 7/16 dual-input logic gates (elementary), with their names              | 23  |

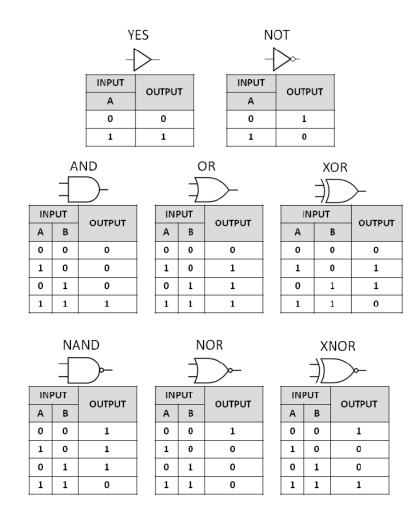

| Figure 13. The truth tables for the most commonly used logic gates             | 24  |

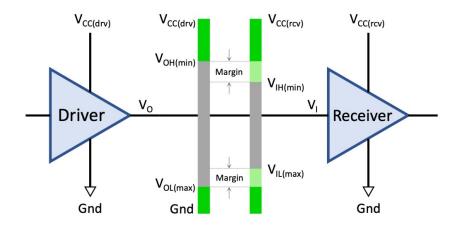

| Figure 14. Voltage levels: output requirements vs. input requirements          | 25  |

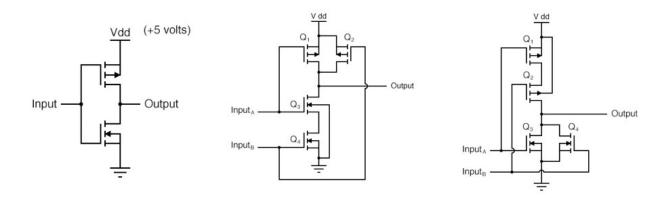

| Figure 15. MOSFET implementations of common logic gates. Left (NOT),           |     |

| middle (NAND), and right (NOR)                                                 |     |

| Figure 16. The 74HC04 hex-inverter circuit                                     | 26  |

| Figure 17. Representing a g(n) function which asymptotically bound f(n)        |     |

|                                                                                | .27 |

| Figure 18. The O-notation complexity increases with the number of elemen       |     |

| processed. O(1) and O(logn) are usually excellent complexities, O(n) is fair   |     |

| and O(n*logn) is usually considered almost decent in algorithms and circuit    |     |

|                                                                                | _   |

| Figure 19. A 16-input AND gate built from 2-input AND gates                    |     |

| Figure 20. Verilog syntax cheat sheet (1/2)                                    |     |

| Figure 21. Verilog syntax cheat sheet (2/2)                                    |     |

| Figure 22. VHDL cheat sheet (1/2)                                              |     |

| Figure 23. VHDL cheat sheet (2/2)                                              |     |

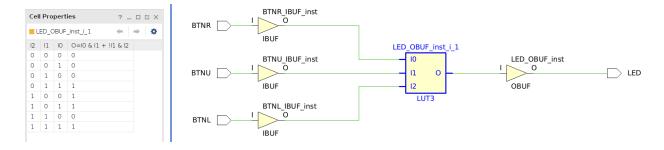

| Figure 24. The schematic of a switch checker                                   |     |

| Figure 25. Verilog description of switch-checker                               |     |

| Figure 26. VHDL description of switch-checker                                  |     |

| Figure 27. 2-input AND gate                                                    |     |

| Figure 28. Verilog code (dataflow) for a 2-input AND gate                      | .36 |

| Figure 29. Verilog code (dataflow) for a 2-input AND gate                 | 36 |

|---------------------------------------------------------------------------|----|

| Figure 30. 4-input AND gate from 2-input AND gates (dataflow)             | 37 |

| Figure 31. Verilog description for 4-input AND (dataflow)                 | 37 |

| Figure 32. VHDL description for 4-input AND (dataflow)                    | 37 |

| Figure 33. 4-input AND gate from 2-input AND gates (structural)           | 38 |

| Figure 34. Verilog description of 4-input AND gate from 2-input AND gates |    |

| (structural)                                                              | 38 |

| Figure 35. VHDL description of 4-input AND gate from 2-input AND gates    |    |

| (structural)                                                              | 39 |

| Figure 36. MUX2 implemented with one NOT, two AND, one OR gate(s)         | 39 |

| Figure 37. LUT-based implementation of elementary mux, in FPGA            | 40 |

| Figure 38. Verilog description of an elementary MUX                       | 40 |

| Figure 39. VHDL description of an elementary MUX                          | 41 |

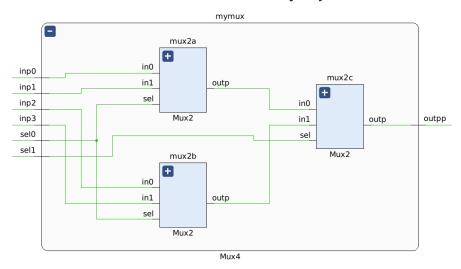

| Figure 40. Block schematic for MUX4 made of 3x MUX2                       |    |

| Figure 41. Verilog description of MUX4 made of MUX2 circuits              | 42 |

| Figure 42. VHDL description of MUX4 made of MUX2 circuits                 |    |

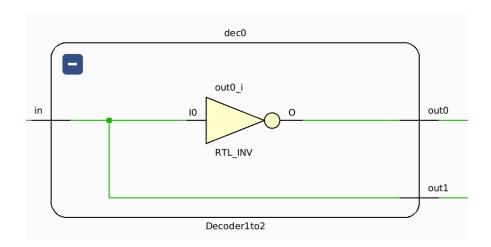

| Figure 43. Schematic of an elementary decoder                             |    |

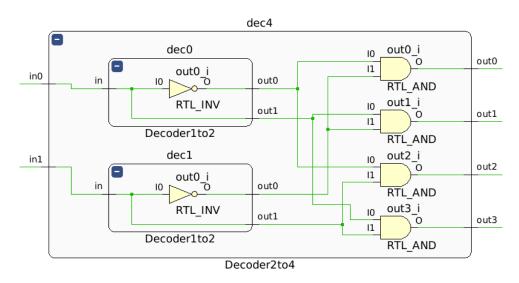

| Figure 44. Schematic of 2-to-4 decoder made of 1-to-2                     |    |

| Figure 45. Verilog description of elementary and 2-to-4 decoder           | 45 |

| Figure 46. VHDL description of elementary decoder                         |    |

| Figure 47. VHDL description of 2-to-4 decoder                             |    |

| Figure 48. Verilog description of elementary demux and 1-to-4 demux       |    |

| Figure 49. Verilog description of elementary equality comparator          |    |

| Figure 50. 4-bit equality comparator                                      |    |

| Figure 51. Verilog description of 4-bit equality comparator               |    |

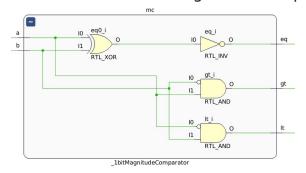

| Figure 52. One-bit magnitude comparator (1)                               |    |

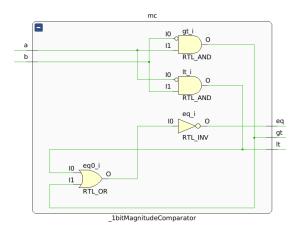

| Figure 53. One-bit magnitude comparator (2)                               |    |

| Figure 54. Verilog description of 1-bit magnitude comparator (with NOR ga |    |

|                                                                           |    |

| Figure 55. Verilog description of 2-bit magnitude comparator              |    |

| Figure 56. Verilog description of 4-bit magnitude comparator              | 51 |

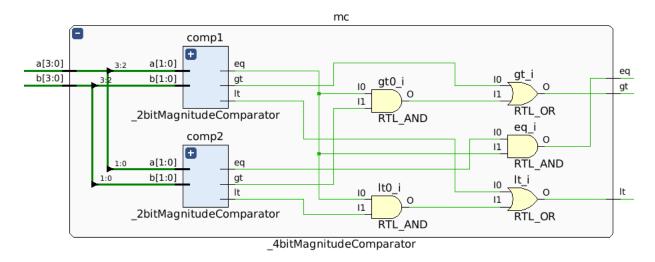

| Figure 57. Schematic of 4-bit magnitude comparator made of 2-bit          |    |

| magnitude comparator                                                      |    |

| Figure 58. VHDL description of 1-bit magnitude comparator                 |    |

| Figure 59. VHDL description of 4-bit magnitude comparator                 |    |

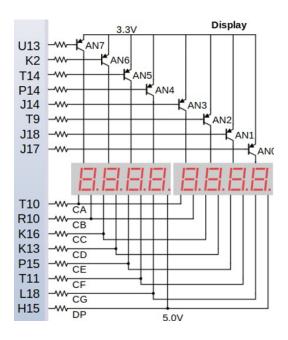

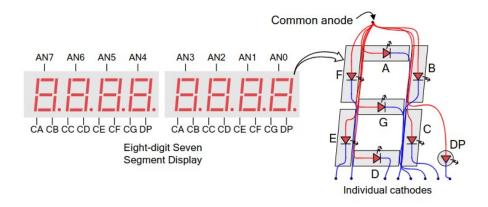

| Figure 60. 7-segment displays present on Nexys4 DDR (schematic)           |    |

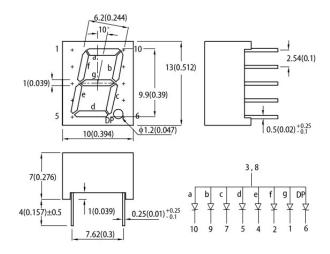

| Figure 61. A Kingbright 1-digit common anode, 7-segment display           |    |

| Figure 62. Font used for 0-9 characters in 7-segment displays             |    |

| Figure 63. The TDCG1060M clock display from Vishay                        | 54 |

| Figure 64. 7-Segment display as common anode (+) in the left side, and    |    |

| common cathode (-) in the right side                                      |    |

| Figure 65. Time-multiplexing for the 4x 7-segment displays                | 55 |

| Figure | 66. 2        | 2x 4 x digit comon anode circuit found in Nexys4 DDR | 55 |

|--------|--------------|------------------------------------------------------|----|

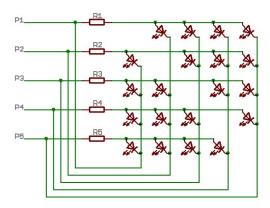

| Figure | 67. (        | Charlieplexing 5 I/Os to power 16 LEDs               | 55 |

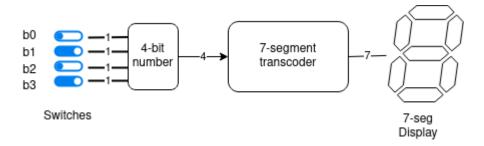

| Figure | 68. <i>A</i> | A 7-segment display data-driven by 4 on/off switches | 56 |

| Figure | 69. \        | Verilog description for 7-segment transcoder circuit | 56 |

| Figure | 70. \        | VHDL description of 7-segment display transcoder     | 57 |

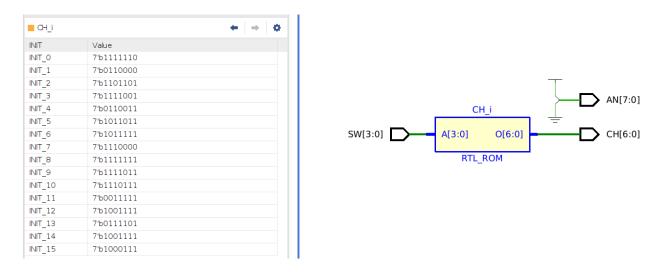

| Figure | 71. F        | RTL implementation of transcoder with ROM            | 58 |

| Figure | 72. (        | Constraints file for 7-segment transcoder circuit    | 58 |

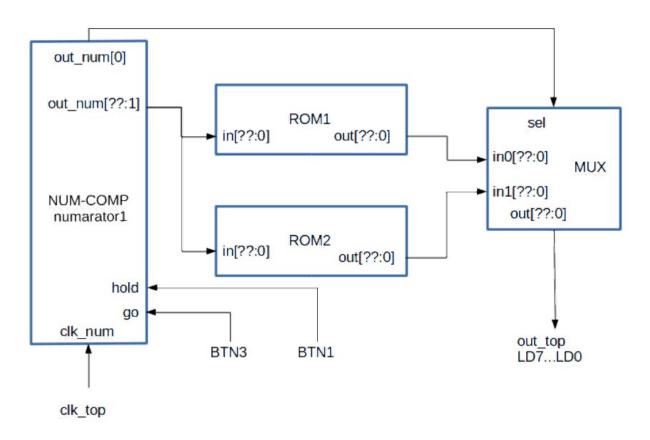

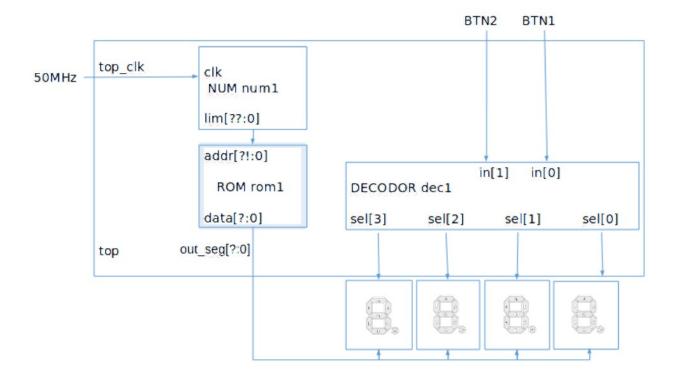

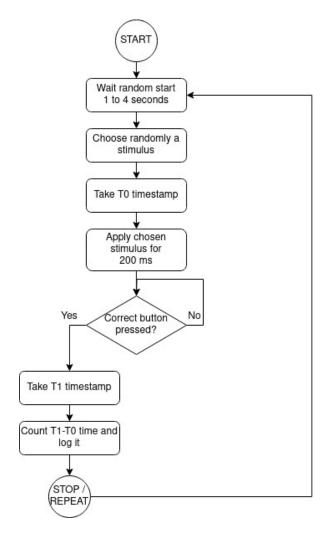

| Figure | 73. l        | Logic diagram of BCRT game                           | 74 |

| Figure | 74. E        | BCRT's class definitions                             | 75 |

| Figure | 75. E        | BCRT's main function                                 | 76 |

|        |              |                                                      |    |

### List of Tables

| Table 1. Multiples of bits / bytes according to JEDEC [3]. IEC 80000-13 |       |

|-------------------------------------------------------------------------|-------|

| standard changes the name for the power of two, by inserting a "bi" ir  | n the |

| name: Kibibyte, Mebibyte, Gibibyte                                      | 15    |

| Table 2. A (general) logic operation's truth table                      | 22    |

| Table 3. Truth tables for AND, OR and NOT operations                    | 22    |

| Table 4. Truth tables for AND, OR and NOT operations (seen as 1-bit     |       |

| operations)                                                             | 22    |

| Table 5. Recommended operating conditions for 54HC595 / 74HC595 I       | Cs (a |

| common 74HCxx circuit)                                                  | 25    |

### List of Acronyms

| AACS    | Advanced Access Content System                                                       |  |

|---------|--------------------------------------------------------------------------------------|--|

| AC      | Alternative Current                                                                  |  |

| ACK     | Acknowledge                                                                          |  |

| ADC     | Analog to digital converter                                                          |  |

| AES     | Advanced Encryption Standard                                                         |  |

| AGM     | Absorbent Glass Mat                                                                  |  |

| AMD     | Advanced Micro Devices                                                               |  |

| ANSI    | American National Standards Institute                                                |  |

| ARPA    | Advanced Research Projects Agency                                                    |  |

| ARPANET | Advanced Research Projects Agency Network                                            |  |

| ASIC    | Application Specific Integrated Circuit                                              |  |

| BIOS    | Basic Input-Output System                                                            |  |

| BJT     | Bipolar Junction Transistor                                                          |  |

| BOD     | Brown-out detect                                                                     |  |

| CBC     | Cipher Block Chaining                                                                |  |

| CD      | Compact Disk                                                                         |  |

| CDIP    | Ceramic Dual Inline Package                                                          |  |

| CERN    | Conseil Européen pour la Recherche Nucléaire / European Council for Nuclear Research |  |

| CFB     | Cipher Feedback Mode                                                                 |  |

| CMOS    | Complementary Metal-Oxide Semiconductor                                              |  |

| COBOL   | Common Business-Oriented Language                                                    |  |

| СРНА    | Clock Phase                                                                          |  |

| CPOL    | Clock Polarity                                                                       |  |

| CPU     | Central Processing Unit                                                              |  |

| CRT   | Cathode-Ray Tube                                  |  |  |

|-------|---------------------------------------------------|--|--|

| CS    | Chip Select                                       |  |  |

| CSNET | Computer Science Network                          |  |  |

| CTFT  | Continuous Time Fourier Transform                 |  |  |

| CTR   | Counter                                           |  |  |

| CUDA  | Compute Unified Device Architecture               |  |  |

| CV    | Computer Vision                                   |  |  |

| DAC   | Digital to Analog Converter                       |  |  |

| DDR   | Double Data Rate                                  |  |  |

| DES   | Data Encryption Standard                          |  |  |

| DHCP  | Dynamic Host Configuration Protocol               |  |  |

| DIP   | Dual In-line Package                              |  |  |

| DNS   | Domain Name Service                               |  |  |

| DRAM  | Dynamic Random Access Memory                      |  |  |

| DUT   | Device Under Test                                 |  |  |

| EB    | Exabyte                                           |  |  |

| ECC   | Error Correction Code                             |  |  |

| EMES  | Engineering of Modern Electric Systems            |  |  |

| FET   | Field-Effect Transistor                           |  |  |

| FIFO  | First-In First-Out                                |  |  |

| FIPS  | Federal Information Processing Standard           |  |  |

| FM    | Frequency Modulation                              |  |  |

| FTP   | File Transfer Protocol                            |  |  |

| GB    | Gigabyte                                          |  |  |

| GHz   | Gigahertz                                         |  |  |

| GND   | Ground                                            |  |  |

| GP    | General Purpose                                   |  |  |

| GPIO  | General Purpose Input/Output                      |  |  |

| GPU   | Graphical Processing Unit                         |  |  |

| GUI   | Graphical User Interface                          |  |  |

| HD    | High Definition                                   |  |  |

| HDD   | Hard Disk Drive                                   |  |  |

| HDL   | Hardware Description Language                     |  |  |

| HTML  | Hypertext Markup Language                         |  |  |

| IC    | Integrated circuit                                |  |  |

| IDE   | Integrated development environment                |  |  |

| IEC   | International Electrotechnical Commission         |  |  |

| IEEE  | Institute of Electrical and Electronics Engineers |  |  |

| IR    | Infrared                                          |  |  |

| ISO   | International Organization for Standardization    |  |  |

| JEDEC | Joint Electron Device Engineering Council         |  |  |

| JS    | JavaScript                                        |  |  |

|       |                                                   |  |  |

| KHZ Kilohertz  LED Light-emitting diode  LIDAR Light Detection and Ranging  LSB Least Significant Bit/Byte  MATLAB Matrix Laboratory  MB Megabyte  MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt |                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|

| LIDAR Light Detection and Ranging  LSB Least Significant Bit/Byte  MATLAB Matrix Laboratory  MB Megabyte  MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                          | Kilobyte<br>Kilohertz                          |  |  |

| LSB Least Significant Bit/Byte  MATLAB Matrix Laboratory  MB Megabyte  MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                             | Light-emitting diode                           |  |  |

| MATLAB Matrix Laboratory  MB Megabyte  MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                             | Light Detection and Ranging                    |  |  |

| MB Megabyte  MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                       | Least Significant Bit/Byte                     |  |  |

| MCU Microcontroller Unit  MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                    |                                                |  |  |

| MHz Megahertz  MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                                              |                                                |  |  |

| MIL-STD Military Standard  MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                                                             |                                                |  |  |

| MIT Massachusetts Institute of Technology  MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                                                                                        |                                                |  |  |

| MOhm Megohm  MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                                                                                                                                   |                                                |  |  |

| MOS Metal-Oxide Semiconductor  MSB Most Significand Bit/Byte  MW Megawatt                                                                                                                                                                                                                                                                                |                                                |  |  |

| MSB Most Significand Bit/Byte MW Megawatt                                                                                                                                                                                                                                                                                                                |                                                |  |  |

| MW Megawatt                                                                                                                                                                                                                                                                                                                                              |                                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                          |                                                |  |  |

| NACK NI LA L                                                                                                                                                                                                                                                                                                                                             |                                                |  |  |

| NACK Not Acknowledge                                                                                                                                                                                                                                                                                                                                     |                                                |  |  |

| NAND Not AND                                                                                                                                                                                                                                                                                                                                             |                                                |  |  |

| NIST National Institute of Standards and Technology                                                                                                                                                                                                                                                                                                      | National Institute of Standards and Technology |  |  |

| NOM Nominal                                                                                                                                                                                                                                                                                                                                              | 5,                                             |  |  |

| NOR Not OR                                                                                                                                                                                                                                                                                                                                               |                                                |  |  |

| NTC Negative Temperature Coefficient                                                                                                                                                                                                                                                                                                                     |                                                |  |  |

| NVM Non-Volatile Memory                                                                                                                                                                                                                                                                                                                                  | ,                                              |  |  |

| OOK On/Off Keying                                                                                                                                                                                                                                                                                                                                        |                                                |  |  |

| OP Operation                                                                                                                                                                                                                                                                                                                                             |                                                |  |  |

| OSI Open Systems Interconnection Model                                                                                                                                                                                                                                                                                                                   |                                                |  |  |

| OTP One Time Password                                                                                                                                                                                                                                                                                                                                    |                                                |  |  |

| OUT Output                                                                                                                                                                                                                                                                                                                                               |                                                |  |  |

| PB Petabyte                                                                                                                                                                                                                                                                                                                                              |                                                |  |  |

| PC Personal Computer                                                                                                                                                                                                                                                                                                                                     |                                                |  |  |

| PCB Printed Circuit Board                                                                                                                                                                                                                                                                                                                                |                                                |  |  |

| PDIP Plastic Dual Inline Package                                                                                                                                                                                                                                                                                                                         |                                                |  |  |

| PIR Passive Infrared                                                                                                                                                                                                                                                                                                                                     |                                                |  |  |

| PN Part Number                                                                                                                                                                                                                                                                                                                                           |                                                |  |  |

| PTC Positive Temperature Coefficient                                                                                                                                                                                                                                                                                                                     | Positive Temperature Coefficient               |  |  |

| PTP Picture Transfer Protocol                                                                                                                                                                                                                                                                                                                            | ·                                              |  |  |

| QSPI Quad SPI                                                                                                                                                                                                                                                                                                                                            | Quad SPI                                       |  |  |

| R,G,B Red, Green, Blue                                                                                                                                                                                                                                                                                                                                   | Red, Green, Blue                               |  |  |

| RADAR Radio Detection and Ranging                                                                                                                                                                                                                                                                                                                        |                                                |  |  |

| RAM Random Access Memory                                                                                                                                                                                                                                                                                                                                 |                                                |  |  |

| RC Remote Control                                                                                                                                                                                                                                                                                                                                        |                                                |  |  |

| RDS(on) Resistance from drain to source, when in on state                                                                                                                                                                                                                                                                                                |                                                |  |  |

| RF Radio Frequency                                                                                                                                                                                                                                                                                                                                       |                                                |  |  |

| RFC   | Request for Comments                                    |  |

|-------|---------------------------------------------------------|--|

| RFID  | Radio Frequency Identification                          |  |

| RGB   | Red Green Blue                                          |  |

| RH    | Relative humidity                                       |  |

| RMS   | Root Means Square                                       |  |

| RX    | Receiver or reception                                   |  |

| SAR   | Successive approximative register                       |  |

| SCK   | Serial Clock                                            |  |

| SCL   | Serial Clock                                            |  |

| SD    | Secure Digital                                          |  |

| SDA   | Serial Data                                             |  |

| SDRAM | Synchronous Dynamic Random Access Memory                |  |

| SMD   | Surface Mount Device                                    |  |

| SOIC  | Small Outline Integrated Circuit                        |  |

| SPDT  | Single Pole Double Throw                                |  |

| SPI   | Serial Peripheral Interface                             |  |

| SPST  | Single Pole Single Throw                                |  |

| SQL   | Structured Query Language                               |  |

| SRAM  | Static Random Access Memory                             |  |

| ТВ    | Terabyte                                                |  |

| TCR   | Temperature Coefficient of Resistance                   |  |

| THT   | Through Hole Technology                                 |  |

| TIOBE | The Importance Of Being Earnest                         |  |

| TTL   | Transistor-to-transistor logic                          |  |

| TX    | Transmitter / Transmission                              |  |

| UART  | Universal Asynchronous Receiver/Transmitter             |  |

| UDIMM | Unbuffered Dual In-Line Memory Module                   |  |

| UDP   | User Datagram Protocol                                  |  |

| UHF   | Ultra-High Frequencies                                  |  |

| USART | Universal Synchronous/Asynchronous Receiver/Transmitter |  |

| USB   | Universal Serial Bus                                    |  |

| UV    | Ultraviolet                                             |  |

| V     | Volt                                                    |  |

| VHDL  | VHSIC Hardware Description Language                     |  |

| VHF   | Very High Frequency                                     |  |

| VI    | Input Voltage                                           |  |

| VIH   | Input Voltage (high, minimum)                           |  |

| VIL   | Input Voltage (low, maximum)                            |  |

| VO    | Output Voltage                                          |  |

| VOH   | Output Voltage (high, minimum)                          |  |

| VOL   | Output Voltage (low, maximum)                           |  |

| XOR   | Exclusive OR                                            |  |

|       | 1                                                       |  |

| YB | Yottabyte |

|----|-----------|

| ZB | Zettabyte |

# 1. Brief Introduction to Digital Circuits and Programming

This chapter is similar to the first chapter in [1] and presents an introduction into digital signals and systems. There are advantages of converting analog signals into digital signals and back, otherwise one would not go through the trouble and cost of the conversion. These reasons will be highlighted at the end of this chapter.

#### 1.1 Analog signals

All the studied systems in high-school's physics classes were composed from analog equipment/devices (voltage supplies, current supplies, resistors, capacitors, inductors, lightbulbs etc.). They are circuits where, for example, the voltage varies continuously within some limits. A default system is an analog audio amplifier, which takes an analogue audio signal, amplifies it (keeps the shape, but delivers more power from the supply) and sends it to the speakers. Analogue signals are hard to store and process, so lately, digital signals are used increasingly.

Figure 1. A digital signal (as a result of both sampling and quantization processes)

#### 1.2 Digital signals

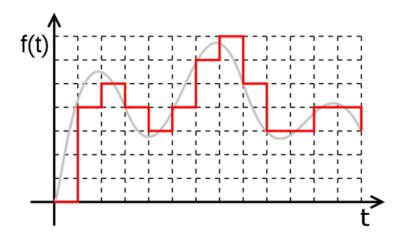

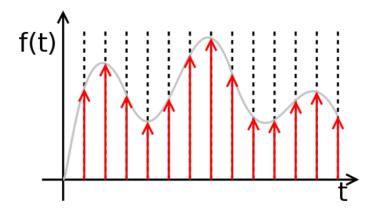

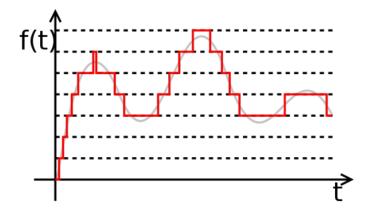

A digital signal is a signal which is discrete (as opposed to continuous) in both time and value. To create a time-discrete signal, one samples a

continuous one. To create a value-discrete signal, one quantizes a continuous one.

The number of samples taken in a unit of time is called sampling rate (e.g., 44100 Hz == samples per second, CD-quality). The number of bits (0 or 1 symbols) required to express the amplitude is linked directly to the number of quantization steps (e.g., 16-bit for 2 to the power of 16 = 65536 steps, in the case of CD-audio quality)

Figure 2. A time-sampled signal (as a result of sampling process)

Figure 3. A value-sampled signal (as a result of quantization process)

Digital signals are used because their expression uses numbers, which allows easy

storage, copying (without loss) and processing. Immunity to noise can be obtained using mathematical instruments like error-detection and error-recovery processes. In addition, the quality (how similar it looks to the source

analogue signal) can be chosen as a compromise. The more quantization steps we use (e.g. infinite) the more accurate the value is to the source signal's value: however, these systems are usually used for the comfort of human life, so the trade-off will take into consideration human hearing or human sight etc. which will not push the quantization step too high (e.g. audio signals are good enough when using 64k steps, that is 16-bits per sample; video signals are good enough when colors are represented with 256 steps of Red, Green and Blue, therefore 3x 8-bits are enough for a pixel). Regarding the recovery of a continuous signal from the time-sampled signal, we have the sampling theorem which demonstrates that we can fully recover the original, as long as the sampling rate is at least twice the maximum frequency contained in the original signal. For example, if one wants to recover up to 22 kHz audio signals (more than what the common human ear can hear), one should use 44 kHz sampling rate.

#### 1.3 Digit, number, and radix

A radix-10 number uses a dictionary of 10 symbols (the ten digits) to express any number. For example, number 123 is made of 1 \* 100 + 2 \* 10 + 3. The radix of 10 is not the only known radix but is the most used by humans (arguably because we have ten fingers and can count easily using them). However, to use radix of 10, one must distinguish between 10 different symbols (0-9). Digital electronics use radix of 2 because it is easier to distinguish between only two symbols, therefore it is easier to store information in this form. The trade-offs that same number expressed in radix of 10 is around 3.5 times shorter that a radix of 2. For example, 9 is expressed in radix 2 with the sequence 1001, the number 127 is 11111111 etc. The symbols available for the radix of 2 are 0 and 1, and they are called Blnary digiTS, in short bits. Using 2 digits we can express numbers from 0 to 99 (that is, 100 different numbers). Using 2 bits we can express numbers from 0 to 3 (that is, 4 different numbers). Most common radices are 2 (binary), 8 (octal), 16 (hex), 10 (dec) and 256. We will mark numbers in radix 2, as prefixed with 0b e.g.: 0b1001 is number 9 in radix 10. The hexadecimal number will be prefixed with 0x e.g.: 0x10 is 16 in radix 10.

Table 1. Multiples of bits / bytes according to JEDEC [3.]. IEC 80000-13 standard changes the name for the power of two, by inserting a "bi" in the name: Kibibyte, Mebibyte, Gibibyte.

| Memory Unit (JEDEC) | Memory unit (IEC) | Description         |

|---------------------|-------------------|---------------------|

| Bit                 | Bit               | Binary Digit 1 or 0 |

| Kbit                | Kibibit           | 1024 bits           |

| Mbit                | Mebibit           | 1024 Kbits          |

| Byte                | Byte            | 8 bits     |

|---------------------|-----------------|------------|

| KiloByte(KB)        | KibiByte (KiB)  | 1024 Bytes |

| MegaByte(MB)        | MebiByte (MiB)  | 1024 KB    |

| GigaByte(GB)        | Gibibyte (GiB)  | 1024 MB    |

| TeraByte(TB)        | Tebibyte (TiB)  | 1024 GB    |

| PetaByte(PB)        | Pebibyte (PiB)  | 1024 TB    |

| HexaByte or exaByte | Exbibyte (EiB)  | 1024 PB    |

| (EB)                |                 |            |

| ZettaByte (ZB)      | Zebibyte (ZiB)  | 1024 EB    |

| YottaByte (YB)      | Yobiibyte (YiB) | 1024 ZB    |

#### 1.4 Digital systems

Digital systems are designed to store and process and exchange information in digital form. They are found in a wide range of applications, including process control, communication systems, digital instruments, and consumer products. These systems/circuits may be classified by the number of appropriate loops enclosed within [5.]; more loops will mean more autonomy, therefore *smarter* circuits.

- 0 loop circuits: contain only combinational circuits (logic gates)

- 1 loop circuits: the memory circuits, with behavioral autonomy in their own internal states; they are mainly used for *storing*

- 2 loops circuits: the automata, with the behavioral autonomy in their own state space, performing mainly the function of *sequencing*

- 3 loops circuits: the processors, with the autonomy in interpreting their own internal states; they perform the function of *controlling*

- 4 loops circuits: the computers, which interpret autonomously the programs according to the internal *data*

n-loop circuits: systems in which the information is interpenetrated with the physical structures involved in processing it; the distinction between *data* and *programs* is surpassed and the main novelty is the *self-organizing* behavior.

Any k-loop circuit can do everything any k-1 loop circuit can do.

While 0 – loop circuits (combinational logic circuits) are quite easy to grasp as they are very simple in structure and behavior, the more evolved circuits, containing sequential circuits (with the clock signal driving them) are the ones used to handle complexity.

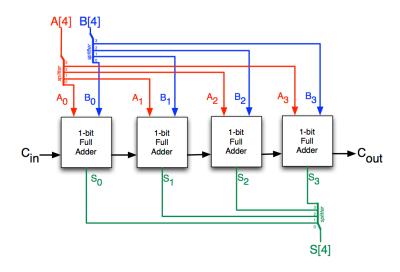

Some common 0-loop circuits are: logic gates, multiplexers (sends the selected digital input to the output), demultiplexers (send the input to the selected output), decoders (sends logic 1 to the selected output), adders, subtractors, ALUs (arithmetical-logical units), equality comparators, magnitude comparators etc.

Some common sequential circuits are flip-flops (FFs), registers, counters/timers, and FSMs.

#### 1.5 The advantages of using digital systems

The world is analog, therefore, interacting with it, using digital systems, implies conversion between analog to digital and back.

Figure 4. Analog to digital conversion, digital processing and digital to analog conversion example

The main advantages of using a digital system:

- Error correction: math (using numbers) can help a lot to find errors and correct them

- Noise tolerance: copy of a copy may be digitally identical, whereas copy of a copy in analog storage is never the same. Keeping numbers

in base2, allows maximum noise immunity as the digital system only has to discriminate between the two possible different symbols. In analog,

- Compression: crunching numbers is possible when

- Modularity: data transfers between digital modules, imply that data processing in a digital system is modular, therefore, there is a high chance of reusability in both hardware modules and software modules. Modular is good as it allows divide-et-impera method of problemsolving.

- Encryption: it is easy to scramble and obfuscate data in other data

- Repeaters: low-cost repeaters and they only have to amplify two symbols accurately (the noise of the repeater can be high)

- Compromise of space & compute power: it can be done in the field, not in the factory. Digital systems are easily configurable to save space and power with acceptable compromises on quality

# 2.The FPGA (Field Programmable Gate Array)

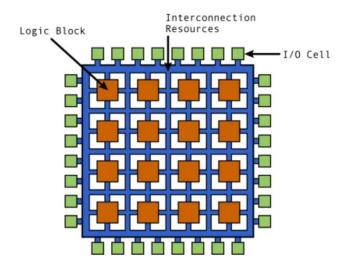

The FPGA is an semiconductor device based on a matrix of reconfigurable logic blocks (CLBs) as seen in Figure 5. The advantage of this device is that it can be reconfigured to emulate any digital circuit of a certain complexity, in the field (not in the factory!). The interconnection can relay signals coming from any direction to signals going towards any direction. The I/O cells allow signals to travel between the FPGA and outer world.

Figure 5. Generic FPGA Architecture Overview

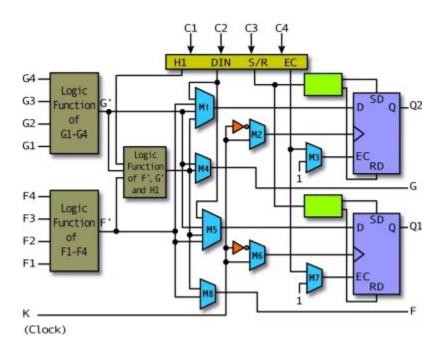

An example of a configurable logic block (CLB) is exemplified below, in Figure 6.

Figure 6. Xilinx CLB. Blue blocks are multiplexers, violet blocks are FFs and dark-green blocks are LUTs (look-up tables)

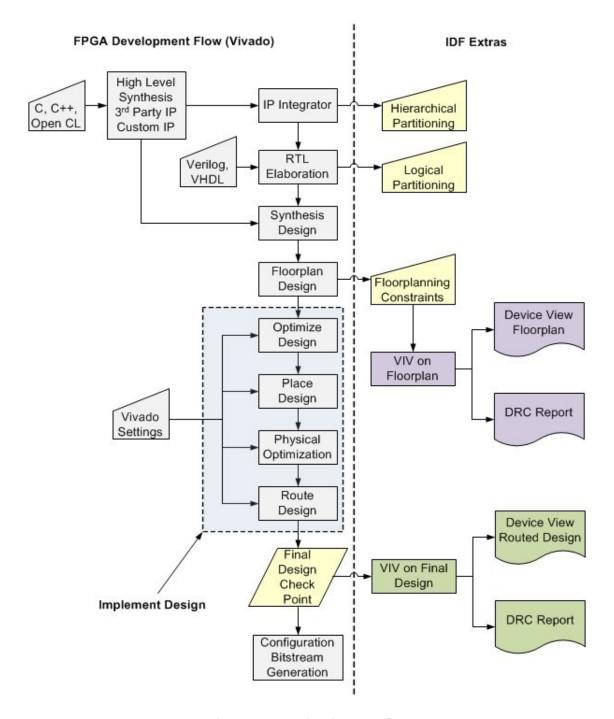

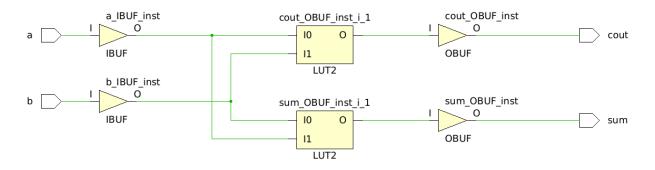

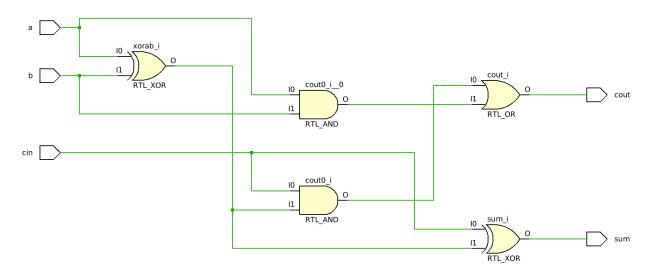

The software tools first convert code into RTL (register-transfer level, a design abstraction which models the synchronous circuit into flow of digital signals between registers and the logical operations performed on them), then from RTL into gates (during synthesis), and then it infers what resources of the FPGA should it use and how to link them in the physical

FPGA device (during implementation). The implementation step is where it matters what specific FPGA chip will be used.

Figure 7. FPGA development flow

Below, there is an FPGA board we will use further, to exemplify digital circuits.

Figure 8. The Nexys 4 DDR FPGA board

| Callout | Component Description                    | Callout                    | Component Description                |  |  |

|---------|------------------------------------------|----------------------------|--------------------------------------|--|--|

| 1       | Power select jumper and battery header   | 13                         | FPGA configuration reset button      |  |  |

| 2       | Shared UART/ JTAG USB port               | 14                         | CPU reset button (for soft cores)    |  |  |

| 3       | External configuration jumper (SD / USB) | 15                         | Analog signal Pmod port (XADC)       |  |  |

| 4       | Pmod port(s)                             | 16 Programming mode jumper |                                      |  |  |

| 5       | Microphone                               | 17                         | Audio connector                      |  |  |

| 6       | Power supply test point(s)               | 18                         | VGA connector                        |  |  |

| 7       | LEDs (16)                                | 19                         | FPGA programming done LED            |  |  |

| 8       | Slide switches                           | 20                         | Ethernet connector                   |  |  |

| 9       | Eight digit 7-seg display                | 21                         | USB host connector                   |  |  |

| 10      | JTAG port for (optional) external cable  | 22                         | PIC24 programming port (factory use) |  |  |

| 11      | Five pushbuttons                         | 23                         | Power switch                         |  |  |

| 12      | Temperature sensor                       | 24                         | Power jack                           |  |  |

Figure 9. Nexys 4 DDR board features

Figure 10. GPIO devices on the Nexys4 DDR FPGA board

### 2. Zero-loop systems

#### 2.1 Prerequisites

#### 2.1.1 Binary and Boolean Logic

Boolean algebra is a branch of algebra, where the values of the variables are truth values (true and false) usually coded as 1 and 0 and uses logical operators such as AND (conjunction), OR (disjunction), NOT (negation). It was introduced by English mathematician George Boole in the book "The Mathematical Analysis of Logic" in 1847.

A logical operation is a function of two variables and may be expressed using a truth table as below:

| Α     | В     | OP (A, |

|-------|-------|--------|

|       |       | B)     |

| FALSE | FALSE | ?      |

| FALSE | TRUE  | ??     |

| TRUE  | FALSE | ???    |

| TRUE  | TRUE  | ????   |

Table 2. A (general) logic operation's truth table

There are 16 dual-input single-output logical operations, 3 of which are most used (hence named). The 16 number comes from the output: there are 4 bits of 0 or 1 (one for every combination of A and B), therefore, there are 16 different output configurations => 16 different gates. Their truth table is as below:

Table 3. Truth tables for AND, OR and NOT operations

| А         | В         | A and<br>B | A or B | Not A |

|-----------|-----------|------------|--------|-------|

| FALS<br>E | FALS<br>E | FALSE      | FALSE  | TRUE  |

| FALS<br>E | TRUE      | FALSE      | TRUE   | TRUE  |

| TRU<br>E  | FALS<br>E | FALSE      | TRUE   | FALSE |

| TRU       | TRUE      | TRUE       | TRUE   | FALSE |

Table 4. Truth tables for AND, OR and NOT operations (seen as 1-bit operations)

| Α | В | A and | A or B | Not A |

|---|---|-------|--------|-------|

|   |   | В     |        |       |

| 0 | 0 | 0     | 0      | 1     |

| 0 | 1 | 0     | 1      | 1     |

| 1 | 0 | 0     | 1      | 0     |

| 1 | 1 | 1     | 1      | 0     |

#### 2.1.2 Digital Gates

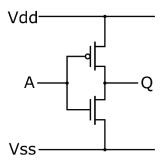

The electronic circuits used to implement Boolean logic are the logical gates. Nowadays, all gates are made of transistors (a semiconductor device used to amplify or switch electrical signals and power). For example, the NOT gate is made of two CMOS transistors (a p-channel and n-channel MOS transistor), as seen in Figure 4 below.

Figure 11. NOT gate ("inverter") made of one pMOS (top) and one nMOS (bottom) transistor.

Vdd is usually at least 1.8V over Vss, and Vss is usually ground. When A is "low," pMOS transistor conducts current and draws Q close to Vdd ("high") whereas nMOS is not conducting. When A is "high" level, nMOS conducts and ties Q to the Vss level ("low").

Engineers use the symbols of such gates, in logic schematics; these symbols, are ratified by international standards as seen in Figure 5.

| ANSI Symbol                            | IEC Symbol | NAME |

|----------------------------------------|------------|------|

| A————————————————————————————————————— | А — & — x  | AND  |

| А————X                                 | A21x       | OR   |

| A—————X                                | A & X      | NAND |

| А—<br>В————X                           | A≥1x       | NOR  |

| А—)                                    | A =1 _x    | XOR  |

| А—)х                                   | A =1 x     | XNOR |

| A                                      | A          | NOT  |

Figure 12. ANSI / IEC [6.] (right) and MIL-STD-806B [7.] (left) symbols foremost common 7/16 dual-input logic gates (elementary), with their names.

Figure 13. The truth tables for the most commonly used logic gates.

All the 2-input gates are called elementary (or basic) gates. Similarly, for all circuits that are expressed in a iterative or recursive way, the very first instance is called "elementary".

NOR and NAND gates are called universal gates, because all other 2-input gates (and therefore, N-input gates) may be implemented using any one of them. For example:

- One NOT gate may be made of one NOR or NAND where both inputs are tied from the same NOT input.

- One AND gate is made of NAND + AND, so three NAND gates are enough.

- One OR gate is made of NOR + NOT, so three NOR gates are enough.

- XOR gate is made of one NAND, one NOT and one AND gate.

Last, a NAND gate may be transformed into NOR and vice versa, by using DeMorgan:

NOT (A OR B) = NOT(A) AND NOT(B) NOT (A AND B) = NOT(A) OR NOT(B)

#### 2.1.3 Voltage levels (VI / VO)

Table 5. Recommended operating conditions for 54HC595 / 74HC595 ICs (a common 74HCxx circuit)

|                                                                         |                                |                         | SN   | SN54HC595 |      |      | SN74HC595 |      |      |

|-------------------------------------------------------------------------|--------------------------------|-------------------------|------|-----------|------|------|-----------|------|------|

|                                                                         |                                |                         | MIN  | NOM       | MAX  | MIN  | NOM       | MAX  | UNIT |

| V <sub>CC</sub>                                                         | Supply voltage                 |                         | 2    | 5         | 6    | 2    | 5         | 6    | V    |

|                                                                         |                                | V <sub>CC</sub> = 2 V   | 1.5  |           |      | 1.5  |           |      |      |

| V <sub>IH</sub>                                                         | High-level input voltage       | V <sub>CC</sub> = 4.5 V | 3.15 |           |      | 3.15 |           |      | ٧    |

|                                                                         |                                | V <sub>CC</sub> = 6 V   | 4.2  |           |      | 4.2  |           |      |      |

|                                                                         | oli.                           | V <sub>CC</sub> = 2 V   |      |           | 0.5  |      |           | 0.5  | V    |

| V <sub>IL</sub> Low-level input voltage                                 | Low-level input voltage        | V <sub>CC</sub> = 4.5 V |      |           | 1.35 |      |           | 1.35 |      |

|                                                                         |                                | V <sub>CC</sub> = 6 V   |      |           | 1.8  |      |           | 1.8  |      |

| VI                                                                      | Input voltage                  |                         | 0    |           | Vcc  | 0    |           | Vcc  | V    |

| Vo                                                                      | Output voltage                 |                         | 0    |           | Vcc  | 0    |           | Vcc  | ٧    |

| $\Delta t / \Delta v$ Input transition rise or fall time <sup>(2)</sup> |                                | V <sub>CC</sub> = 2 V   |      |           | 1000 |      |           | 1000 |      |

|                                                                         | V <sub>CC</sub> = 4.5 V        |                         |      | 500       |      |      | 500       | ns   |      |

|                                                                         |                                | V <sub>CC</sub> = 6 V   |      |           | 400  |      |           | 400  |      |

| TA                                                                      | Operating free-air temperature | *                       | -55  |           | 125  | -40  |           | 85   | °C   |

Figure 14. Voltage levels: output requirements vs. input requirements.

- High state/Logic 1:  $V_0 > V_{OH}$  ( $V_{OH}$  is minimum output voltage for state HIGH or logic 1)

- Low state/Logic 0:  $V_0 < V_{OL}$  ( $V_{OL}$  is maximum output voltage for low/0 state)

- High state/Logic 1:  $V_I > V_{IH}$  ( $V_{IH}$  is minimum voltage interpreted as logic high/1)

- Low state/Logic 0:  $V_1 < V_{1L}$  ( $V_{1L}$  is maximum voltage interpreted as logic low/0)

- "Noise Margin"- allows logic level to be correct even if some voltage variation occurs

- High state/Logic 1:  $V_{OH} = V_{IH} + V_{IDISE}$  (noise does not pull voltage below threshold)

- Low state/Logic 0:  $V_{OL} = V_{IL}$  Vnoise (noise does not pull voltage above threshold)

In digital design vocabulary, a driver is similar in function to an electrical driver: it just amplifies the current (keeps the voltage the same, therefore, keeps the logic value on the output, similar to input)

#### 2.1.4 Logic gates components

The logic gates may be composed of various devices depending on the field used in. First ones were mechanical, then electro-mechanical, and nowadays electronic. One common implementation in electronics is with MOSFET transistors.

Figure 15. MOSFET implementations of common logic gates. Left (NOT), middle (NAND), and right (NOR)

Regarding the size in MOS transistors we have:

- NOT gate, made of 2 transistors

- NAND, NOR gates made of 4 transistors

- AND, OR gates made of 6 transistors (NAND/NOR + NOT)

- XOR gate made of 8 transistors

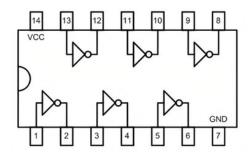

Logic gates are still available as integrated circuits using the 74xx family, for example the 74HC00 implements 6x NOT gates in one DIP14 or SOIC14 package (6 inputs, 6 outputs, one Vcc and one GND). There are circuits for all common 2-input gates (74HC00 for NAND, 74HC02 for NOR) and common 3-input gates (74HC10 for NAND, 74HC11 for AND).

Figure 16. The 74HC04 hex-inverter circuit

#### 2.1.5 Complexity in digital circuits

A complex circuit is a circuit that has spatial complexity (structure) or behavior complexity or a combination of the two.

To express spatial complexity, two metrics are used:

- the SIZE (S) of the circuit (the number of elementary gates)

- the DEPTH (D) of the circuit (the largest number of elementary gates passed through, when the signal goes from any input to any output)

An elementary gate (2-input, 1-output) has the S = 1 and D = 1.

#### 2.1.6 Complexity classes

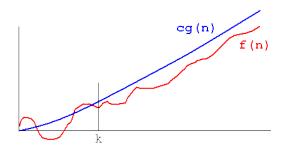

A more in-depth talk on complexity for algorithms may be found in [941.], below is an extract of how complexity applies to circuits. Complexity is usually expressed as Big-O notation. The complexity of a function f is decided by finding another function g, which asymptotically bounds the f function.

Mathematically, this is expressed as: if f(n) has the same complexity as g(n), then from n = k onwards, the c\*g(n) >= f(n), where k is a point < infinity and c is a constant

Figure 17. Representing a g(n) function which asymptotically bound f(n) function.

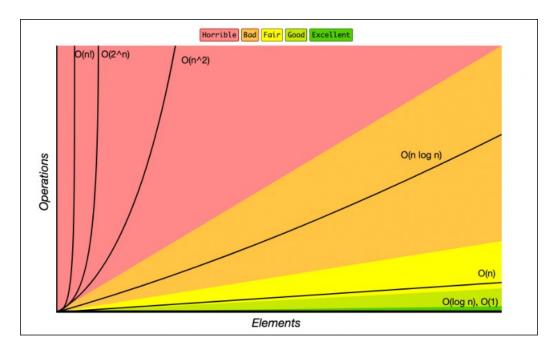

To learn more about Big-Oh, Big-Theta and Big-Omega and their small variants, see [10.10.]. A list of common complexity classes is listed below. O(1) means constant time, and is the best one can hope for: the algorithm runtime will not increase with data increase, the circuit will not increase its size no matter the number of inputs etc.

Figure 18. The O-notation complexity increases with the number of elements processed. O(1) and O(logn) are usually excellent complexities, O(n) is fair, and O(n\*logn) is usually considered almost decent in algorithms and circuits

To better understand the complexity difference between O(logN) and O(N) we propose the next game: one thinks at a number from 0 to 100. Assuming another one tries to guess the number, with hints of "my number is higher" or "my number is lower":

in O(N) algorithm (brute forcing all values) one will guess in at most 100 steps

• whereas in O(logN) algorithm, same task will take at most 7 steps (assuming log2).

This is not very impressive, but as one goes further (towards infinity), the advantage will become obvious. Assume the same game, but with numbers from 0 to 4 billion:

- in O(N) algorithm it will take at most 4 billion steps

- whereas in O(logN) it will take at most 32 steps!

This is the power of the logarithm: it goes to infinity with N going to infinity, but much slower.

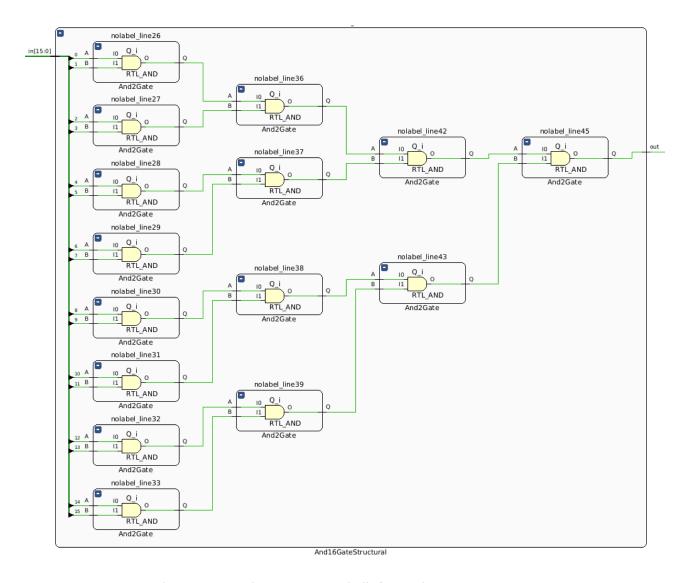

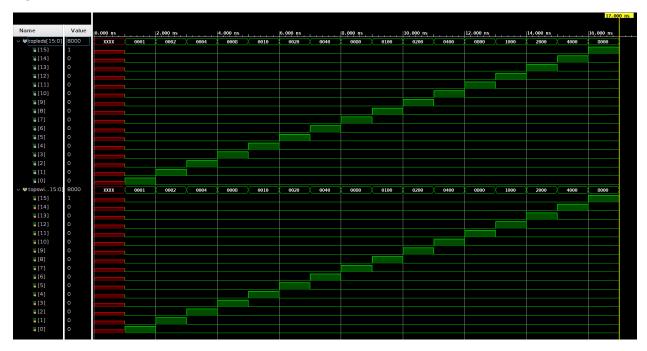

To better understand how this applies to circuits, imagine an N-input AND gate, implemented with N-1 elementary gates, arranged in logN layers as below:

Figure 19. A 16-input AND gate built from 2-input AND gates.

It is quite common to have a logN depth (and acceptable); a size of O(N) is also fair. There are circuits that can implement any logic function (eg. a decoder to output all minterms + specific AND gates to combine the specific minters) however, the price paid is 2\*\*N size or even worse, N\*2\*\*N size: this is why the process of minimization (expressing the same logic function with as few number of elementary gates, as possible) is a mandatory study in this field. Fortunately, for most common circuits, the synthesis toolchain will take care of that, but applying an optimization step after inferring the logic function from the behavioral description.

#### 2.1.7 Verilog syntax

S. Winberg and J. Taylor [9.] summarized the most important syntax features of Verilog language in their cheat sheet:

```

Comments

Operators

// One-liner

// These are in order of precedence...

/* Multiple

// Select

A[N] A[N:M]

lines */

// Reduction

&A ~&A |A ~|A ~A ~^A

Numeric Constants

// Compliment

// The 8-bit decimal number 106:

!A ~A

8'b_0110_1010 // Binary

// Unary

8'o_152 // Octal

+A -A

8'd_106

// Decimal

// Concatenate

// Hexadecimal

8'h_6A

\{A, \ldots, B\}

"j"

// ASCII

// Replicate

\{N\{A\}\}

78'bZ

// 78-bit high-impedance

// Arithmetic

A*B A/B A%B

A+B A-B

Too short constants are padded with zeros

// Shift

on the left.

Too long constants are

A<<B A>>B

truncated from the left.

// Relational

A>B A<B A>=B A<=B

Nets and Variables

A==B A!=B

wire [3:0]w; // Assign outside always blocks

// Bit-wise

reg [1:7]r; // Assign inside always blocks

A&B

reg [7:0]mem[31:0];

A^B A~^B

AB

integer j; // Compile-time variable

// Logical

genvar k; // Generate variable

A&&B

AIIB

// Conditional

Parameters

A ? B : C

parameter N

= 8;

localparam State = 2'd3;

Module

module MyModule

Assignments

#(parameter N = 8) // Optional parameter

assign Output = A * B;

(input Reset, Clk,

assign \{C, D\} = \{D[5:2], C[1:9], E\};

output [N-1:0]Output);

// Module implementation

endmodule

Module Instantiation

// Override default parameter: setting N = 13

```

Figure 20. Verilog syntax cheat sheet (1/2)

MyModule #(13) MyModule1(Reset, Clk, Result);

```

Case

Generate

always @(*) begin

genvar j;

case(Mux)

wire [12:0]Output[19:0];

2'd0: A = 8'd9;

2'd1,

generate

2'd3: A = 8'd103;

for(j = 0; j < 20; j = j+1)

begin: Gen_Modules

2'd2: A = 8'd2;

default:;

MyModule #(13) MyModule_Instance(

Reset, Clk,

endcase

end

Output[j]

);

always @(*) begin

end

casex(Decoded)

endgenerate

4'b1xxx: Encoded = 2'd0;

4'b01xx: Encoded = 2'd1;

State Machine

4'b001x: Encoded = 2'd2;

reg [1:0]State;

4'b0001: Encoded = 2'd3;

localparam Start = 2'b00;

default: Encoded = 2'd0;

localparam Idle = 2'b01;

endcase

localparam Work = 2'b11;

end

localparam Done = 2'b10;

Synchronous

reg tReset;

always @(posedge Clk) begin

always @(posedge Clk) begin

if(Reset) B <= 0;

else B <= B + 1'b1;

tReset <= Reset;

end

if(tReset) begin

State <= Start;

Loop

always @(*) begin

end else begin

Count = 0;

case(State)

for(j = 0; j < 8; j = j+1)

Start: begin

Count = Count + Input[j];

State <= Idle;

end

end

Idle: begin

State <= Work;

Function

end

function [6:0]F;

Work: begin

input [3:0]A;

State <= Done;

input [2:0]B;

begin

Done: begin

F = \{A+1'b1, B+2'd2\};

State <= Idle;

end

end

endfunction

default:;

endcase

end

end

```

Figure 21. Verilog syntax cheat sheet (2/2)

#### 2.1.7 VHDL syntax

```

GRAY_ITALICS represent user-defined names or operations keywords

Purple constructs are only available in VHDL 2008.

literals (constants)

-- This is a comment

/* Multi-line comment

(VHDL 2008 only) */

library IEEE;

You almost always need these libraries;

use IEEE.std logic 1164.all;

just put this at the top of every file.

use IEEE.numeric_std.all;

entity ENTITY_NAME is

port(

PORT_NAME : in std_logic; -- Single bit input

ANOTHER : out std_logic_vector(3 downto 0) -- 4-bit output

No semicolon on the last one! '

Don't forget these semicolons!

architecture ARCH_NAME of ENTITY_NAME is

-- Component declarations, if using submodules

port(

and put 'end component' at the end.

-- Port list for the entity you're including

);

Instantiate a submodule

end component;

INSTANCE_NAME : MODULE_NAME

-- Signal declarations, if using intermediate signals

generic map (

signal NAME : TYPE;

GENERIC => CONSTANT,

-- Architecture definition goes here

port map(

end;

PORT => VALUE.

ANOTHER => LOCAL_SIGNAL

);

Continuous assignments

RESULT_SIGNAL <= SIGNAL1 and SIGNAL2; Also works for or, not, nand, nor, xor

RESULT_SIGNAL <= '1' when (SIGNAL1 = x"5") else '0'; Note'=' for comparison (not'==')

HIGHEST_BIT <= EIGHT_BIT_VEC(7); Extract a single bit (7 is MSB, 0 is LSB)</pre>

TWO_BIT_VEC <= EIGHT_BIT_VEC(3 downto 2); Extract multiple bits

SIX_BIT_VEC <= "000" & EIGHT_BIT_VEC(3 downto 2) & SINGLE_BYTE; Concatenate

Literals

Types

'0', '1', 'X', 'Z'

std_logic Basic logic type, can take values 0, 1, X, Z (and others)

"00001010", x"0c" 8-bit binary, hex

std_logic_vector (n downto m) Ordered group of std_logic

unsigned (n downto m)

Like std_logic_vector, but preferred

9x"101"

3b"101"

7d"101"

for numerically meaningful signals

9-bit hex

3-bit binary 7-bit decimal

signed (n downto m)

integer Poor for synthesis, but constants are integers by default

5, 38, 10000000

Type conversion

to_unsigned(INTEGER, WIDTH)

Use to_unsigned for unsigned constants before VHDL 2008.

unsigned(LOGIC_VECTOR)

(Same things for signed)

std_logic_vector(UNSIGNED)

```

Figure 22. VHDL cheat sheet (1/2)

```

Process blocks

If sensitivity includes:

process (SENSITIVITY) is

all $ ── Combinational logic

Specify all signals by name prior to

VHDL 2008

clk↑ → Flip-flop / register

-- if/case/print go here

end process;

Nothing ----- Testbench (repeated evaluation)

Something else → Bad things you probably didn't want

Reporting stuff

assert CONDITION report "MESSAGE" severity error; Print message if condition is false

report "MESSAGE" severity error;

Severity can be NOTE, WARNING, ERROR, FATAL

"FATAL" ends the simulation

report "A is " & to_string(a);

Use image function prior to VHDL 2008

report "A in hex is "_& to_hstring(a);

concatenation conversion to string

Writing to files (or stdout)

variable BUF: line; Declare buffer in process block

write(BUF, string'("MESSAGE")); Append message to buffer

writeline(output, BUF); Write buffer to stdout (like report, but just the text)

file RESULTS: text; Declare file handle in process block

file_open(RESULTS, "FILENAME", WRITE_MODE);

writeline(RESULTS, BUF);

If/else

Case

if CONDITION then

case INPUT_SIGNAL is

SIGNAL <= VALUE1;

when VALUE1 => OPERATION1;

elsif OTHER CONDITION then

when VALUE2 => OPERATION2;

SIGNAL <= VALUE2; Note spelling

when others => DEFAULT;

of "elsif"!

end case;

SIGNAL <= VALUE3;

end if;

For loop

Sequential logic

for INDEXVAR in MIN to MAX loop

-- loop body here

process (CLOCK) is

end loop;

begin

if rising_edge(CLOCK) then

To count down:

-- Clocked assignments go here

end if;

for INDEXVAR in MAX downto MIN loop

end process;

Enumerated types

type TYPENAME is (VAL1, VAL2, VAL3);

signal NAME: TYPENAME; Just like any other type

```

Figure 23. VHDL cheat sheet (2/2)

### 2.1.8 Simulation

The simulation is

### 2.1.9 Our first digital circuit – the switch tester

Usually, dev-board switches are of poor quality, therefore, before using them, one might check the state of the switches (whether they are always on or off, hence malfunctioning). The circuit would be driver at the input, driver at the output, such that the on or off state of each switch can be monitored on a correspondent led:

Figure 24. The schematic of a switch checker

A simulation where each switch is switched on then off, should look like the figure below:

The Verilog and VHDL implementation are as follows:

```

[Digital] Electronics by Example: When Hardware Greets Software

```

```

module top(output [15:0]LED, input [15:0]SW);

assign LED = SW;

endmodule

Figure 25. Verilog description of switch-checker

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity top is

Port (SW: in STD_LOGIC_VECTOR (15 downto 0);

LED: out STD_LOGIC_VECTOR (15 downto 0));

end top;

architecture Behavioral of topis

begin

LED <=SW;

end Behavioral;

Figure 26. VHDL description of switch-checker

// TODO: Verilog simulation / VHDL?

```

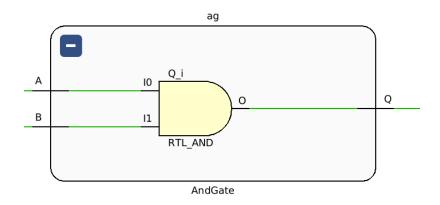

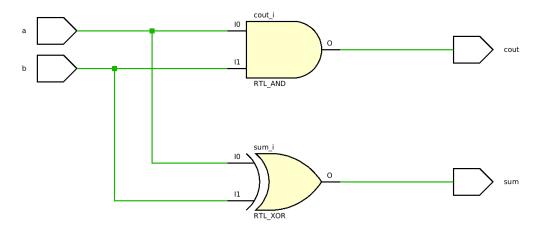

To express the AND gate behavior in Figure 27 one has to write in Verilog the code or VHDL code below.

Figure 27. 2-input AND gate

module AndGate(input A, input B, output Q);

```

assign Q = A & B;

```

endmodule

Figure 28. Verilog code (dataflow) for a 2-input AND gate

```

library IEEE;

use IEEE.std_logic_1164.all;

- Entity declaration

entity and Gate is

port(A: in std_logic; — AND gate input

B: in std_logic; — AND gate input

Q: out std_logic); — AND gate output

end and Gate;

- Dataflow Modelling Style

- Architecture definition

architecture and Logic of and Gate is

begin

Q ←A AND B;

end and Logic;

```

Figure 29. Verilog code (dataflow) for a 2-input AND gate

### 2.2 Theory & Exercises

### 2.2.1 Multiple-input gates

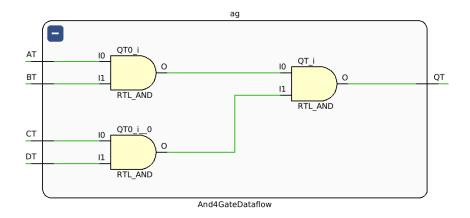

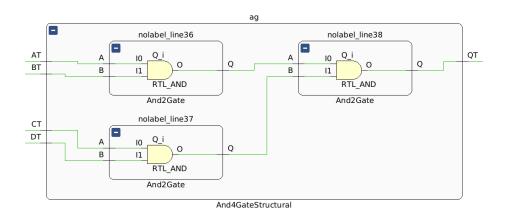

Using only elementary (2-input) gates, create a 4-input AND gate. Write code in both dataflow and structural manner. Describe the circuit in both in Verilog and VHDL language.

Figure 30. 4-input AND gate from 2-input AND gates (dataflow)

module And4GateDataflow(input AT, input BT, input CT, input DT, output QT); assign QT =AT & BT & CT & DT; endmodule

Figure 31. Verilog description for 4-input AND (dataflow)

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity And4Gate is

Port (AT: in STD_LOGIC;

BT: in STD_LOGIC;

CT: in STD_LOGIC;

DT: in STD_LOGIC;

QT: out STD_LOGIC);

end And4Gate;

architecture and4Logic of And4Gate is begin

QT ←AT AND BT AND CT AND DT;

end and4Logic;

```

Figure 32. VHDL description for 4-input AND (dataflow)

Figure 33. 4-input AND gate from 2-input AND gates (structural)

[Digital] Electronics by Example: When Hardware Greets Software

module And2Gate(input A, input B, output Q);

assign Q =A & B;

endmodule

module And4GateStructural(input AT, input BT, input CT, input DT, output QT);

wire ABT;

wire CDT;

And2Gate(.A(AT), .B(BT), .Q(ABT));

And2Gate(.A(CT), .B(DT), .Q(CDT));

Figure 34. Verilog description of 4-input AND gate from 2-input AND gates (structural)

A few notes here: assuming N is power of 2, the number of elementary gates for an N-input AND or OR gate is a having log2 N layers each with half of the number of gates or previous layer. For example, an 16-input AND gate requires 4 layers having the N-1 gates, distributed as follows:

- Layer 1: 8 elementary gates (all 16 inputs go into the inputs of the first layer)

- Layer 2: 4 elementary gates

And2Gate(.A(ABT), .B(CDT), .Q(QT));

endmodule

- Layer 3: 2 elementary gates

- Layer 4: 1 elementary gate (which gives the output of the circuit)

Therefore, the SIZE of the circuit is O(N), and the DEPTH of the circuit is O(log N)

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity And4Gate is

Port (AT: in STD_LOGIC;

BT: inSTD LOGIC;

CT: inSTD LOGIC;

DT: inSTD LOGIC;

QT: out STD_LOGIC);

end And4Gate;

architecture and 4LogicStructural of And 4Gate is

component And2Gate

port(A, B: in std_logic;

Q: out std logic);

end component;

signal and1_to_and3: std_logic;

signal and2_to_and3: std_logic;

begin

and1: And2Gate port map(AT, BT, and1_to_and3);

and2: And2Gate port map(CT, DT, and2_to_and3);

and3: And2Gate port map(and1_to_and3, and2_to_and3, QT);

end and 4Logic Structural;

```

Figure 35. VHDL description of 4-input AND gate from 2-input AND gates (structural)

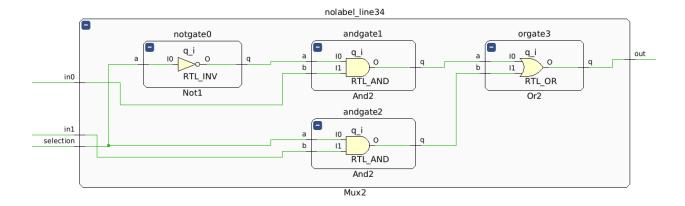

### 2.2.2 Elementary multiplexer

A multiplexer is a circuit that outputs one of its inputs, depending on the selection. The elementary multiplexer is draws as follows:

Figure 36. MUX2 implemented with one NOT, two AND, one OR gate(s)

The implementation post-synthesis is done with one LUT, as shown in the

Figure 37. LUT-based implementation of elementary mux, in FPGA

```

module And2(output q, input a, input b);

assign q = a \& b;

endmodule

module Or2(output q, input a, input b);

assign q = a \mid b;

endmodule

module Not1(output q, input a);

assign q = \sim a;

endmodule