Diferență între revizuiri ale paginii „Introducere în sinteza pe FPGA. Xilinx ISE”

| (Nu s-au afișat 20 de versiuni intermediare efectuate de același utilizator) | |||

| Linia 21: | Linia 21: | ||

# Sinteza - este etapa în care codul Verilog este interpretat de programul de sinteză care generează din el un circuit (ansamblul de porți și registre) ce poartă denumirea de '''netlist'''; această etapă este independentă de modelul de FPGA cu care se lucrează; | # Sinteza - este etapa în care codul Verilog este interpretat de programul de sinteză care generează din el un circuit (ansamblul de porți și registre) ce poartă denumirea de '''netlist'''; această etapă este independentă de modelul de FPGA cu care se lucrează; | ||

| − | # Implementare - etapa în care se | + | # Implementare - etapa în care se translatează circuitul la nivel de poartă (netlist) în circuitul la nivel de elemente disponibile pe cipul FPGA utilizat; în mod evident, acestă etapă depinde de modelul de FPGA utilizat; |

# Generare a fișierului de programare - din circuitul de la punctul anterior, se generează un fișier cu extensia '''.bit''' care conține biții de configurare pentru blocurile logice, blocurile de I/O și blocurile de interconectare corespunzătoare circuitului dorit; | # Generare a fișierului de programare - din circuitul de la punctul anterior, se generează un fișier cu extensia '''.bit''' care conține biții de configurare pentru blocurile logice, blocurile de I/O și blocurile de interconectare corespunzătoare circuitului dorit; | ||

# Programarea dispozitivului - etapa în care, printr-o interfață [http://en.wikipedia.org/wiki/Jtag JTAG], se încarcă fișierul '''.bit''' în memoria SRAM a FPGA-ului, configurând astfel dispozitivul. | # Programarea dispozitivului - etapa în care, printr-o interfață [http://en.wikipedia.org/wiki/Jtag JTAG], se încarcă fișierul '''.bit''' în memoria SRAM a FPGA-ului, configurând astfel dispozitivul. | ||

| + | |||

| + | |||

| + | '''Atenție:''' Modulele de test NU se folosesc în pentru sinteză! Prin urmare un modul de test nu trebuie să apară în Xilinx, ci doar în Modelsim! | ||

| + | |||

| + | == Configurarea I/O-ului == | ||

| + | |||

| + | === Legături externe === | ||

| + | [[Fișier:fpga4.png|thumb|Dispozitive de IO legate la pinii FPGA-ului]] | ||

| + | |||

| + | Dispozitivele de I/O (input - output) sunt legate în exteriorul cipului de FPGA la câte un pin. Fiecare din acești pini are un nume cunoscut de programul de sinteză. Aceste nume diferă de la un model de FPGA la altul. În figura dată ca exemplu, la pinul cu numele "P88" al FPGA-ului este legat un comutator (switch - SW0) care este un dispozitiv de intrare, iar la pinul "P45" este legat un led (LD0), care este un dispozitiv de ieșire. Aceste legături sunt realizate fizic la producerea plăcilor și nu pot fi modificate. Prin urmare, de cele mai multe ori, în dreptul fiecărui dispozitiv de pe o placă de dezvoltare este trecut în paranteză index-ul sau numele pinului FPGA-ului la care acesta este legat. | ||

| + | |||

| + | Pentru placa de dezvoltare Pegasus, în dreptul fiecărui dispozitiv este trecut index-ul pinului. Ca exemplu, lângă switch-ul '''SW0''' este trecut în paranteză numărul '''(89)'''. În acest caz, numele complet al pinului, în momentul realizării legăturilor interne în FPGA este '''P89'''. Analog pentru toate dispozitivele de pe placă. | ||

| + | |||

| + | Pentru placa de dezvolatare FPGA Spartan-3 Starter Board, în dreptul fiecărui dispozitiv este trecut chiar numele pinului. Ca exemplu, lângă switch-ul '''SW0''' este trecut în paranteză '''(F12)''', care este chiar numele pinului. Analog pentru toate dispozitivele de pe placă. | ||

| + | |||

| + | === Legături interne === | ||

| + | |||

| + | Legăturile interne reprezintă conexiunile logice dintre '''fiecare bit''' al porturilor modulului principal, și pinii FPGA-ului. Aceste legături fac posibilă conectarea dispozitivelor externe de pe placa de dezvoltare la modului Verilog definit de utilizator. Spre exemplu, dacă placa FPGA este configurată cu un sumator pe 4 biți, atunci vom vrea ca fiecare bit al porturilor de intrare să fie legat la câte un switch, și fiecare bit al portului de ieșire să fie legat la câte un led, sau la alt dispozitiv de ieșire. Aceste legături nu sunt permanente, prin urmare la fiecare configurare a plăcii, aceste legături trebuie specificate programului de sinteză, înaintea etapei de implementare. Specificațiile legăturilor se dau într-un fișier numit '''"Implementation Constraints File"''', care trebuie să fie adăugat la proiectul ISE, și care are următoarea sintaxă: | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | net "in0[0]" loc = "P88"; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | Această linie exprimă faptul că bitul 0 (cel mai puțin semnificativ) al portului '''in0''' (care în cazul modulului Adder este o intrare), este legat intern la pinul '''P88''', care în cazul plăcii Pegasus, este legat mai departe extern la switch-ul SW0. | ||

| + | |||

| + | '''Observație:''' Analog limbajului Verilog, dacă portul are un singur bit, index-ul acestuia lipsește: | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | net "port_de_un_bit" loc = "P88"; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <div class="regula"> | ||

| + | <font color="red">Regulă:</font> Pentru fiecare bit al fiecărui port al modulului principal, în fișierul de constrângeri trebuie să apară câte o linie, unde acesta este legat la dispozitivul dorit de pe placă. | ||

| + | </div> | ||

| + | |||

| + | Intrările în Verilog se definesc cu cuvântul ''input', ieşirile sunt ''output''. | ||

| + | Orice modul începe cu cuvântul ''module'' şi se termină cu ''endmodule''. Modulele nu se pot suprapune şi nu pot fi incluse unele în altele. | ||

== Xilinx ISE == | == Xilinx ISE == | ||

| Linia 32: | Linia 69: | ||

În laboratorul de CID puteți lucra cu una din următoarele plăci de dezvoltare: | În laboratorul de CID puteți lucra cu una din următoarele plăci de dezvoltare: | ||

| − | * | + | * [[Pegasus]] |

| − | * | + | * [[Spartan 3 Starter Board]] |

| − | * Nexys 2 | + | * [[Nexys 2]] |

Pentru toate plăcile disponibile, codul modelului ca și codul pachetului sunt scrise direct pe cip. | Pentru toate plăcile disponibile, codul modelului ca și codul pachetului sunt scrise direct pe cip. | ||

Versiunea curentă din 16 februarie 2014 18:50

FPGA (Field Programmable Gate Array)

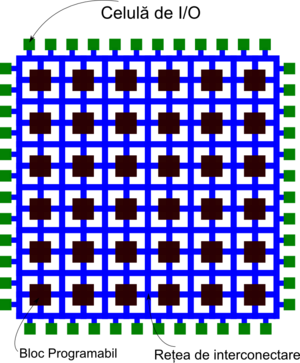

Circuitul FPGA (Field Programmable Gate Array) este un circuit generic ce poate fi programat pentru a implementa orice funcție definită de utilizator. Un FPGA este constituit dintr-o matrice de blocuri programabile, o rețea de interconectare care leagă aceste blocuri între ele, circuite de I/O și o memorie SRAM care configurează aceste structuri. Figura alăturată prezinta o schema simplificata de FPGA.

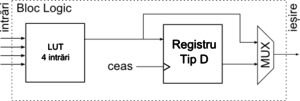

Blocurile programabile pot fi generatoare de funcții logice, memorii RAM, sau circuite de înmulțire. În figură este prezentată structura unui bloc generator de funcții logice. Acesta este format dintr-un LUT (Look-Up Table) și un registru pentru a sincroniza ieșirea acestuia, dacă se dorește acest lucru. Un LUT poate implementa orice funcție logică de 4 variabile cu ajutorul unui selector. Fiecare combinație de valori ale variabilelor de intrare selectează rezultatul corespunzător, calculat în prealabil de programul de sinteză și stocat în memoria de configurație la programarea FPGA-ului. Ieșirea generatorului de funcții logice poate fi legată fie la registru, fie direct la ieșirea LUT-ului.

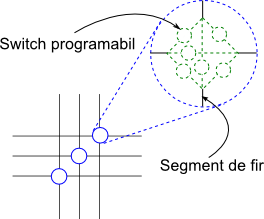

Fiecare bloc programabil este legat la rețeaua de interconectare. Aceasta este formată din segmente de fire și comutatoare programabile. Fiecare comutator poate lega două sau mai multe segmente între ele, asa cum se poate observa în figură. Starea comutatoarelor (on/off) este deasemenea determinată în prealabil în etapa de Place and Route, și stocată în memoria de configurație.

Etapele de sinteză

Când se dorește programarea unui FPGA cu un circuit nou, acesta urmează o serie de proceduri care îl transformă din cod de descriere hardware (Verilog, VHDL, etc.) într-un șir de biți cu care se configurează cipul. Aceste etape sunt:

- Sinteza - este etapa în care codul Verilog este interpretat de programul de sinteză care generează din el un circuit (ansamblul de porți și registre) ce poartă denumirea de netlist; această etapă este independentă de modelul de FPGA cu care se lucrează;

- Implementare - etapa în care se translatează circuitul la nivel de poartă (netlist) în circuitul la nivel de elemente disponibile pe cipul FPGA utilizat; în mod evident, acestă etapă depinde de modelul de FPGA utilizat;

- Generare a fișierului de programare - din circuitul de la punctul anterior, se generează un fișier cu extensia .bit care conține biții de configurare pentru blocurile logice, blocurile de I/O și blocurile de interconectare corespunzătoare circuitului dorit;

- Programarea dispozitivului - etapa în care, printr-o interfață JTAG, se încarcă fișierul .bit în memoria SRAM a FPGA-ului, configurând astfel dispozitivul.

Atenție: Modulele de test NU se folosesc în pentru sinteză! Prin urmare un modul de test nu trebuie să apară în Xilinx, ci doar în Modelsim!

Configurarea I/O-ului

Legături externe

Dispozitivele de I/O (input - output) sunt legate în exteriorul cipului de FPGA la câte un pin. Fiecare din acești pini are un nume cunoscut de programul de sinteză. Aceste nume diferă de la un model de FPGA la altul. În figura dată ca exemplu, la pinul cu numele "P88" al FPGA-ului este legat un comutator (switch - SW0) care este un dispozitiv de intrare, iar la pinul "P45" este legat un led (LD0), care este un dispozitiv de ieșire. Aceste legături sunt realizate fizic la producerea plăcilor și nu pot fi modificate. Prin urmare, de cele mai multe ori, în dreptul fiecărui dispozitiv de pe o placă de dezvoltare este trecut în paranteză index-ul sau numele pinului FPGA-ului la care acesta este legat.

Pentru placa de dezvoltare Pegasus, în dreptul fiecărui dispozitiv este trecut index-ul pinului. Ca exemplu, lângă switch-ul SW0 este trecut în paranteză numărul (89). În acest caz, numele complet al pinului, în momentul realizării legăturilor interne în FPGA este P89. Analog pentru toate dispozitivele de pe placă.

Pentru placa de dezvolatare FPGA Spartan-3 Starter Board, în dreptul fiecărui dispozitiv este trecut chiar numele pinului. Ca exemplu, lângă switch-ul SW0 este trecut în paranteză (F12), care este chiar numele pinului. Analog pentru toate dispozitivele de pe placă.

Legături interne

Legăturile interne reprezintă conexiunile logice dintre fiecare bit al porturilor modulului principal, și pinii FPGA-ului. Aceste legături fac posibilă conectarea dispozitivelor externe de pe placa de dezvoltare la modului Verilog definit de utilizator. Spre exemplu, dacă placa FPGA este configurată cu un sumator pe 4 biți, atunci vom vrea ca fiecare bit al porturilor de intrare să fie legat la câte un switch, și fiecare bit al portului de ieșire să fie legat la câte un led, sau la alt dispozitiv de ieșire. Aceste legături nu sunt permanente, prin urmare la fiecare configurare a plăcii, aceste legături trebuie specificate programului de sinteză, înaintea etapei de implementare. Specificațiile legăturilor se dau într-un fișier numit "Implementation Constraints File", care trebuie să fie adăugat la proiectul ISE, și care are următoarea sintaxă:

net "in0[0]" loc = "P88";

Această linie exprimă faptul că bitul 0 (cel mai puțin semnificativ) al portului in0 (care în cazul modulului Adder este o intrare), este legat intern la pinul P88, care în cazul plăcii Pegasus, este legat mai departe extern la switch-ul SW0.

Observație: Analog limbajului Verilog, dacă portul are un singur bit, index-ul acestuia lipsește:

net "port_de_un_bit" loc = "P88";

Regulă: Pentru fiecare bit al fiecărui port al modulului principal, în fișierul de constrângeri trebuie să apară câte o linie, unde acesta este legat la dispozitivul dorit de pe placă.

Intrările în Verilog se definesc cu cuvântul input', ieşirile sunt output. Orice modul începe cu cuvântul module şi se termină cu endmodule. Modulele nu se pot suprapune şi nu pot fi incluse unele în altele.

Xilinx ISE

Programul utilizat in laborator pentru sinteza circuitelor este ISE Design Suite, de la Xilinx. Aveți la dispoziție tutorial-ul de sinteză pentru sumatorul pe 4 biți pe pagina Tutorial Xilinx ISE.

Plăci FPGA disponibile

În laboratorul de CID puteți lucra cu una din următoarele plăci de dezvoltare:

Pentru toate plăcile disponibile, codul modelului ca și codul pachetului sunt scrise direct pe cip.