Diferență între revizuiri ale paginii „Circuite secvențiale”

| (Nu s-au afișat 18 versiuni intermediare efectuate de același utilizator) | |||

| Linia 7: | Linia 7: | ||

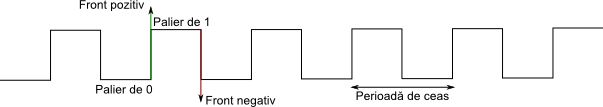

Semnalul de ceas este un semnal periodic, care oscilează cu o anumită frecvență, numită frecvența de ceas. | Semnalul de ceas este un semnal periodic, care oscilează cu o anumită frecvență, numită frecvența de ceas. | ||

| − | Observație: Vezi sintaxa [[Verilog | + | '''Observație:''' Vezi sintaxa [[Verilog#Module de test (nesintetizabile)|Verilog]] pentru a afla cum se generează un semnal de ceas în simulare. |

[[Fișier:seq1.png|Elementele semnalului de ceas]] | [[Fișier:seq1.png|Elementele semnalului de ceas]] | ||

== Circuite de memorare. Registrul == | == Circuite de memorare. Registrul == | ||

| + | |||

| + | Registrul este celula elementară de memorare și baza circuitelor secvențiale. Odată o valoare încarcată într-un registru, aceasta se păstrează până la suprascrierea ei cu o altă valoare. | ||

| + | |||

| + | <div class="regula"><font color="red">'''Regulă:'''</font> Încărcarea unei valori într-un registru se face doar pe frontul de ceas.</div> | ||

| + | <div class="regula"><font color="red">'''Regulă:'''</font> În [[Verilog#Blocuri always secvențiale. Asignări non-blocante (non-blocking assignments)|Verilog]], încărcarea cu o valoare a unui registru se face exclusiv în blocuri '''always'''.</div> | ||

| + | <div class="regula"><font color="red">'''Regulă:'''</font> Dacă un modul este secvențial atunci obligatoriu el va avea un port de intrare pentru semnalul de ceas.</div> | ||

| + | |||

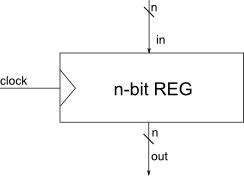

| + | [[Fișier:seq2.png|Reprezentarea grafică a unui registru pe n biți]] | ||

| + | |||

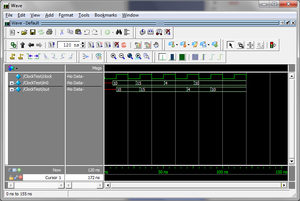

| + | [[Fișier:seq3.png|thumb|Simulare a unui registru pe 4 biți]] | ||

| + | |||

| + | Aceasta este implementarea în Verilog a unui registru pe 4 biți care nu face decât să încarce registrul cu valoarea de intrare, iar în imagine puteți vedea o simulare Modelsim care arată că ieșirea nu se schimbă decât pe frontul pozitiv de ceas care urmează schimbării intrării: | ||

| + | |||

| + | <syntaxhighlight lang="verilog"> | ||

| + | module Register( | ||

| + | output reg [3:0] out, | ||

| + | input [3:0] in, | ||

| + | input clock | ||

| + | ); | ||

| + | |||

| + | always@(posedge clock) begin | ||

| + | out <= in; | ||

| + | end | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | == Reset pentru circuitele secvențiale == | ||

| + | |||

| + | Există situații în care registrele trebuie resetate, adică încărcate cu o valoare implicită. Acest proces de reset este de obicei utilizat când circuitul de blochează, dintr-un motiv sau altul, sau când se dorește repornirea acestuia dint-o stare inițială. Circuitelor pentru care este necesar să fie posibilă resetarea, li se adaugă un semnal de reset. Descrierea în Verilog a unui registru pe 4 biți cu semnal de reset, care doar se încară cu o valoarea de pe intrare, este următoarea: | ||

| + | |||

| + | <syntaxhighlight lang="verilog"> | ||

| + | module Register( | ||

| + | output reg [3:0] out, | ||

| + | input [3:0] in, | ||

| + | input clock, | ||

| + | input reset | ||

| + | ); | ||

| + | |||

| + | always@(posedge clock) begin | ||

| + | if(reset) begin | ||

| + | out <= 4'b0; | ||

| + | end else begin | ||

| + | out <= in; | ||

| + | end | ||

| + | end | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | Acest tip de reset se numește reset sincron, pentru ca el este evaluat doar pe frontul de ceas (sincron cu ceasul). Există și cazuri în care resetul este asincron, iar atunci frontul activ al semnalului de reset trebuie să apară în lista de sensitivități a blocului '''always'''. | ||

Versiunea curentă din 1 aprilie 2014 05:59

Circuitele secvențiale sunt circuitele care sunt sincronizate de un semnal de ceas, adică ale căror ieșiri nu se modifică decât pe frontul pozitiv (sau negativ, în funcție de descriere) de ceas.

Semnalul de ceas

Semnalul de ceas este un semnal periodic, care oscilează cu o anumită frecvență, numită frecvența de ceas.

Observație: Vezi sintaxa Verilog pentru a afla cum se generează un semnal de ceas în simulare.

Circuite de memorare. Registrul

Registrul este celula elementară de memorare și baza circuitelor secvențiale. Odată o valoare încarcată într-un registru, aceasta se păstrează până la suprascrierea ei cu o altă valoare.

Aceasta este implementarea în Verilog a unui registru pe 4 biți care nu face decât să încarce registrul cu valoarea de intrare, iar în imagine puteți vedea o simulare Modelsim care arată că ieșirea nu se schimbă decât pe frontul pozitiv de ceas care urmează schimbării intrării:

module Register(

output reg [3:0] out,

input [3:0] in,

input clock

);

always@(posedge clock) begin

out <= in;

end

endmodule

Reset pentru circuitele secvențiale

Există situații în care registrele trebuie resetate, adică încărcate cu o valoare implicită. Acest proces de reset este de obicei utilizat când circuitul de blochează, dintr-un motiv sau altul, sau când se dorește repornirea acestuia dint-o stare inițială. Circuitelor pentru care este necesar să fie posibilă resetarea, li se adaugă un semnal de reset. Descrierea în Verilog a unui registru pe 4 biți cu semnal de reset, care doar se încară cu o valoarea de pe intrare, este următoarea:

module Register(

output reg [3:0] out,

input [3:0] in,

input clock,

input reset

);

always@(posedge clock) begin

if(reset) begin

out <= 4'b0;

end else begin

out <= in;

end

end

endmodule

Acest tip de reset se numește reset sincron, pentru ca el este evaluat doar pe frontul de ceas (sincron cu ceasul). Există și cazuri în care resetul este asincron, iar atunci frontul activ al semnalului de reset trebuie să apară în lista de sensitivități a blocului always.