Diferență între revizuiri ale paginii „Introducere în sinteza pe FPGA. Xilinx ISE”

(Pagină nouă: == FPGA (Field Programmable Gate Array) == thumb|Schema simplificată a unui FPGA Circuitul [http://en.wikipedia.org/wiki/Field-programmable_gate_array FPGA] (...) |

|||

| Linia 11: | Linia 11: | ||

este format dintr-un LUT (Look-Up Table) și un registru pentru a sincroniza ieșirea acestuia, dacă se dorește acest lucru. Un LUT poate implementa orice funcție logică de 4 variabile cu | este format dintr-un LUT (Look-Up Table) și un registru pentru a sincroniza ieșirea acestuia, dacă se dorește acest lucru. Un LUT poate implementa orice funcție logică de 4 variabile cu | ||

ajutorul unui selector. Fiecare combinație de valori ale variabilelor de intrare selectează rezultatul corespunzător, calculat în prealabil de programul de sinteză și stocat în memoria de configurație la programarea FPGA-ului. Ieșirea generatorului de funcții logice poate fi legată fie la registru, fie direct la ieșirea LUT-ului. | ajutorul unui selector. Fiecare combinație de valori ale variabilelor de intrare selectează rezultatul corespunzător, calculat în prealabil de programul de sinteză și stocat în memoria de configurație la programarea FPGA-ului. Ieșirea generatorului de funcții logice poate fi legată fie la registru, fie direct la ieșirea LUT-ului. | ||

| + | |||

| + | [[Fișier:fpga3.png|thumb|Nodurile de interconectare]] | ||

| + | |||

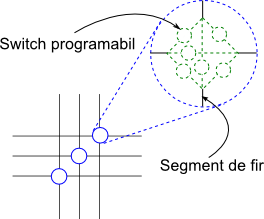

| + | Fiecare bloc programabil este legat la rețeaua de interconectare. Aceasta este formată din segmente de fire și comutatoare programabile. Fiecare comutator poate lega două sau mai multe segmente între ele, asa cum se poate observa în figură. Starea comutatoarelor (on/off) este deasemenea determinată în prealabil în etapa de Place and Route, și stocată în memoria de configurație. | ||

Versiunea de la data 25 februarie 2012 20:57

FPGA (Field Programmable Gate Array)

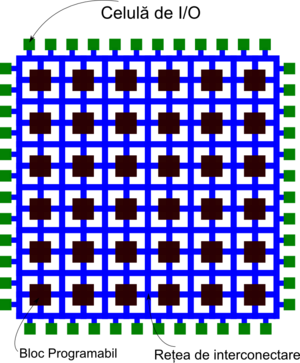

Circuitul FPGA (Field Programmable Gate Array) este un circuit generic ce poate fi programat pentru a implementa orice funcție definită de utilizator. Un FPGA este constituit dintr-o matrice de blocuri programabile, o rețea de interconectare care leagă aceste blocuri între ele, circuite de I/O și o memorie SRAM care configurează aceste structuri. Figura alăturată prezinta o schema simplificata de FPGA.

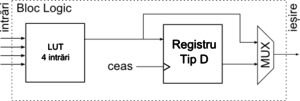

Blocurile programabile pot fi generatoare de funcții logice, memorii RAM, sau circuite de înmulțire. În figură este prezentată structura unui bloc generator de funcții logice. Acesta este format dintr-un LUT (Look-Up Table) și un registru pentru a sincroniza ieșirea acestuia, dacă se dorește acest lucru. Un LUT poate implementa orice funcție logică de 4 variabile cu ajutorul unui selector. Fiecare combinație de valori ale variabilelor de intrare selectează rezultatul corespunzător, calculat în prealabil de programul de sinteză și stocat în memoria de configurație la programarea FPGA-ului. Ieșirea generatorului de funcții logice poate fi legată fie la registru, fie direct la ieșirea LUT-ului.

Fiecare bloc programabil este legat la rețeaua de interconectare. Aceasta este formată din segmente de fire și comutatoare programabile. Fiecare comutator poate lega două sau mai multe segmente între ele, asa cum se poate observa în figură. Starea comutatoarelor (on/off) este deasemenea determinată în prealabil în etapa de Place and Route, și stocată în memoria de configurație.