Diferență între revizuiri ale paginii „CID Seminar 2”

Cbira (discuție | contribuții) |

|||

| (Nu s-au afișat 19 versiuni intermediare efectuate de alți 2 utilizatori) | |||

| Linia 1: | Linia 1: | ||

| − | În acest seminar veţi învăţa | + | Descriere comportamentală, atribuire continuă, instrucţiuni condiţionale, folosirea blocurilor '''always''' pentru descrierea circuitelor combinaţionale. |

| + | |||

| + | În seminarul anterior circuitele au fost descrise prin intermediul schemei lor. În acest seminar veţi învăţa alte modalităţi de descriere a circuitelor combinaţionale, pornind de la funcţia realizată de circuit. | ||

'''Cuvinte cheie''': atribuirea condiţionată, proces, listă de senzitivităţi | '''Cuvinte cheie''': atribuirea condiţionată, proces, listă de senzitivităţi | ||

| Linia 7: | Linia 9: | ||

Verilog este un HDL, un limbaj de descriere hardware şi are numite caracteristici care derivă din faptul că limbajul este destinat descrierii, simulării şi sintezei unor circuite (şi nu execuţiei unor algoritmi). Astfel, anumite instrucţiuni precum assign şi always descriu (reprezintă) '''procese''' care se execută în paralel. Cu ajutorul lor se poate modela comportamentul unor circuite a căror ieşire se modifică de câte ori apare o modificare a semnalelor de la intrare. | Verilog este un HDL, un limbaj de descriere hardware şi are numite caracteristici care derivă din faptul că limbajul este destinat descrierii, simulării şi sintezei unor circuite (şi nu execuţiei unor algoritmi). Astfel, anumite instrucţiuni precum assign şi always descriu (reprezintă) '''procese''' care se execută în paralel. Cu ajutorul lor se poate modela comportamentul unor circuite a căror ieşire se modifică de câte ori apare o modificare a semnalelor de la intrare. | ||

| − | == | + | ==Exercițiul 1== |

| − | Descrieţi în Verilog un circuit de selecţie cu două intrări (şi un bit de selecţie), folosind instrucţiunea de atribuire condiţionată. | + | Descrieţi în Verilog un circuit de selecţie cu două intrări (şi un bit de selecţie), folosind: |

| + | # instrucţiunea de atribuire; | ||

| + | # instrucţiunea de atribuire condiţionată. | ||

<u>Explicaţie suplimentară</u> | <u>Explicaţie suplimentară</u> | ||

| − | ''' | + | Acest exerciţiu se referă la circuitul descris în seminarul 1, exerciţiile 1-2. La punctul 1 se va folosi expresia logică dedusă din circuitul respectiv. Pentru punctul 2, descriem direct funcţia pe care o realizează acest circuit: dacă s == 1, y = b, iar dacă s == 0, y = a. |

| + | |||

| + | [[Fișier:sem1ex1.png]] | ||

| + | |||

| + | ==Exercițiul 2== | ||

| + | |||

| + | Scrieţi funcţia de selecţie realizată de circuitul din exemplul anterior folosind instrucţiunea ''if''. Simulaţi comparativ funcţionarea circuitului cu implementarea din acest exerciţiu şi exerciţiul 1, punctul 2. | ||

| + | |||

| + | <u>Explicaţie suplimentară</u> | ||

| + | |||

| + | Pentru a descrie un circuit combinaţionaţional cu ajutorul unei instrucţiuni ''if'', folosim blocuri | ||

| + | ''always''. Reţineţi că în general, în Verilog, '''instrucţiunea if se foloseşte numai în blocuri ''always'''''. | ||

| + | |||

| + | ==Exercițiul 3== | ||

| + | |||

| + | Descrieţi un multiplexor cu 4 intrări şi 2 biţi de selecţie folosind instrucţiunea ''case''. Simulaţi funcţionarea circuitului. | ||

| + | |||

| + | <u>Explicaţie suplimentară</u> | ||

| + | |||

| + | Ca şi instrucţiunea if, case se foloseşte numai într-un bloc always; variabilele care sunt atribuite trebuie să fie declarate de tip reg. | ||

| + | |||

| + | ==Exercițiul 4== | ||

| + | |||

| + | Descrieţi în Verilog un circuit care incrementează numărul de la intrare (pe patru biţi) numai dacă intrarea de comandă este 1. | ||

| + | |||

| + | ==Exercițiul 5== | ||

| + | |||

| + | Descrieţi un transcodor BCD - 7 segmente folosind instrucţiunea ''case''. | ||

| + | |||

| + | '''Indicaţie''': Transcodorul binar – 7 segmente are la intrare un număr binar pe 4 biţi (care reprezintă o cifră zecimală) şi calculează la ieşire 7 semnale logice, care comandă cele 7 segemente ale unui afişaj [[Dispozitiv de IO: Afișajul cu 7 segmente]]. | ||

| + | Pentru numerele 10-15, vom comanda afişarea simbolului E (pentru eroare). | ||

| + | |||

| + | ==Temă== | ||

| + | |||

| + | # Descrieţi funcţia unui comparator folosind instrucţiunea assign, respectiv instrucţiunea if: | ||

| + | ## pentru două intrări de 1 bit şi o ieşire care este activă când intrările sunt egale; | ||

| + | ## pentru două intrări de câte 3 biţi, cu o ieşire care este activă când intrările sunt egale; | ||

| + | ## pentru două intrări de câte 3 biţi, cu trei ieşiri care semnalează cele trei cazuri. | ||

| + | # Descrieţi un multiplexor cu 2 biţi de selecţie folosind | ||

| + | ## instrucţiunea assign condiţionată; | ||

| + | ## instrucţiunea assign şi expresii logice. | ||

| + | # Modificaţi exemplul 5, considerând că intrarea este o cifră hexazecimală. ''Indicaţie: Pentru valorile 9-15 pe intrare nu se va afişa eroare (E), ci cifrele corespunzătoare din baza 16, simbolizate cu A, b, C, d, E, F.'' | ||

| + | # Descrieţi în Verilog o schemă care conţine circuitul incrementator (din exemplul 4) şi transcodorul binar - 7 segmente (din exemplul 5). Simulaţi funcţionarea acestui circuit. | ||

| + | |||

| + | == Principalele noţiuni de Verilog introduse în acest seminar == | ||

| + | |||

| + | === Atribuirea continuă === | ||

| + | |||

| + | Atribuirea continuă din Verilog, instrucţiunea ''assign'', se evaluează de câte ori se modifică valoarea unui argument. | ||

| + | |||

De exemplu, expresia | De exemplu, expresia | ||

| + | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

assign a = b + c; | assign a = b + c; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | este calculată din nou | + | este calculată din nou dacă b sau c îşi modifică valoarea. Atribuirea continuă are rolul de a descrie funcţionarea circuitelor combinaţionale, în care ieşirea urmează modificările intrărilor. Toate instrucţiunile ''assign'' se execută în paralel, aşa cum toate componentele unui circuit funcţionează în acelaşi timp. |

| + | |||

| + | === Atribuire condiţionată === | ||

| − | Instrucţiunea de | + | Instrucţiunea de atribuire condiţionată are forma |

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

assign w = x ? a : b; | assign w = x ? a : b; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | Atribuirea depinde de valoarea lui x: dacă x == 1, w = a, iar pentru x == 0, w = b. | |

| − | + | === Instrucţiunea ''if'' === | |

| + | Instrucţiunea ''if''în Verilog are forma | ||

| − | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

if (conditie) ...... // de exemplu, if (a == b) | if (conditie) ...... // de exemplu, if (a == b) | ||

| − | + | else ....; | |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | Mai multe instrucţiuni pot fi grupate în blocuri folosind | + | Atribuirile dintr-o construcţie de acest tip sunt secvenţiale ('''nu''' se foloseşte ''assign'') şi implică să declarăm variabilele respective, care îşi modifică valoarea, de tipul ''reg''. Mai multe instrucţiuni pot fi grupate în blocuri folosind begin ....end. Pentru a descrie un circuit combinaţionaţional cu ajutorul unei instrucţiuni ''if'', folosim blocul ''always''. Reţineţi că în general, în Verilog, '''instrucţiunea ''if'' se foloseşte numai în blocuri ''always'''''. |

| + | |||

| + | === Procese '''always''' === | ||

| − | + | În Verilog, instrucţiunea '''always''' descrie un proces care se execută atunci când se modifică cel puţin un semnal din lista de senzitivităţi (lista semnalelor care apare în paranteză, după simbolul @)). | |

| − | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

| − | always @ (a or b or c) | + | always @ (a or b or c) // aici nu se pune ";" |

| − | + | y = a + b + c; // datorita blocului always, atribuirea secvențială se | |

| − | + | //recalculeaza de fiecare dată când se modifică | |

| − | + | //unul dintre semnalele a, b sau c | |

| − | + | // atentie! y este de tipul reg | |

</syntaxhighlight> | </syntaxhighlight> | ||

| + | |||

Mai simplu, putem scrie | Mai simplu, putem scrie | ||

| + | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

always @ (*) | always @ (*) | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | Unde notaţia | + | |

| + | Unde notaţia (*) desemneaza orice modificare. | ||

Atunci când se simulează funcţionarea unui circuit, toate blocurile ''always'' se execută în paralel. | Atunci când se simulează funcţionarea unui circuit, toate blocurile ''always'' se execută în paralel. | ||

| − | == | + | === Blocuri ''case'' === |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | Instrucţiunea case în Verilog are următorul format: | |

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

case (expresie_case) | case (expresie_case) | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | valoare1: instrucţiune1; /* pentru diferite valori ale expresiei se executa diferite instr*/ | |

| − | + | ... | |

| − | + | default: instrucţiune; /* cazul implicit, pentru valorile care nu au fost precizate*/ | |

| − | |||

| − | + | endcase | |

| + | </syntaxhighlight> | ||

| − | + | Ca şi instrucţiunea if, case se foloseşte numai într-un bloc always; variabilele care | |

| + | sunt atribuite trebuie să fie declarate de tip reg. | ||

| − | == | + | ==Reguli de bună practică== |

| + | * Atunci când descriem circuite combinaţionale, pentru instrucţiunea if se precizează şi else, chiar dacă nu se petrece nimic. De exemplu: | ||

| − | + | <syntaxhighlight lang="verilog"> | |

| − | + | a_lt_b = 0; | |

| − | + | if (a<b) a_lt_b = 1; | |

| − | + | else ; | |

| − | + | </syntaxhighlight> | |

| − | |||

| − | |||

| − | Pentru case se scrie întotdeauna şi cazul default, chiar dacă am precizat toate configuraţiile binare posibile (aceasta se face pentru cazul în care valoarea expresiei nu este cunoscută, sau altfel spus are "valoarea" x). | + | * Pentru case se scrie întotdeauna şi cazul default, chiar dacă am precizat toate configuraţiile binare posibile (aceasta se face pentru cazul în care valoarea expresiei nu este cunoscută, sau altfel spus are "valoarea" x). |

Versiunea curentă din 27 aprilie 2018 20:22

Descriere comportamentală, atribuire continuă, instrucţiuni condiţionale, folosirea blocurilor always pentru descrierea circuitelor combinaţionale.

În seminarul anterior circuitele au fost descrise prin intermediul schemei lor. În acest seminar veţi învăţa alte modalităţi de descriere a circuitelor combinaţionale, pornind de la funcţia realizată de circuit.

Cuvinte cheie: atribuirea condiţionată, proces, listă de senzitivităţi

Sintaxa Verilog: assign, always, if, case

Verilog este un HDL, un limbaj de descriere hardware şi are numite caracteristici care derivă din faptul că limbajul este destinat descrierii, simulării şi sintezei unor circuite (şi nu execuţiei unor algoritmi). Astfel, anumite instrucţiuni precum assign şi always descriu (reprezintă) procese care se execută în paralel. Cu ajutorul lor se poate modela comportamentul unor circuite a căror ieşire se modifică de câte ori apare o modificare a semnalelor de la intrare.

Exercițiul 1

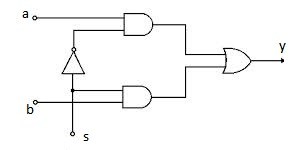

Descrieţi în Verilog un circuit de selecţie cu două intrări (şi un bit de selecţie), folosind:

- instrucţiunea de atribuire;

- instrucţiunea de atribuire condiţionată.

Explicaţie suplimentară

Acest exerciţiu se referă la circuitul descris în seminarul 1, exerciţiile 1-2. La punctul 1 se va folosi expresia logică dedusă din circuitul respectiv. Pentru punctul 2, descriem direct funcţia pe care o realizează acest circuit: dacă s == 1, y = b, iar dacă s == 0, y = a.

Exercițiul 2

Scrieţi funcţia de selecţie realizată de circuitul din exemplul anterior folosind instrucţiunea if. Simulaţi comparativ funcţionarea circuitului cu implementarea din acest exerciţiu şi exerciţiul 1, punctul 2.

Explicaţie suplimentară

Pentru a descrie un circuit combinaţionaţional cu ajutorul unei instrucţiuni if, folosim blocuri always. Reţineţi că în general, în Verilog, instrucţiunea if se foloseşte numai în blocuri always.

Exercițiul 3

Descrieţi un multiplexor cu 4 intrări şi 2 biţi de selecţie folosind instrucţiunea case. Simulaţi funcţionarea circuitului.

Explicaţie suplimentară

Ca şi instrucţiunea if, case se foloseşte numai într-un bloc always; variabilele care sunt atribuite trebuie să fie declarate de tip reg.

Exercițiul 4

Descrieţi în Verilog un circuit care incrementează numărul de la intrare (pe patru biţi) numai dacă intrarea de comandă este 1.

Exercițiul 5

Descrieţi un transcodor BCD - 7 segmente folosind instrucţiunea case.

Indicaţie: Transcodorul binar – 7 segmente are la intrare un număr binar pe 4 biţi (care reprezintă o cifră zecimală) şi calculează la ieşire 7 semnale logice, care comandă cele 7 segemente ale unui afişaj Dispozitiv de IO: Afișajul cu 7 segmente. Pentru numerele 10-15, vom comanda afişarea simbolului E (pentru eroare).

Temă

- Descrieţi funcţia unui comparator folosind instrucţiunea assign, respectiv instrucţiunea if:

- pentru două intrări de 1 bit şi o ieşire care este activă când intrările sunt egale;

- pentru două intrări de câte 3 biţi, cu o ieşire care este activă când intrările sunt egale;

- pentru două intrări de câte 3 biţi, cu trei ieşiri care semnalează cele trei cazuri.

- Descrieţi un multiplexor cu 2 biţi de selecţie folosind

- instrucţiunea assign condiţionată;

- instrucţiunea assign şi expresii logice.

- Modificaţi exemplul 5, considerând că intrarea este o cifră hexazecimală. Indicaţie: Pentru valorile 9-15 pe intrare nu se va afişa eroare (E), ci cifrele corespunzătoare din baza 16, simbolizate cu A, b, C, d, E, F.

- Descrieţi în Verilog o schemă care conţine circuitul incrementator (din exemplul 4) şi transcodorul binar - 7 segmente (din exemplul 5). Simulaţi funcţionarea acestui circuit.

Principalele noţiuni de Verilog introduse în acest seminar

Atribuirea continuă

Atribuirea continuă din Verilog, instrucţiunea assign, se evaluează de câte ori se modifică valoarea unui argument.

De exemplu, expresia

assign a = b + c;

este calculată din nou dacă b sau c îşi modifică valoarea. Atribuirea continuă are rolul de a descrie funcţionarea circuitelor combinaţionale, în care ieşirea urmează modificările intrărilor. Toate instrucţiunile assign se execută în paralel, aşa cum toate componentele unui circuit funcţionează în acelaşi timp.

Atribuire condiţionată

Instrucţiunea de atribuire condiţionată are forma

assign w = x ? a : b;

Atribuirea depinde de valoarea lui x: dacă x == 1, w = a, iar pentru x == 0, w = b.

Instrucţiunea if

Instrucţiunea ifîn Verilog are forma

if (conditie) ...... // de exemplu, if (a == b)

else ....;

Atribuirile dintr-o construcţie de acest tip sunt secvenţiale (nu se foloseşte assign) şi implică să declarăm variabilele respective, care îşi modifică valoarea, de tipul reg. Mai multe instrucţiuni pot fi grupate în blocuri folosind begin ....end. Pentru a descrie un circuit combinaţionaţional cu ajutorul unei instrucţiuni if, folosim blocul always. Reţineţi că în general, în Verilog, instrucţiunea if se foloseşte numai în blocuri always.

Procese always

În Verilog, instrucţiunea always descrie un proces care se execută atunci când se modifică cel puţin un semnal din lista de senzitivităţi (lista semnalelor care apare în paranteză, după simbolul @)).

always @ (a or b or c) // aici nu se pune ";"

y = a + b + c; // datorita blocului always, atribuirea secvențială se

//recalculeaza de fiecare dată când se modifică

//unul dintre semnalele a, b sau c

// atentie! y este de tipul reg

Mai simplu, putem scrie

always @ (*)

Unde notaţia (*) desemneaza orice modificare.

Atunci când se simulează funcţionarea unui circuit, toate blocurile always se execută în paralel.

Blocuri case

Instrucţiunea case în Verilog are următorul format:

case (expresie_case)

valoare1: instrucţiune1; /* pentru diferite valori ale expresiei se executa diferite instr*/

...

default: instrucţiune; /* cazul implicit, pentru valorile care nu au fost precizate*/

endcase

Ca şi instrucţiunea if, case se foloseşte numai într-un bloc always; variabilele care sunt atribuite trebuie să fie declarate de tip reg.

Reguli de bună practică

- Atunci când descriem circuite combinaţionale, pentru instrucţiunea if se precizează şi else, chiar dacă nu se petrece nimic. De exemplu:

a_lt_b = 0;

if (a<b) a_lt_b = 1;

else ;

- Pentru case se scrie întotdeauna şi cazul default, chiar dacă am precizat toate configuraţiile binare posibile (aceasta se face pentru cazul în care valoarea expresiei nu este cunoscută, sau altfel spus are "valoarea" x).