Diferență între revizuiri ale paginii „Tutorial Vivado”

(Pagină nouă: == Instalare Vivado == Pentru a instala utilitarul Vivado, acesta trebuie descarcat de pe site-ul [https://www.xilinx.com/support/download.html Xilinx], alegand versiunea potrivita...) |

|||

| Linia 10: | Linia 10: | ||

La acest pas vom denumi proiectul (de obicei, numele trebuie sa corespunda cu numele modulului TOP) si vom stabili calea la care se va crea acesta. | La acest pas vom denumi proiectul (de obicei, numele trebuie sa corespunda cu numele modulului TOP) si vom stabili calea la care se va crea acesta. | ||

| − | + | [[Fișier:Vivado tutorial pas1.png]] | |

'''Pasul 2: Alegerea tipului proiectului''' | '''Pasul 2: Alegerea tipului proiectului''' | ||

| Linia 16: | Linia 16: | ||

La acest pas, vom selecta RTL Project, apoi vom da click pe '''Next''' | La acest pas, vom selecta RTL Project, apoi vom da click pe '''Next''' | ||

| − | + | [[Fișier:Vivado tutorial pas 2.png]] | |

'''Pasul 3: Adaugarea surselor deja existente''' | '''Pasul 3: Adaugarea surselor deja existente''' | ||

| Linia 22: | Linia 22: | ||

La acest pas vom adauga proiectului sursele modulelor pentru care avem deja descrierea in fisiere de tip Verilog. Acest lucru se face prin '''Add Files''' si selectarea acestora. Daca nu avem fisiere de adaugat, putem da click direct pe '''Next'''. | La acest pas vom adauga proiectului sursele modulelor pentru care avem deja descrierea in fisiere de tip Verilog. Acest lucru se face prin '''Add Files''' si selectarea acestora. Daca nu avem fisiere de adaugat, putem da click direct pe '''Next'''. | ||

| − | + | [[Fișier:Vivado tutorial pas 3.png|600px]] | |

'''Pasul 4: Adaugarea fisierelor de constrangeri''' | '''Pasul 4: Adaugarea fisierelor de constrangeri''' | ||

| − | La acest pas vom adauga fisierele de constrangeri pentru sinteza si implemenatrea pe FPGA, daca este cazul. Daca nu, putem da direct click '''Next'''. | + | La acest pas vom adauga fisierele de constrangeri pentru sinteza si implemenatrea pe FPGA, daca este cazul. Daca nu, putem da direct click pe '''Next'''. |

| − | |||

| + | [[Fișier:Vivado tutorial pas 4.png|600px]] | ||

'''Pasul 5: Alegerea dispozitivului tinta''' | '''Pasul 5: Alegerea dispozitivului tinta''' | ||

| Linia 34: | Linia 34: | ||

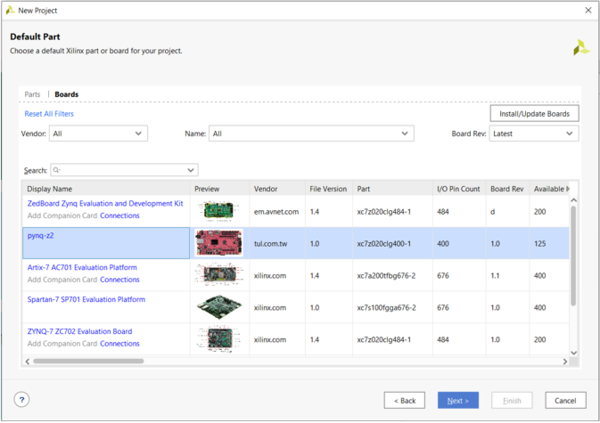

La acest pas vom alege dispozitivul tinta. In cazul laboratorului nostru, acesta este placuta '''PYNQ Z2'''. Mergem la tab-ul '''Boards''', alegem PYNQ Z2, iar apoi dam click pe '''Next'''. | La acest pas vom alege dispozitivul tinta. In cazul laboratorului nostru, acesta este placuta '''PYNQ Z2'''. Mergem la tab-ul '''Boards''', alegem PYNQ Z2, iar apoi dam click pe '''Next'''. | ||

| + | [[Fișier:Vivado tutorial pas 5.png|600px]] | ||

| + | Dupa alegerea dispozitivului, va aparea o pagina cu rezumatul setarilor proiectului. Daca totul este corect, dam click pe '''Finish'''. | ||

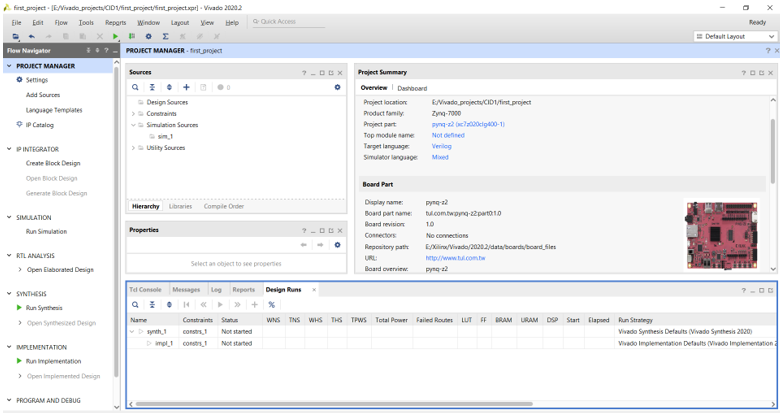

| − | + | '''Pasul 6: Pagina principala a proiectului''' | |

| − | + | [[Fișier:Vivado tutorial pas 6.png]] | |

| − | In fereastra principala a proiectului se pot observa urmatoarele zone: '''Flow navigator''', in care avem principalele comenzi utilizate in crearea, simularea, sinteza si implementarea unui circuit digital pe FPGA, '''Sources''', in care vedem lista cu sursele proiectului | + | In fereastra principala a proiectului se pot observa urmatoarele zone: '''Flow navigator''', in care avem principalele comenzi utilizate in crearea, simularea, sinteza si implementarea unui circuit digital pe FPGA, '''Sources''', in care vedem lista cu sursele proiectului (fisiere verilog in care descriem modulele, fisiere utilizate in simulare, in care vom descrie modulele de test, fisierele de constrangeri), '''Consola''', in josul paginii si zona '''Project Sumary''', in care se vor deschide fisierele proiectului. |

Versiunea de la data 27 februarie 2021 14:37

Instalare Vivado

Pentru a instala utilitarul Vivado, acesta trebuie descarcat de pe site-ul Xilinx, alegand versiunea potrivita sistemului de operare folosit. Pentru a putea descarca orice utilitar Xilinx, va trebui mai intai sa creati un cont. Pentru instalarea Vivado 2020.2 pe sistemul de operare Windows, puteti consulta pagina Tutorial instalare Vivado.

Utilizarea Vivado pentru simularea si sinteza circuitelor digitale

Crearea unui proiect

Pentru a crea un proiect nou, mergeti la File->Project->New, iar apoi vom urma pasii de configurare:

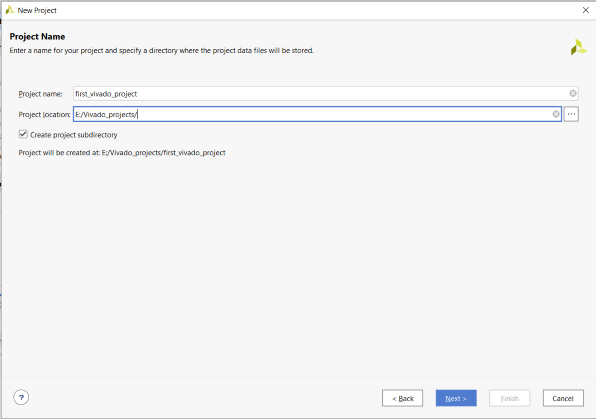

Pasul 1: Denumirea proiectului si stabilirea caii catre acesta

La acest pas vom denumi proiectul (de obicei, numele trebuie sa corespunda cu numele modulului TOP) si vom stabili calea la care se va crea acesta.

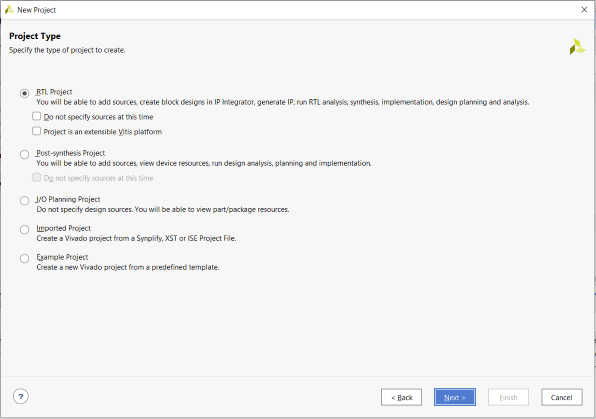

Pasul 2: Alegerea tipului proiectului

La acest pas, vom selecta RTL Project, apoi vom da click pe Next

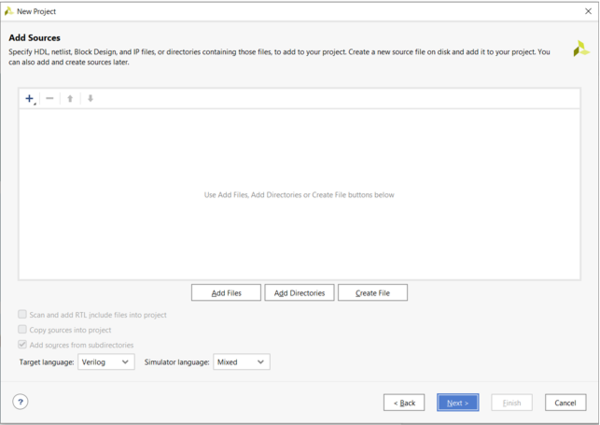

Pasul 3: Adaugarea surselor deja existente

La acest pas vom adauga proiectului sursele modulelor pentru care avem deja descrierea in fisiere de tip Verilog. Acest lucru se face prin Add Files si selectarea acestora. Daca nu avem fisiere de adaugat, putem da click direct pe Next.

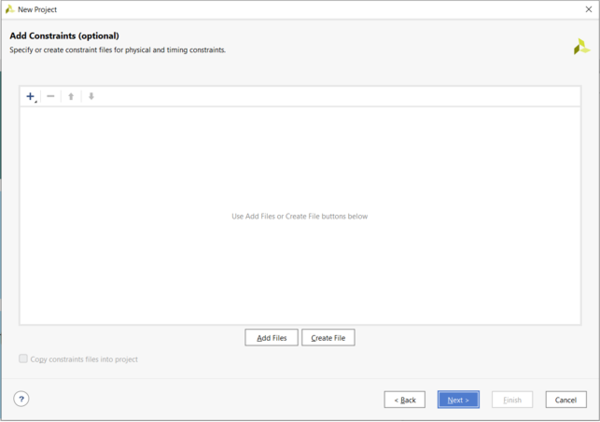

Pasul 4: Adaugarea fisierelor de constrangeri

La acest pas vom adauga fisierele de constrangeri pentru sinteza si implemenatrea pe FPGA, daca este cazul. Daca nu, putem da direct click pe Next.

Pasul 5: Alegerea dispozitivului tinta

La acest pas vom alege dispozitivul tinta. In cazul laboratorului nostru, acesta este placuta PYNQ Z2. Mergem la tab-ul Boards, alegem PYNQ Z2, iar apoi dam click pe Next.

Dupa alegerea dispozitivului, va aparea o pagina cu rezumatul setarilor proiectului. Daca totul este corect, dam click pe Finish.

Pasul 6: Pagina principala a proiectului

In fereastra principala a proiectului se pot observa urmatoarele zone: Flow navigator, in care avem principalele comenzi utilizate in crearea, simularea, sinteza si implementarea unui circuit digital pe FPGA, Sources, in care vedem lista cu sursele proiectului (fisiere verilog in care descriem modulele, fisiere utilizate in simulare, in care vom descrie modulele de test, fisierele de constrangeri), Consola, in josul paginii si zona Project Sumary, in care se vor deschide fisierele proiectului.