Diferență între revizuiri ale paginii „CID Aplicatii 4”

Sduda (discuție | contribuții) |

Sduda (discuție | contribuții) |

||

| Linia 119: | Linia 119: | ||

|} | |} | ||

| + | |||

| + | |||

| + | [[Fișier:Fpga connections.PNG | 600px]] | ||

| + | |||

| + | |||

| + | ==Exemplul 2 == | ||

| + | |||

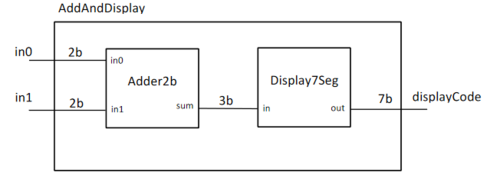

| + | '''Scop:''' Implementarea unui circuit de afisare a sumei dintre doua numere pe 2 biti, folosind afisajul cu 7 segmente | ||

| + | |||

| + | [[Fișier:Add and display.PNG | 500px]] | ||

| + | |||

| + | |||

| + | ''' Implementarea Verilog amodululuiAdder2b''' | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | module Adder2b( | ||

| + | input [1:0] in0, | ||

| + | input [1:0] in1, | ||

| + | output reg [2:0] sum | ||

| + | ); | ||

| + | |||

| + | always@(*) begin | ||

| + | sum = in0 + in1; | ||

| + | end | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | '''Observatii:''' | ||

| + | * Suma a doua numere pe n biti este un numar pe n+1 biti, cel de-al n+1 -ulea fiind bitul de carry.De aceea, aici suma a doua numere pe 2 biti va fi un numar pe 3 biti. | ||

| + | * Aici consideram un sumator simplu, pentru care carry este inglobat in suma (nu este explicit un port separat). | ||

| + | |||

| + | '''Implementarea Verilog a modululuiAfisaj7Seg''' | ||

| + | |||

| + | Inainte de a prezenta codul Verilog, trebuie sa intelegem cum functioneaza afisajul cu 7 segmente. Acest dispozitiv de afisare este format, asa cum sugereaza si numele, din 7 segmente ce pot fi controlate separat. Putem aprinde sau stinge fiecare segmentcontroland tensiunea aplicata pe acesta. Pentru acest afisaj, comanda este negativa: aplicand 0 logic pe un segment acesta se va aprinde, iar aplicand 1 logic, acesta se va stinge. | ||

| + | Structura unui afisaj cu 7 segmente este prezentata in imaginea de mai jos: | ||

| + | |||

| + | == TODO: Add image == | ||

| + | |||

| + | Pentru a reprezenta, de exemplu, cele 16 numere hexa,segmentele trebuie aprinse conform Anexei 1. | ||

| + | |||

| + | In cazul circuitului nostru, vom vrea sa afisam numerele de la 0 la 6, deoarece suma maxima ce poate fi obtinuta este 6. Pentru aceasta, implementam o memorie ROM care va contine codurile de aprins-stins pentru fiecare segment, fiind accesate pe baza numarului pe care dorim sa il afisam. Asadar, intrarea memoriei ROM (adresa) va fi pe 3 biti (3 bitisunt de ajuns pentru a reprezenta numerele de la 0 la 6), iar iesirea va fi pe 7 biti, cate un bit de stare pentru fiecare segment. Vom considera, asadar, ca bitul 0 al iesirii se va lega la segmentul 0, bitul 1 la segmentul 1 si tot asa. | ||

| + | |||

| + | De exemplu, daca la intrare vom avea 0, memoria ROM va trebui sa dea la iesire sirul 1000000, stingand segmentul 6 si aprinzandu-le pe toate celelalte.Extinzand pentru toate numerele de la 0 la 7, obtinem: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- align="center" | ||

| + | ||'''Numar''' || '''Sir de afisare''' | ||

| + | |- align="center" | ||

| + | | 0 || 7'b100_0000 | ||

| + | |- align="center" | ||

| + | | 1 || 7'b111_1001 | ||

| + | |- align="center" | ||

| + | | 2 || 7'b010_0100 | ||

| + | |- align="center" | ||

| + | | 3 || 7'b011_0000 | ||

| + | |- align="center" | ||

| + | | 4 || 7'b001_1001 | ||

| + | |- align="center" | ||

| + | | 5 || 7'b001_0010 | ||

| + | |- align="center" | ||

| + | | 6 || 7'b000_0010 | ||

| + | |} | ||

| + | |||

| + | |||

| + | '''Implementarea Verilog a modululuiDisplay7Seg''' | ||

| + | |||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | module Display7Seg( | ||

| + | input [2:0] in, | ||

| + | output reg [6:0] out | ||

| + | ); | ||

| + | |||

| + | always@(in) begin | ||

| + | case(in) | ||

| + | 3'd0: out = 7'b1000000; | ||

| + | 3'd1: out = 7'b1111001; | ||

| + | 3'd2: out = 7'b0100100; | ||

| + | 3'd3: out = 7'b0110000; | ||

| + | 3'd4: out = 7'b0011001; | ||

| + | 3'd5: out = 7'b0010010; | ||

| + | 3'd6: out = 7'b0000010; | ||

| + | default: out = 7'b0000110; | ||

| + | endcase | ||

| + | end | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

| + | '''Implementarea Verilog a circuitului AddAndDisplay''' | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | module AddAndDisplay( | ||

| + | input [1:0] in0, | ||

| + | input [1:0] in1, | ||

| + | output [6:0] displayCode | ||

| + | ); | ||

| + | |||

| + | wire [2:0] sum; | ||

| + | |||

| + | Adder2b ADD ( | ||

| + | .in0(in0), | ||

| + | .in1(in1), | ||

| + | .sum(sum) | ||

| + | ); | ||

| + | |||

| + | Display7Seg DISPLAY( | ||

| + | .in(sum), | ||

| + | .out(displayCode) | ||

| + | ); | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

<syntaxhighlight lang="Verilog"> | <syntaxhighlight lang="Verilog"> | ||

</syntaxhighlight> | </syntaxhighlight> | ||

Versiunea de la data 21 martie 2021 14:16

Memoria ROM–Introducere

Memoria ROM(Read-Only Memory)este un circuit combinationalfolosit pentru stocarea unor date ce pot fi accesate cu ajutorul unei intrari de adrese. Asa cum se intelege si din nume, memoria ROM, in general, nu poate fi modificata.

Pentru a intelege termenul de memorie, putem face urmatorul exercitiude imaginatie: sa ne gandim la un dulap cu mai multe sertare. Continutul memoriei este reprezentat de continutul sertarelor, iar adresele sunt reprezentate de etichetele lipite pe aceste sertare, pentru a le identifica. Daca avem nevoie de continutul unui sertar, va trebui sa stim eticheta aferenta acestuia.

Am intalnit memoria ROM in aplicatiile anterioare, atunci cand am vorbit despre structura unui FPGA. Am vazut atunci cafunctiile logice erau implementate pe FPGA prin intermediul unor LUT-uri (memorii ROM), care stocau iesirile corespunzatoare unor combinatii de intrari. Asadar, in cazul acela, adreseleerau reprezentate de combinatii ale intrarilor, iar continutul memoriei era reprezentat de iesirile aferente acestor combinatii.

O memorie ROM are urmatorii parametrii: numerul de biti ai adresei, care este legat de numarul de locatii de memorie (cu n biti de adresa putem forma 2𝑛combinatii diferite, deci putem accesa maxim 2𝑛locatii de memorie) si dimensiunea locatiei de memorie, care ne spune cat de multa informatie poate stoca o locatie de memorie.

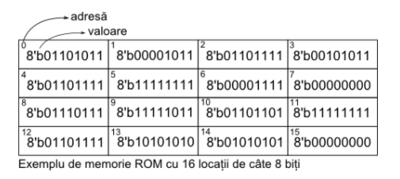

Sa urmarim exemplul din figura urmatoare:

Aici, adresa are dimensiunea de 4 biti, asadar putem accesa cu aceasta 16 locatii diferite de memorie. Dimensiunea fiecarei locatii este de 8 biti, asadar fiecare locatie de memorie poate stoca numere de 8 biti. Spunem ca memoria ROM este o memorie 4x8. Capacitatea acestei memorii este de 16 x 8 biti = 128 biti.

Exemplul 1

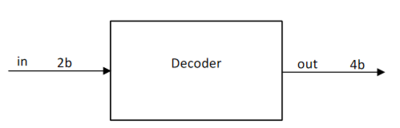

Scop: Descrierea comportamentala a unui decodor, testarea acestuia prin simulare si sinteza pe FPGA.

Decodorul este circuitul care, pentru o anumita valoare a intrarii, va genera laiesire un sir binar care contine 1 pe pozitia cu indicele egal cu valorea intrarii si 0 in rest. De exemplul, decodorul de mai jos pe 2 biti, va avea urmatoarea corespondentaintrare-iesire:

| in | out |

| 2'b00 | 4'b0001 |

| 2'b01 | 4'b0010 |

| 2'b10 | 4'b0100 |

| 2'b11 | 4'b1000 |

Vom implementa acest circuit ca o memorie ROM.

Implementarea Verilog a circuitului

module Decoder(

input [1:0] in,

output reg [3:0] out

);

always@(in) begin

case(in)

2'b00: out = 4'b0001;

2'b01: out = 4'b0010;

2'b10: out = 4'b0100;

2'b11: out = 4'b1000;

default: out = 4'b0000;

endcase

end

endmodule

Implementarea Verilog a modulului de test

`timescale 1ns/1ps

module Decoder_TB();

reg [1:0] in_t;

wire [3:0] out_t;

integer idx;

initial begin

for(idx=0; idx<4; idx = idx + 1) begin

in_t = idx;

#1;

end

#2 $stop();

end

Decoder DUT(

.in(in_t),

.out(out_t)

);

endmodule

Observatii:

- Circuitul Decoder va avea o intrare pe 2 biti, care va reprezenta adresa memoriei ROM si o iesire pe 4 biti, reprezentand continuturile memoriei ROM corespunzatoare fiecarei combinatii de la intrare.

- Chiar daca in interiorul case se acopera toate cazurile posibile (toate combinatiile de 2 biti), este bine sa punem si un default, ca sa evitam inserarea in locul circuitului combinational dorit (aici, memoria ROM) a unui latch.

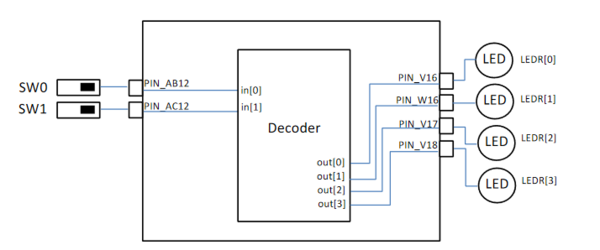

Implementarea pe FPGA:

- Implementarea pe FPGA are ca tinta doar modulul in sine (Decoder), modulul de test (Decoder_TB) fiind nesintetizabil.

- Semnalele de intrare vor fi legate la dispozitive care comanda stari, iar iesirile la dispozitive care observa stari. Asadar, vom alege aici comutatoare pentru intrari (cate un comutator pentru fiecare bital fiecarei intrari –2in total) si 4 LED-uri pentru iesiri.

| Semnal | Dispozitiv | PIN |

| in[0] | SW0 | AB12 |

| in[1] | SW1 | AC12 |

| out[0] | LEDR0 | V16 |

| out[1] | LEDR1 | W16 |

| out[2] | LEDR2 | V17 |

| out[3] | LEDR3 | V18 |

Exemplul 2

Scop: Implementarea unui circuit de afisare a sumei dintre doua numere pe 2 biti, folosind afisajul cu 7 segmente

Implementarea Verilog amodululuiAdder2b

module Adder2b(

input [1:0] in0,

input [1:0] in1,

output reg [2:0] sum

);

always@(*) begin

sum = in0 + in1;

end

endmodule

Observatii:

- Suma a doua numere pe n biti este un numar pe n+1 biti, cel de-al n+1 -ulea fiind bitul de carry.De aceea, aici suma a doua numere pe 2 biti va fi un numar pe 3 biti.

- Aici consideram un sumator simplu, pentru care carry este inglobat in suma (nu este explicit un port separat).

Implementarea Verilog a modululuiAfisaj7Seg

Inainte de a prezenta codul Verilog, trebuie sa intelegem cum functioneaza afisajul cu 7 segmente. Acest dispozitiv de afisare este format, asa cum sugereaza si numele, din 7 segmente ce pot fi controlate separat. Putem aprinde sau stinge fiecare segmentcontroland tensiunea aplicata pe acesta. Pentru acest afisaj, comanda este negativa: aplicand 0 logic pe un segment acesta se va aprinde, iar aplicand 1 logic, acesta se va stinge. Structura unui afisaj cu 7 segmente este prezentata in imaginea de mai jos:

TODO: Add image

Pentru a reprezenta, de exemplu, cele 16 numere hexa,segmentele trebuie aprinse conform Anexei 1.

In cazul circuitului nostru, vom vrea sa afisam numerele de la 0 la 6, deoarece suma maxima ce poate fi obtinuta este 6. Pentru aceasta, implementam o memorie ROM care va contine codurile de aprins-stins pentru fiecare segment, fiind accesate pe baza numarului pe care dorim sa il afisam. Asadar, intrarea memoriei ROM (adresa) va fi pe 3 biti (3 bitisunt de ajuns pentru a reprezenta numerele de la 0 la 6), iar iesirea va fi pe 7 biti, cate un bit de stare pentru fiecare segment. Vom considera, asadar, ca bitul 0 al iesirii se va lega la segmentul 0, bitul 1 la segmentul 1 si tot asa.

De exemplu, daca la intrare vom avea 0, memoria ROM va trebui sa dea la iesire sirul 1000000, stingand segmentul 6 si aprinzandu-le pe toate celelalte.Extinzand pentru toate numerele de la 0 la 7, obtinem:

| Numar | Sir de afisare |

| 0 | 7'b100_0000 |

| 1 | 7'b111_1001 |

| 2 | 7'b010_0100 |

| 3 | 7'b011_0000 |

| 4 | 7'b001_1001 |

| 5 | 7'b001_0010 |

| 6 | 7'b000_0010 |

Implementarea Verilog a modululuiDisplay7Seg

module Display7Seg(

input [2:0] in,

output reg [6:0] out

);

always@(in) begin

case(in)

3'd0: out = 7'b1000000;

3'd1: out = 7'b1111001;

3'd2: out = 7'b0100100;

3'd3: out = 7'b0110000;

3'd4: out = 7'b0011001;

3'd5: out = 7'b0010010;

3'd6: out = 7'b0000010;

default: out = 7'b0000110;

endcase

end

endmodule

Implementarea Verilog a circuitului AddAndDisplay

module AddAndDisplay(

input [1:0] in0,

input [1:0] in1,

output [6:0] displayCode

);

wire [2:0] sum;

Adder2b ADD (

.in0(in0),

.in1(in1),

.sum(sum)

);

Display7Seg DISPLAY(

.in(sum),

.out(displayCode)

);

endmodule