Diferență între revizuiri ale paginii „Tutorial Xilinx ISE (14.7)”

(ftp -> files.arh.pub.ro) |

|||

| (Nu s-au afișat 11 versiuni intermediare efectuate de alți 2 utilizatori) | |||

| Linia 1: | Linia 1: | ||

| + | == Instalare Xilinx ISE == | ||

| + | |||

| + | === Download === | ||

| + | |||

| + | Puteți descărca kitul de instalare pentru ultima versiune de Xilinx WebPack de pe [http://www.xilinx.com/support/download/index.htm site-ul companiei Xilinx]. În continuare, selectați versiunea corespunzătoare sistemului vostru de operare. Este necesar să vă creați un cont pentru a continua. Kit-ul de instalare este compresat într-o arhivă tar.gz. Dacă utilizați sistemul de operare Windows, veți avea nevoie de un program care să îl dezarhiveze. O variantă este [http://www.7-zip.org/ 7-zip]. | ||

| + | |||

| + | Puteți descărca Xilinx ISE 14.7 și de pe site-ul departamentului: https://files.arh.pub.ro/kits/Xilinx_ISE_DS_14.7_1015_1.tar | ||

| + | |||

| + | === Instalare pe Windows === | ||

| + | |||

| + | Odată descărcat kit-ul și instalat programul 7-zip. Dezarhivați fișierele într-un director temporar (pe care îl puteți șterge odată instalat programul). Apoi se ruleaza executabilul ''xsetup.exe''. | ||

| + | |||

| + | În fereastra în care vă cere ediția pe care o doriți înstalată, selectați ISE WebPACK. Este singurul tip de instalare care nu necesită o licență. | ||

| + | |||

| + | În fereastra cu opțiuni de instalare, selectați doar '''Use multiple CPU cores for installer archive extraction''' (dacă este cazul) și '''Aquire or Manage a License Key'''. | ||

| + | |||

| + | La ultimul pas trebuie să selectați directorul destinație pentru instalare. La final, nu uitați să ștergeți directorul temporar. | ||

| + | |||

| + | După instalarea efectivă, va porni '''Xilinx License Configuration Manager'''. Selectați ''Get Free ISE WebPACK License'' și urmăriți instrucțiunile. | ||

| + | |||

| + | === Instalare pe Linux === | ||

| + | |||

| + | Odată kitul descărcat, acesta trebuie dezarhivat într-un director temporar (pe care îl puteți șterge odată instalat programul). Pentru a putea instala un soft pentru toți utilizatorii pe un sistem Lunix, trebuie să aveți drepturi de ''root''. Pentru asta, deschideți o consolă și tastați: | ||

| + | |||

| + | <syntaxhighlight lang="bash"> | ||

| + | su - | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | În continuare vi se va cere parola de ''root''. Pe un sistem Ubuntu, unde ''root'' nu are o parolă setată implicit, tastați: | ||

| + | |||

| + | <syntaxhighlight lang="bash"> | ||

| + | sudo su - | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | În continuare vi se va cere parola user-ului vostru. | ||

| + | |||

| + | Vom dezarhiva kit-ul în directorul /tmp/. Pentru asta, tastați: | ||

| + | |||

| + | <syntaxhighlight lang="bash"> | ||

| + | mkdir /tmp/xilinx | ||

| + | cd /tmp/xilinx | ||

| + | tar -xf ~/Downloads/Xilinx_ISE_DS_Lin_13.4_O.87xd.3.0.tar | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | Am considerat că ați descărcat kitul în directorul ''Downloads'' din home-ul personal. Dacă acesta se află în altă parte, sau are alt nume, schimbați în comandă calea până la arhivă. | ||

| + | |||

| + | Trebuie acum rulat programul de instalare. tastați: | ||

| + | <syntaxhighlight lang="bash"> | ||

| + | cd /tmp/xilinx/Xilinx_ISE_DS_Lin_13.4_O.87xd.3.0/ | ||

| + | ./xsetup.sh | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

== Crearea unui proiect == | == Crearea unui proiect == | ||

| − | Pentru a porni programul Xilinx ISE în laborator, apăsați tasta F12, în consola care apare tastați comanda '''ise&''', și mai apăsați o data F12. Odată pornită aplicația, aceasta va arăta într-un mod similar cu cel de mai jos: | + | Pentru a porni programul Xilinx ISE în laborator, apăsați tasta F12, în consola care apare tastați comanda '''ise&''', enter, și mai apăsați o data F12. Odată pornită aplicația, aceasta va arăta într-un mod similar cu cel de mai jos: |

[[Fișier:ise1_2.png|600px|Fereastra inițială a programului Xilinx ISE]] | [[Fișier:ise1_2.png|600px|Fereastra inițială a programului Xilinx ISE]] | ||

| Linia 9: | Linia 62: | ||

[[Fișier:ise2_2.png|600px|Fereastra proiect nou în Xilinx ISE]] | [[Fișier:ise2_2.png|600px|Fereastra proiect nou în Xilinx ISE]] | ||

| − | Modifcați întâi locația proiectului să fie '''/home/student/Xilinx''' și apoi dați un nume proiectului, în cazul nostru '''Adder'''. Mai departe vi se va afișa următoarea fereastră: | + | Modifcați întâi locația proiectului să fie '''/home/student/Xilinx''' și apoi dați un nume proiectului, în cazul nostru '''Adder'''. |

| + | |||

| + | '''Atenție:''' Rețineți locația unde salvați proiectul deoarece aici se va genera fișierul .bit de care aveți nevoie pentru configurarea plăcii. | ||

| + | |||

| + | Mai departe vi se va afișa următoarea fereastră: | ||

[[Fișier:ise3_2.png|600px|Fereastra pentru configurarea dispozitivului Xilinx ISE]] | [[Fișier:ise3_2.png|600px|Fereastra pentru configurarea dispozitivului Xilinx ISE]] | ||

| Linia 41: | Linia 98: | ||

Odată ce există în proiect cel puțin un fișier HDL, se poate adăuga în continuare fișierul de constrângeri, care va fi subordonat fișierului Verilog principal. Adăugarea lui se face tot prin opțiunea '''New Source...''' din meniul '''Project''': | Odată ce există în proiect cel puțin un fișier HDL, se poate adăuga în continuare fișierul de constrângeri, care va fi subordonat fișierului Verilog principal. Adăugarea lui se face tot prin opțiunea '''New Source...''' din meniul '''Project''': | ||

| − | [[Fișier: | + | [[Fișier:ise9_2.png|600px|Adăugarea fișierului de constrângeri]] |

| − | După selectarea tipului de fișier (Implementation Constraints File) și numirea acestuia dați click pe '''Next''', apoi pe '''Finish'''. În continuare va apărea fișierul de constrângeri sub fișierul Verilog în lista de proiect (vezi cerc verde) | + | După selectarea tipului de fișier (Implementation Constraints File) și numirea acestuia dați click pe '''Next''', apoi pe '''Finish'''. În continuare va apărea fișierul de constrângeri sub fișierul Verilog în lista de proiect (vezi cerc verde), și vi se va deschide fișierul pentru editare. Faceți toate legăturle de care este nevoie. În cazul de față, vom lega intrarea '''in0''' la switch-urile '''SW0 - SW3''', intrarea '''in1''' la switch-urile '''SW4 - SW7''' și ieșirea '''out''' la ledurile '''LD0 - LD4''': |

<syntaxhighlight lang="Verilog"> | <syntaxhighlight lang="Verilog"> | ||

| − | net "out[0]" loc = " | + | net "out[0]" loc = "J14"; |

| − | net "out[1]" loc = " | + | net "out[1]" loc = "J15"; |

| − | net "out[2]" loc = " | + | net "out[2]" loc = "K15"; |

| − | net "out[3]" loc = " | + | net "out[3]" loc = "K14"; |

| − | net "out[4]" loc = " | + | net "out[4]" loc = "E17"; |

| − | net "in0[0]" loc = " | + | net "in0[0]" loc = "G18"; |

| − | net "in0[1]" loc = " | + | net "in0[1]" loc = "H18"; |

| − | net "in0[2]" loc = " | + | net "in0[2]" loc = "K18"; |

| − | net "in0[3]" loc = " | + | net "in0[3]" loc = "K17"; |

| − | net "in1[0]" loc = " | + | net "in1[0]" loc = "L14"; |

| − | net "in1[1]" loc = " | + | net "in1[1]" loc = "L13"; |

| − | net "in1[2]" loc = " | + | net "in1[2]" loc = "N17"; |

| − | net "in1[3]" loc = " | + | net "in1[3]" loc = "R17"; |

</syntaxhighlight> | </syntaxhighlight> | ||

| Linia 69: | Linia 126: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | [[Fișier: | + | '''Observație:''' Pentru a deschide ulterior fișierul de constrângeri pentru editare, acesta trebuie selectat din lista de fișiere ale proiectului (vezi cerc verde), iar după ce îl selectați, în lista de procese va apărea o nouă opțiune '''User Constraints''' -> '''Edit Contraints (Text)''' (vezi cerc albastru) pe care trebuie să dați dublu-click. |

| + | |||

| + | [[Fișier:ise10_2.png|600px|Editarea fișierului de contrângeri]] | ||

== Sinteza și programarea plăcii FPGA == | == Sinteza și programarea plăcii FPGA == | ||

| − | <div style="line-height:1.25; font-size:40px; color:red;">Atenție: asigurați-vă în acest moment că placa este | + | <div style="line-height:1.25; font-size:40px; color:red;">Atenție: asigurați-vă în acest moment că placa este pornită (cablul USB conectat, întrerupătorul de alimentare este pe ON și led-ul rosu POWER este aprins)!</div> |

Pentru a începe etapele procesului de programare a plăcii, veți selecta din nou fișierul Verilog în lista de proiect (vezi cerc verde) și selectați din lista de procese opțiunea '''Generate Programming File'''. Dacă nu există nici o greșeală, în dreptul fiecărei etape va apărea un cerc verde. Dacă aveți erori, în tabul numit '''Errors''' (vezi cerc roșu) puteți afla mai multe detalii ca să vă ajute în procesul de depanare: | Pentru a începe etapele procesului de programare a plăcii, veți selecta din nou fișierul Verilog în lista de proiect (vezi cerc verde) și selectați din lista de procese opțiunea '''Generate Programming File'''. Dacă nu există nici o greșeală, în dreptul fiecărei etape va apărea un cerc verde. Dacă aveți erori, în tabul numit '''Errors''' (vezi cerc roșu) puteți afla mai multe detalii ca să vă ajute în procesul de depanare: | ||

| − | [[Fișier: | + | [[Fișier:ise11_2.png|600px|Pornirea procesului de sinteză și programare a plăcii]] |

Dacă nu există erori, în continuare puteți da click pe opțiunea '''Configure Target Device''' din lista de procese. | Dacă nu există erori, în continuare puteți da click pe opțiunea '''Configure Target Device''' din lista de procese. | ||

| Linia 83: | Linia 142: | ||

Vi se va deschide o fereastră care vă va anunța că nu există definit un proiect iMPACT, iar după ce dați ok, va porni aplicația iMPACT, care este folosită pentru configurarea plăcii și va apărea următoarea fereastră: | Vi se va deschide o fereastră care vă va anunța că nu există definit un proiect iMPACT, iar după ce dați ok, va porni aplicația iMPACT, care este folosită pentru configurarea plăcii și va apărea următoarea fereastră: | ||

| − | [[Fișier: | + | [[Fișier:ise12_2.png|600px|Aplicația iMPACT]] |

| + | |||

| + | În continuare, dați dublu-click pe opțiunea '''Boundary Scan''' (vezi cerc verde). Fereastra principală se va schimba în alb, și acum puteți da click dreapta și selecta opțiunea '''Initialize Chain'''. | ||

| + | |||

| + | [[Fișier:ise13_2.png|600px|Initialize chain]] | ||

| + | |||

| + | Va apărea o fereastră cu două cipuri verzi, fiecare cu un cod de dispozitiv, conform ferestrei de mai jos. Primul are codul FPGA-ului (cel selectat la crearea proiectului și care este scris pe FPGA), iar al doilea are un alt cod. Primul pătrat reprezintă FPGA-ul, iar al doilea o memorie flash pe care nu o vom utiliza și căreia nu-i vom asocia nici un fișier de programare: | ||

| + | |||

| + | [[Fișier:ise14_2.png|600px|Fereastra cu dispozitivele din scan-chain]] | ||

| − | + | Vi se va cere să selectați un fișier de configurare pentru fiecare din cele două cipuri. Pentru FPGA selectați fișierul '''.bit''' obținut la pasul anterior, care poartă numele proiectului (în cazul de față '''adder.bit'''). ATENȚIE: fișierul .bit se află în directorul proiectului. Vi se va da opțiunea să selectați un fișier de configurare pentru PROM Flash. | |

| − | [[Fișier: | + | [[Fișier:ise15_2.png|PROM Flash]] |

| − | + | Selectați NO, iar pentru a doua memorie flash (al doilea pătrat) selectați opțiunea '''Bypass''', sau '''Cancel'''. Pentru a configura efectiv placa, dați click dreapta pe pătratul reprezentând FPGA-ul și selectați opțiunea '''Program'''. Vi se va deschide o fereastră ca cea de mai jos, utilizată pentru modificarea opțiunilor de configurare. Puteți da click pe '''Ok''' fără a modifica nimic. | |

| − | [[Fișier: | + | [[Fișier:ise16.png|600px|Opțiuni de configurare]] |

Versiunea curentă din 8 octombrie 2024 09:53

Instalare Xilinx ISE

Download

Puteți descărca kitul de instalare pentru ultima versiune de Xilinx WebPack de pe site-ul companiei Xilinx. În continuare, selectați versiunea corespunzătoare sistemului vostru de operare. Este necesar să vă creați un cont pentru a continua. Kit-ul de instalare este compresat într-o arhivă tar.gz. Dacă utilizați sistemul de operare Windows, veți avea nevoie de un program care să îl dezarhiveze. O variantă este 7-zip.

Puteți descărca Xilinx ISE 14.7 și de pe site-ul departamentului: https://files.arh.pub.ro/kits/Xilinx_ISE_DS_14.7_1015_1.tar

Instalare pe Windows

Odată descărcat kit-ul și instalat programul 7-zip. Dezarhivați fișierele într-un director temporar (pe care îl puteți șterge odată instalat programul). Apoi se ruleaza executabilul xsetup.exe.

În fereastra în care vă cere ediția pe care o doriți înstalată, selectați ISE WebPACK. Este singurul tip de instalare care nu necesită o licență.

În fereastra cu opțiuni de instalare, selectați doar Use multiple CPU cores for installer archive extraction (dacă este cazul) și Aquire or Manage a License Key.

La ultimul pas trebuie să selectați directorul destinație pentru instalare. La final, nu uitați să ștergeți directorul temporar.

După instalarea efectivă, va porni Xilinx License Configuration Manager. Selectați Get Free ISE WebPACK License și urmăriți instrucțiunile.

Instalare pe Linux

Odată kitul descărcat, acesta trebuie dezarhivat într-un director temporar (pe care îl puteți șterge odată instalat programul). Pentru a putea instala un soft pentru toți utilizatorii pe un sistem Lunix, trebuie să aveți drepturi de root. Pentru asta, deschideți o consolă și tastați:

su -

În continuare vi se va cere parola de root. Pe un sistem Ubuntu, unde root nu are o parolă setată implicit, tastați:

sudo su -

În continuare vi se va cere parola user-ului vostru.

Vom dezarhiva kit-ul în directorul /tmp/. Pentru asta, tastați:

mkdir /tmp/xilinx

cd /tmp/xilinx

tar -xf ~/Downloads/Xilinx_ISE_DS_Lin_13.4_O.87xd.3.0.tar

Am considerat că ați descărcat kitul în directorul Downloads din home-ul personal. Dacă acesta se află în altă parte, sau are alt nume, schimbați în comandă calea până la arhivă.

Trebuie acum rulat programul de instalare. tastați:

cd /tmp/xilinx/Xilinx_ISE_DS_Lin_13.4_O.87xd.3.0/

./xsetup.sh

Crearea unui proiect

Pentru a porni programul Xilinx ISE în laborator, apăsați tasta F12, în consola care apare tastați comanda ise&, enter, și mai apăsați o data F12. Odată pornită aplicația, aceasta va arăta într-un mod similar cu cel de mai jos:

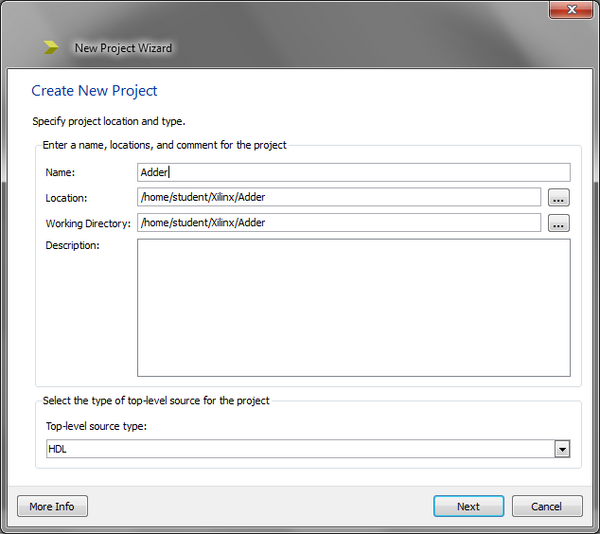

Vom continua acest tutorial cu sinteza circuitului de adunare a cărui simulare a fost prezentată în lucrarea de laborator precedentă. Ca şi în cazul programului Modelsim, prima operație este de a creea un proiect nou. După ce dați click pe File -> New Project vi se va deschide următoarea fereastră:

Modifcați întâi locația proiectului să fie /home/student/Xilinx și apoi dați un nume proiectului, în cazul nostru Adder.

Atenție: Rețineți locația unde salvați proiectul deoarece aici se va genera fișierul .bit de care aveți nevoie pentru configurarea plăcii.

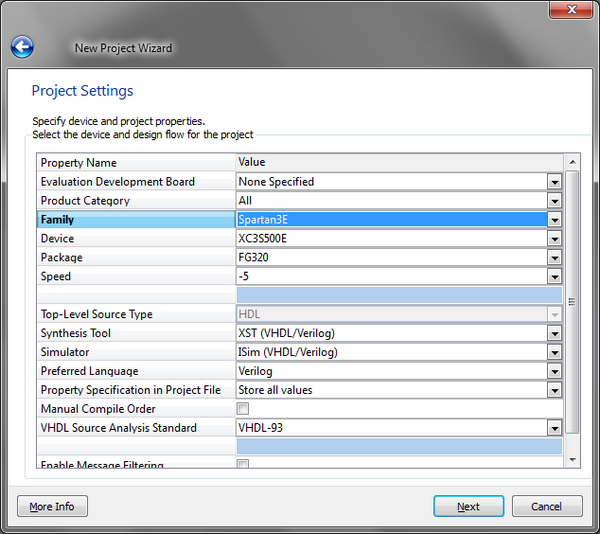

Mai departe vi se va afișa următoarea fereastră:

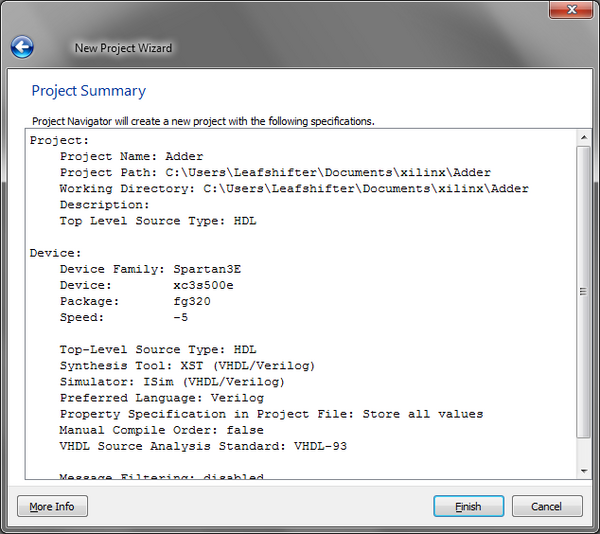

În funcție de placa cu care lucrați, selectați întâi familia de FPGA-uri (Spartan2, Spartan3 sau Spartan3E), apoi alegeți dispozitivul și pachetul conform codurilor pe care le vedeți pe cip. Restul opțiunilor le puteți ignora deocamdată. Ultima fereastă va conține cuprinsul setărilor folosite, unde veți da click pe butonul Finish:

Adăugarea de fișiere noi la proiect

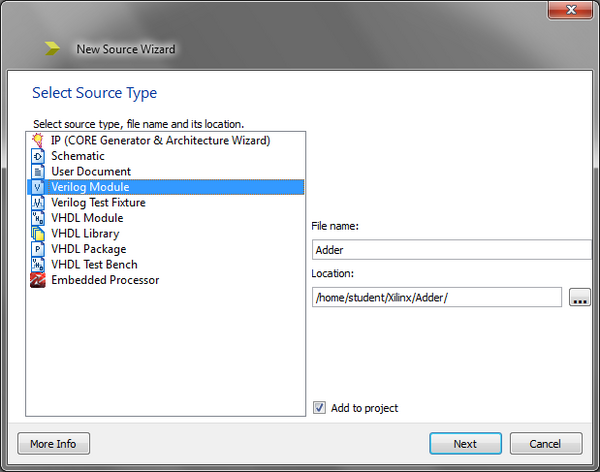

Din meniul Project selectați opțiunea New Source... și va apărea următoarea fereastră:

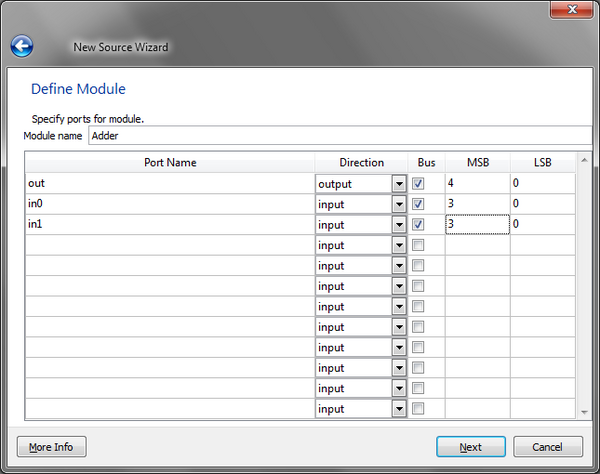

Selectați tipul fișierului ca modul Verilog și dați-i un nume (în cazul de față, Adder). În continuare va apărea fereastra de configurare a modulului:

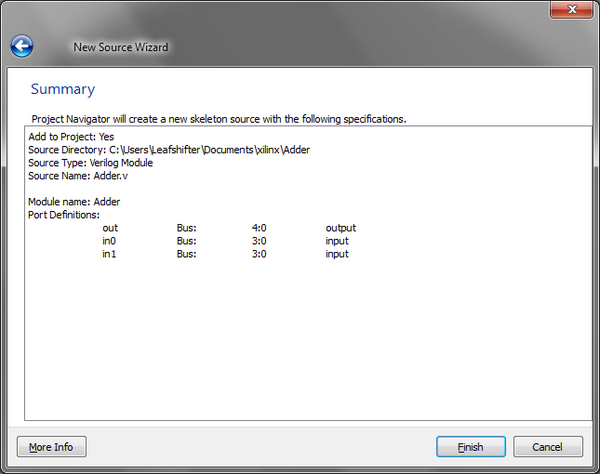

Aici puteți completa detaliile cerute, conform figurii, pentru a genera în mod automat interfața modulului, sau puteți selecta Next și scrie interfața manual, ca și în Modelsim. Celula Bus se bifează dacă portul are mai mult de un bit. Pentru semnale de un singur bit, se lasă ne-bifat. Ultima fereastră vă face un sumar al opțiunilor alese:

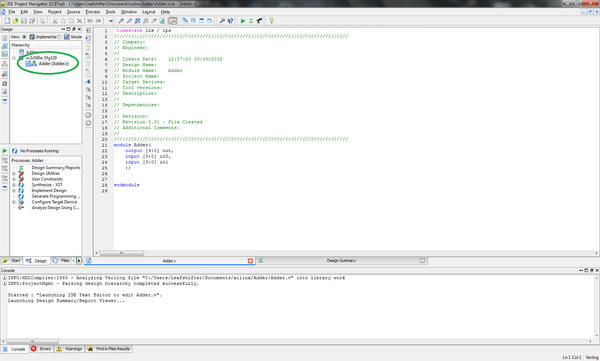

După apăsarea butonului Finish, o sa apară următoarea fereastră, unde se observă că a apărut noul fișier în lista proiectului (vezi cerc verde) și acesta s-a și deschis pentru a putea fi editat. Adăugați blocul assign care implementează funcționalitatea modulului, conform lucrării de laborator 1.

Dacă fișierul Verilog există deja, puteți alege din meniul Project opțiunea Add Copy of Source... care va copia fișierul deja existent în folder-ul proiectului.

Adăugarea fișierului de constrângeri

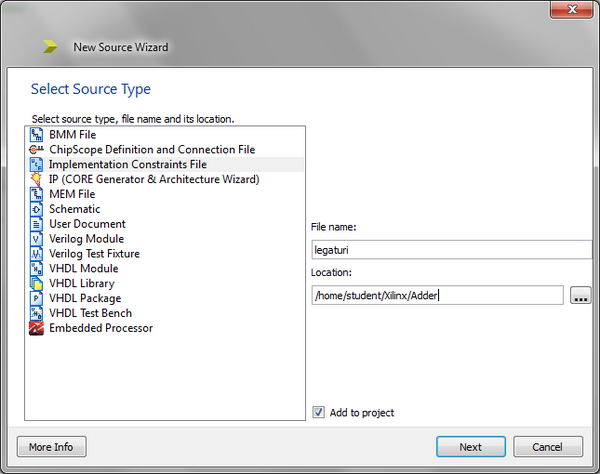

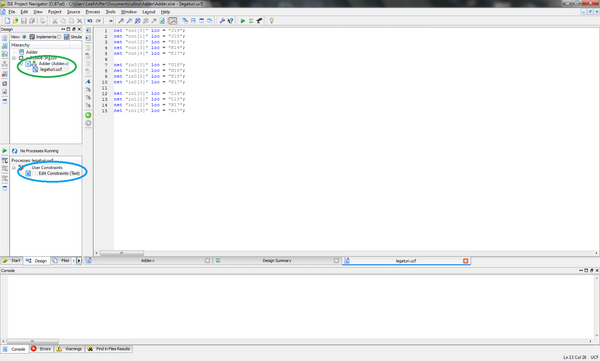

Odată ce există în proiect cel puțin un fișier HDL, se poate adăuga în continuare fișierul de constrângeri, care va fi subordonat fișierului Verilog principal. Adăugarea lui se face tot prin opțiunea New Source... din meniul Project:

După selectarea tipului de fișier (Implementation Constraints File) și numirea acestuia dați click pe Next, apoi pe Finish. În continuare va apărea fișierul de constrângeri sub fișierul Verilog în lista de proiect (vezi cerc verde), și vi se va deschide fișierul pentru editare. Faceți toate legăturle de care este nevoie. În cazul de față, vom lega intrarea in0 la switch-urile SW0 - SW3, intrarea in1 la switch-urile SW4 - SW7 și ieșirea out la ledurile LD0 - LD4:

net "out[0]" loc = "J14";

net "out[1]" loc = "J15";

net "out[2]" loc = "K15";

net "out[3]" loc = "K14";

net "out[4]" loc = "E17";

net "in0[0]" loc = "G18";

net "in0[1]" loc = "H18";

net "in0[2]" loc = "K18";

net "in0[3]" loc = "K17";

net "in1[0]" loc = "L14";

net "in1[1]" loc = "L13";

net "in1[2]" loc = "N17";

net "in1[3]" loc = "R17";

Atenție: Ca și în cazul codului Verilog, dacă portul are un singur bit, atunci va lipsi și paranteza dreaptă cu indexul acestuia, deci:

net "port_de_un_bit" loc = "p46";

Observație: Pentru a deschide ulterior fișierul de constrângeri pentru editare, acesta trebuie selectat din lista de fișiere ale proiectului (vezi cerc verde), iar după ce îl selectați, în lista de procese va apărea o nouă opțiune User Constraints -> Edit Contraints (Text) (vezi cerc albastru) pe care trebuie să dați dublu-click.

Sinteza și programarea plăcii FPGA

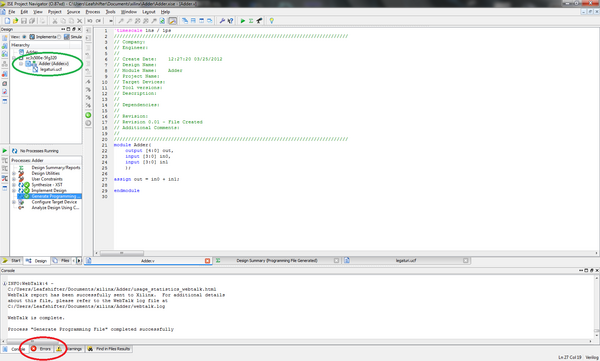

Pentru a începe etapele procesului de programare a plăcii, veți selecta din nou fișierul Verilog în lista de proiect (vezi cerc verde) și selectați din lista de procese opțiunea Generate Programming File. Dacă nu există nici o greșeală, în dreptul fiecărei etape va apărea un cerc verde. Dacă aveți erori, în tabul numit Errors (vezi cerc roșu) puteți afla mai multe detalii ca să vă ajute în procesul de depanare:

Dacă nu există erori, în continuare puteți da click pe opțiunea Configure Target Device din lista de procese.

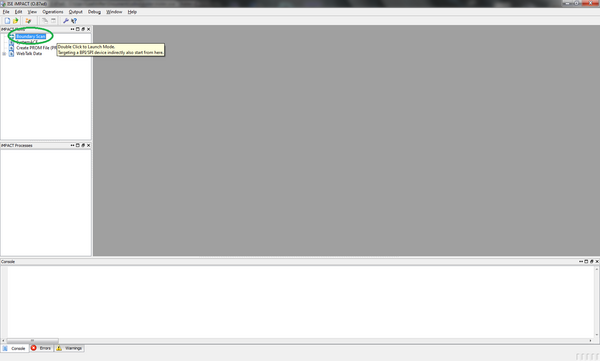

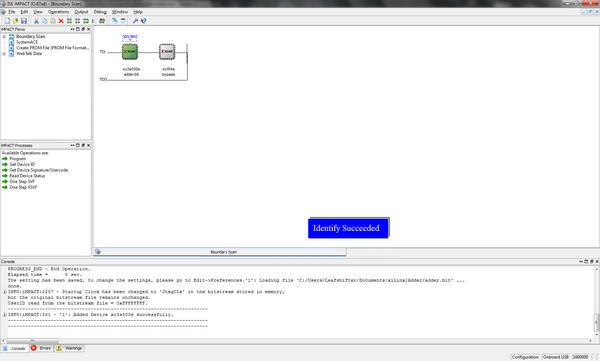

Vi se va deschide o fereastră care vă va anunța că nu există definit un proiect iMPACT, iar după ce dați ok, va porni aplicația iMPACT, care este folosită pentru configurarea plăcii și va apărea următoarea fereastră:

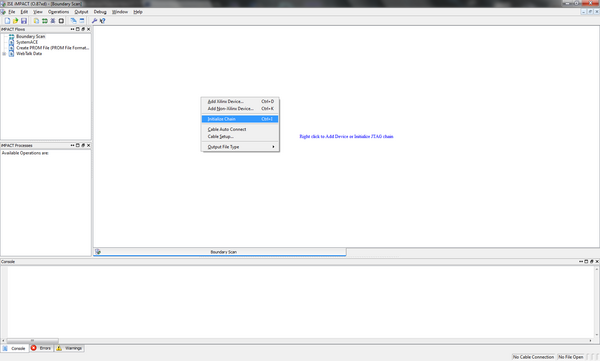

În continuare, dați dublu-click pe opțiunea Boundary Scan (vezi cerc verde). Fereastra principală se va schimba în alb, și acum puteți da click dreapta și selecta opțiunea Initialize Chain.

Va apărea o fereastră cu două cipuri verzi, fiecare cu un cod de dispozitiv, conform ferestrei de mai jos. Primul are codul FPGA-ului (cel selectat la crearea proiectului și care este scris pe FPGA), iar al doilea are un alt cod. Primul pătrat reprezintă FPGA-ul, iar al doilea o memorie flash pe care nu o vom utiliza și căreia nu-i vom asocia nici un fișier de programare:

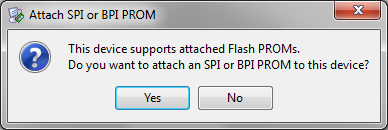

Vi se va cere să selectați un fișier de configurare pentru fiecare din cele două cipuri. Pentru FPGA selectați fișierul .bit obținut la pasul anterior, care poartă numele proiectului (în cazul de față adder.bit). ATENȚIE: fișierul .bit se află în directorul proiectului. Vi se va da opțiunea să selectați un fișier de configurare pentru PROM Flash.

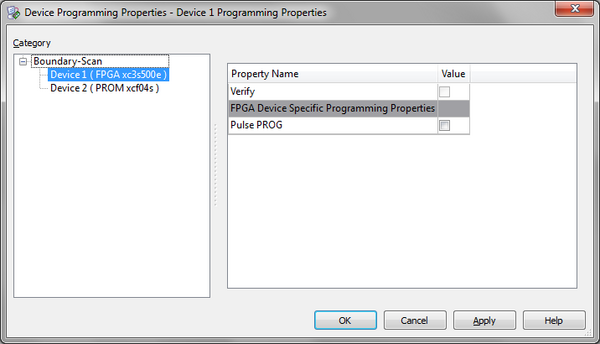

Selectați NO, iar pentru a doua memorie flash (al doilea pătrat) selectați opțiunea Bypass, sau Cancel. Pentru a configura efectiv placa, dați click dreapta pe pătratul reprezentând FPGA-ul și selectați opțiunea Program. Vi se va deschide o fereastră ca cea de mai jos, utilizată pentru modificarea opțiunilor de configurare. Puteți da click pe Ok fără a modifica nimic.