Diferență între revizuiri ale paginii „Divizorul de frecvență”

| (Nu s-a afișat o versiune intermediară efectuată de același utilizator) | |||

| Linia 3: | Linia 3: | ||

După cum s-a văzut în lucrarea 3 de laborator, cel mai simplu divizor de ceas este un numărător. Dar această implementare are limitări. Fiecare bit are o frecvență de două ori mai mică decât bitul precedent, deci există o multime discretă de valori posibile de frecvență pe care acestă implementare le poate oferi. Spre exemplu, pentru ceasul de 50MHz, valorile posibile de ieșire sunt: 25MHz, 12,5MHz, 6,25MHz, 3,125MHz, 1,5625MHz, etc. Dacă dorim un semnal de ceas cu frecvența de 1Hz, această implementare nu o poate oferi. | După cum s-a văzut în lucrarea 3 de laborator, cel mai simplu divizor de ceas este un numărător. Dar această implementare are limitări. Fiecare bit are o frecvență de două ori mai mică decât bitul precedent, deci există o multime discretă de valori posibile de frecvență pe care acestă implementare le poate oferi. Spre exemplu, pentru ceasul de 50MHz, valorile posibile de ieșire sunt: 25MHz, 12,5MHz, 6,25MHz, 3,125MHz, 1,5625MHz, etc. Dacă dorim un semnal de ceas cu frecvența de 1Hz, această implementare nu o poate oferi. | ||

| + | |||

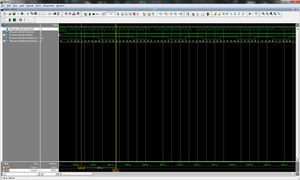

| + | [[Fișier:divfreq0.png|thumb|Exemplu de divizor de frecvență cu limita 4. Se observă perioada semnalului de ieșire între cele două markere ca fiind 220ns]] | ||

Pentru a rezolva această cerință, se va utiliza tot un numărător, dar în alt mod. În loc de a izola un bit care să fie folosit pe post de semnal de ceas, numărătorului i se va da o valoare limită de numărare, iar când se ajunge la valoarea respectivă, numărătorul neagă semnalul de ceas de ieșire, conform formelor de undă din figură. Prin urmare, dacă perioada semnalului de ceas al numărătorului este de ''Tc'', atunci numărătorul se va incrementa la fiecare ''Tc'' unități de timp (fiecare front de ceas), ceea ce înseamnă că va ajunge la valoarea limită, notată ''n'' după ''n * Tc'' unități de timp. Întârzierea de un ceas introdusă de registrul de ieșire mai introduce o perioadă de ceas, prin urmare semnalul de ieșire se schimbă după fiecare ''(n + 1) * Tc'' unități de timp. Astfel, perioada semnalului de ieșire este dată de schimbarea acestuia de două ori (0 -> 1, 1 -> 0), schimbare care durează cât două numărări complete până la limita ''n''. Deci, perioada semnalului de ieșire este ''Tn = 2 * (n + 1) * Tc''. Trecând în frecvență, ''fn = fc / (2 * (n + 1))'', unde ''n'' este valoarea limită dată numărătorului. | Pentru a rezolva această cerință, se va utiliza tot un numărător, dar în alt mod. În loc de a izola un bit care să fie folosit pe post de semnal de ceas, numărătorului i se va da o valoare limită de numărare, iar când se ajunge la valoarea respectivă, numărătorul neagă semnalul de ceas de ieșire, conform formelor de undă din figură. Prin urmare, dacă perioada semnalului de ceas al numărătorului este de ''Tc'', atunci numărătorul se va incrementa la fiecare ''Tc'' unități de timp (fiecare front de ceas), ceea ce înseamnă că va ajunge la valoarea limită, notată ''n'' după ''n * Tc'' unități de timp. Întârzierea de un ceas introdusă de registrul de ieșire mai introduce o perioadă de ceas, prin urmare semnalul de ieșire se schimbă după fiecare ''(n + 1) * Tc'' unități de timp. Astfel, perioada semnalului de ieșire este dată de schimbarea acestuia de două ori (0 -> 1, 1 -> 0), schimbare care durează cât două numărări complete până la limita ''n''. Deci, perioada semnalului de ieșire este ''Tn = 2 * (n + 1) * Tc''. Trecând în frecvență, ''fn = fc / (2 * (n + 1))'', unde ''n'' este valoarea limită dată numărătorului. | ||

| Linia 11: | Linia 13: | ||

Interfața divizorului de frecvență va conține următoarele semnale: | Interfața divizorului de frecvență va conține următoarele semnale: | ||

| − | * semnalul de ceas și semnalul de reset ca intrări (fiind | + | * semnalul de ceas și semnalul de reset ca intrări (fiind circuit secvențial); |

* valoarea limită, dată ca intrare (numărul de biți pentru această intrare se specifică ținând cont de valoarea maximă a limitei care se poate da în aplicația curentă); | * valoarea limită, dată ca intrare (numărul de biți pentru această intrare se specifică ținând cont de valoarea maximă a limitei care se poate da în aplicația curentă); | ||

* semnalul de ceas divizat, dat ca ieșire a circuitului. | * semnalul de ceas divizat, dat ca ieșire a circuitului. | ||

Versiunea curentă din 8 aprilie 2012 10:15

Unele aplicații au nevoie de un semnal de ceas cu o frecvență mai mică decât cea a ceasului principal al unui circuit (în cazul de față este vorba de oscilatorul de 50MHz de pe placa de dezvoltare cu FPGA). Frecvența și perioada unui semnal sunt invers proporționale (f = 1/T), astfel înjumătățirea frecvenței implică dublarea perioadei. Un semnal cu frecvența de 50MHz are perioada de 20ns.

După cum s-a văzut în lucrarea 3 de laborator, cel mai simplu divizor de ceas este un numărător. Dar această implementare are limitări. Fiecare bit are o frecvență de două ori mai mică decât bitul precedent, deci există o multime discretă de valori posibile de frecvență pe care acestă implementare le poate oferi. Spre exemplu, pentru ceasul de 50MHz, valorile posibile de ieșire sunt: 25MHz, 12,5MHz, 6,25MHz, 3,125MHz, 1,5625MHz, etc. Dacă dorim un semnal de ceas cu frecvența de 1Hz, această implementare nu o poate oferi.

Pentru a rezolva această cerință, se va utiliza tot un numărător, dar în alt mod. În loc de a izola un bit care să fie folosit pe post de semnal de ceas, numărătorului i se va da o valoare limită de numărare, iar când se ajunge la valoarea respectivă, numărătorul neagă semnalul de ceas de ieșire, conform formelor de undă din figură. Prin urmare, dacă perioada semnalului de ceas al numărătorului este de Tc, atunci numărătorul se va incrementa la fiecare Tc unități de timp (fiecare front de ceas), ceea ce înseamnă că va ajunge la valoarea limită, notată n după n * Tc unități de timp. Întârzierea de un ceas introdusă de registrul de ieșire mai introduce o perioadă de ceas, prin urmare semnalul de ieșire se schimbă după fiecare (n + 1) * Tc unități de timp. Astfel, perioada semnalului de ieșire este dată de schimbarea acestuia de două ori (0 -> 1, 1 -> 0), schimbare care durează cât două numărări complete până la limita n. Deci, perioada semnalului de ieșire este Tn = 2 * (n + 1) * Tc. Trecând în frecvență, fn = fc / (2 * (n + 1)), unde n este valoarea limită dată numărătorului.

Se observă că nici această implementare nu poate genera orice frecvență de ieșire, dar mulțimea de valori posibile este mai mare decât cea precedentă.

Interfață

Interfața divizorului de frecvență va conține următoarele semnale:

- semnalul de ceas și semnalul de reset ca intrări (fiind circuit secvențial);

- valoarea limită, dată ca intrare (numărul de biți pentru această intrare se specifică ținând cont de valoarea maximă a limitei care se poate da în aplicația curentă);

- semnalul de ceas divizat, dat ca ieșire a circuitului.

Implementare

Implementarea acestui circuit se face utilizând un registru intern pentru numărare (cu dimensiunea în biți egală cu cea a portului pentru valoarea limită - numărătorul trebuie să poată ajunge la valoarea limită), și un registru pentru semnalul de ceas divizat, de ieșire. Registrul de numărare se incrementează până când ajunge la valoarea limită, în care caz valoarea lui devine 0, iar valoarea registrului de ieșire se neagă.