Diferență între revizuiri ale paginii „Applications 4”

| (Nu s-au afișat 12 versiuni intermediare efectuate de același utilizator) | |||

| Linia 1: | Linia 1: | ||

| − | == Exercise 1 == | + | == <span id="transcoder">Exercise 1</span> == |

| − | + | === transcoder === | |

| + | |||

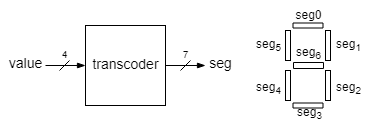

| + | Design a '''transcoder''' circuit, that converts a 4-bit integer from the range 0 ... 9 to a 7-bit combination that shows the integer's value on a 7-segment display. The input of the module should be named '''value''', and the output '''seg'''. | ||

[[Fișier: segment.png]] | [[Fișier: segment.png]] | ||

| Linia 18: | Linia 20: | ||

| <syntaxhighlight lang="Verilog" inline>8'b00000011</syntaxhighlight> || 3, in binary format on 8 bits. Leading zeros are explicitly written | | <syntaxhighlight lang="Verilog" inline>8'b00000011</syntaxhighlight> || 3, in binary format on 8 bits. Leading zeros are explicitly written | ||

|- | |- | ||

| − | | <syntaxhighlight lang="Verilog" inline>8'b0000_0011</syntaxhighlight> || when there are | + | | <syntaxhighlight lang="Verilog" inline>8'b0000_0011</syntaxhighlight> || when there are many bits, the underline, '''_''', may be used to split bits into smaller groups that are easier to read |

|} | |} | ||

| − | + | <syntaxhighlight lang="SystemVerilog"> | |

| + | module transcoder( | ||

| + | input logic [3:0] value, | ||

| + | output logic [6:0] seg | ||

| + | ); | ||

| + | |||

| + | always_comb begin | ||

| + | case (value) | ||

| + | 4'd0: seg = 7'b1000000; | ||

| + | 4'd1: seg = 7'b1111001; | ||

| + | 4'd2: seg = 7'b0100100; | ||

| + | // other 7 cases (for value = 3, 4, ... , 9 | ||

| + | default: seg = 7'b1111111; // all segments are off | ||

| + | endcase | ||

| + | end | ||

| − | + | endmodule | |

| + | </syntaxhighlight> | ||

'''Coding style:''' | '''Coding style:''' | ||

* '''case''' statements should always include the '''default''' case. | * '''case''' statements should always include the '''default''' case. | ||

| + | |||

| + | Open the ''transcoder'' VPL activity on Moodle, upload the source file of the transcoder, run the test and check the results. In case of errors fix the design and retry. After you get TEST PASS on Moodle, proceed to implementation. | ||

| + | |||

| + | === top design module === | ||

| + | |||

| + | The transcoder is wrapped in a top module that takes care also of the digits control. | ||

| + | A digit is active (the segments are displayed) if its common anode (the anode common to all segments of the digit) is connected to the power supply through a controlled switch. The digit is enabled if the corresponding control bit is 0. | ||

| + | There are 4 digits in a display bloc, each with its control signal. These digits share the segment 7-bit control signal. To display different values on those digits, the digit segment combinations should be multiplexed in time. | ||

| + | For this exercise only the rigthmost digit is active. | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | module top( | ||

| + | input logic [3:0] num, | ||

| + | output logic [6:0] seg, | ||

| + | output logic [7:0] anode | ||

| + | ); | ||

| + | |||

| + | transcoder transcoder( | ||

| + | .value (num), | ||

| + | .seg (seg) | ||

| + | ); | ||

| + | |||

| + | assign anode = 8'b11111110; // activate the rightmost digit | ||

| + | |||

| + | endmodule | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | === implementation === | ||

| + | |||

| + | Test the transcoder by connecting its 4 bit input to SW3, SW2, SW1, SW0, and displaying the output on the rightmost digit of a 7-segment display. | ||

| + | |||

| + | |||

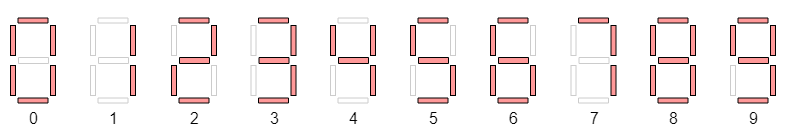

| + | === hexadecimal digit === | ||

| + | |||

| + | The transcoder may be extended to show hexadecimal digits greater than 9. Use the most common 7-segment symbols for them: | ||

| + | |||

| + | [[Fișier: letters.png]] | ||

| + | |||

| + | |||

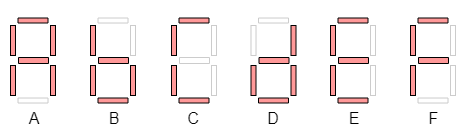

== Exercise 2 == | == Exercise 2 == | ||

| Linia 34: | Linia 90: | ||

[[Fișier: app4_adder.png]] | [[Fișier: app4_adder.png]] | ||

| − | The result of the 3 bit addition is in the range [0 | + | The result of the 3 bit addition is an integer in the range [0 ... 14], and it may be written in the hexadecimal base using only one digit. |

| − | The transcoder must be extended to show hexadecimal digits greater than 9. | + | The transcoder must be extended to show all hexadecimal digits, including those greater than 9. |

| − | + | # change the transcoder description such that to display all hexadecimal digits | |

| + | # the top-level module instantiates the adder and the transcoder, and generates the 8-bit combination that controls all 8 digits | ||

| + | # assign switches SW15, SW14 and SW13 for the input '''a''', SW2, SW1, SW0 for the input '''b'''. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

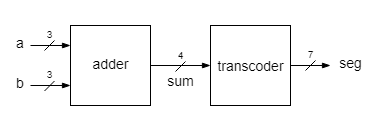

== Exercise 3 == | == Exercise 3 == | ||

| Linia 59: | Linia 109: | ||

[[Fișier: app4_bcd.png]] | [[Fișier: app4_bcd.png]] | ||

| + | <!-- | ||

# create a new project in a new folder | # create a new project in a new folder | ||

# create a new sorce file for the top module, which is described structurally | # create a new sorce file for the top module, which is described structurally | ||

| Linia 66: | Linia 117: | ||

# assign switches SW[9], SW[8] and SW[7] for the input a, SW[2], SW[1] and SW[0] for the input b, Digit0 pins for seg0, and Digit1 pins for seg1 | # assign switches SW[9], SW[8] and SW[7] for the input a, SW[2], SW[1] and SW[0] for the input b, Digit0 pins for seg0, and Digit1 pins for seg1 | ||

# implement and check that the result of multiplying two 3 bit numbers is correctly displayed on two digits in decimal format. If the result is smaller than ten, the first digit will show a leading 0) | # implement and check that the result of multiplying two 3 bit numbers is correctly displayed on two digits in decimal format. If the result is smaller than ten, the first digit will show a leading 0) | ||

| + | --> | ||

| + | |||

| + | |||

| + | == Exercise 4 == | ||

| + | === Caesar cipher === | ||

| + | |||

| + | The Caesar cipher is the simplest substitution cipher. A plain text message is encrypted by replacing each letter from the message by another one that is some fixed number of positions down the alphabet. All letters of the alphabet are changed using the same fixed number of positions. The letters are “shifted” down the alphabet, this code being also named shift cipher. | ||

| + | In this exercise and the following ones, we assume that the plain and encoded messages contain only ASCII uppercase letters A to Z, without blank spaces between words. The encryption is done such that A-Z set of letters are translated to letters from the same set A-Z. For example, if the shift is of 3 positions down the alphabet, '''A''' translates to '''D''', '''B''' to '''E''', '''C''' to '''F''', a.s.o. To achieve the circularity of the encoding, '''W''' translates to '''Z''', '''X''' to '''A''', '''Y''' to '''B''' and '''Z''' to '''C'''. | ||

| + | |||

| + | [[Fișier: Dic_lab4_cipher_shift.png]] | ||

| + | |||

| + | === ASCII code === | ||

| + | The ASCII code is the widest used character encoding standard in digital technology. Originally limited to 7 bits it usually uses 8 bits to code for the Latin alphabet letters, uppercase and lowercase, digits, punctuation marks, some special symbols, and some commands. We need to know the ASCII codes for the uppercase letters of the alphabet: | ||

| + | |||

| + | {| class="wikitable" style="text-align: center; | ||

| + | | Letter || A||B||C||D||E||F||G||H||I||J||K||L||M||N||O||P||Q||R||S||T||U||V||W||X||Y||Z | ||

| + | |- | ||

| + | | hex code|| 41||42||43||44||45||46||47||48||49||4a||4b||4c||4d||4e||4f||50||51||52||53||54||55||56||57||58||59||5a | ||

| + | |} | ||

| + | |||

| + | === Caesar encoder === | ||

| + | Your goal is to design a configurable Caesar encoder, where the shift is set from the outside. The circuit receives an ASCII letter on data_in input, shifts it by a number of positions given by the key input and outputs the resulting letter as data_out. It is supposed that the input data are restricted to the A-Z ASCII codes and the shift is an unsigned integer no greater than 26 (the length of the alphabet) | ||

| + | |||

| + | [[Fișier: Dic_lab4_caesar.png]] | ||

| + | |||

| + | The implementation adds the shift number to the ASCII code of the input letter and corrects the sum such that the output ASCII code is also in the A-Z range of ASCII codes. | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | assign data_out = data_in + shift > 8'd90 ? | ||

| + | data_in + shift - 8'd26 : | ||

| + | data_in + shift; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | === Caesar decoding === | ||

| + | The Caesar encrypted message is easy to decode: we need only to shift back all letters to undo the coding. Of course the decoder needs to know the shift number (by the way, the Caesar code may be easily broken by trying for the encrypted message various shifts until a meaningful message is found). | ||

| + | To reverse the coding of our Caesar encoder, the decoder uses shift_decode = 26 - shift_code | ||

| + | |||

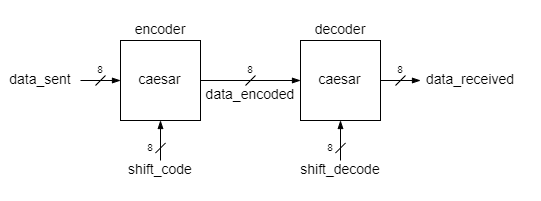

| + | [[Fișier: Dic_lab4_caesar_tb.png]] | ||

| + | |||

| + | === Testbench === | ||

| + | The testbench instantiates two Caesar encoder modules. The first one is the encoder itself, that generates the encoded message. The second instance uses the reversed shift to decode the encrypted message. The shift value (for example 13) may be assigned directly to the shift port of the instance as a literal constant: | ||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | caesar encoder ( | ||

| + | .shift (8'd13), | ||

| + | // other port connections | ||

| + | ); | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | The constant value assigned to an input port is actually a hardwired connection of its bits to the power supply and to the ground. | ||

| + | |||

| + | The testbench generates a sequence of ASCII values for the data_sent input of the encoder. The verilog language allows you to assign to an 8-bit logic variable an ASCII value as a character: | ||

| + | |||

| + | <syntaxhighlight lang="Verilog"> | ||

| + | initial begin | ||

| + | #0 data_sent = "C"; | ||

| + | #1 data_sent = "O"; | ||

| + | #1 data_sent = "M"; | ||

| + | #1 data_sent = "B"; | ||

| + | #1 data_sent = "I"; | ||

| + | #1 data_sent = "N"; | ||

| + | #1 data_sent = "A"; | ||

| + | #1 data_sent = "T"; | ||

| + | #1 data_sent = "I"; | ||

| + | #1 data_sent = "O"; | ||

| + | #1 data_sent = "N"; | ||

| + | #1 data_sent = "A"; | ||

| + | #1 data_sent = "L"; | ||

| + | #1 $stop; | ||

| + | end | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | To display the ASCII values on the waveforms in simulation, right-click the name of the variable in the Simulation panel and select from the pop-up menu '''radix''' -> '''ASCII''' | ||

Versiunea curentă din 2 aprilie 2025 13:30

Exercise 1

transcoder

Design a transcoder circuit, that converts a 4-bit integer from the range 0 ... 9 to a 7-bit combination that shows the integer's value on a 7-segment display. The input of the module should be named value, and the output seg.

The output bits would control the segments of a digit display, one bit for each segment. The segment is lit when the corresponding bit is 0, otherwise it is off (negative logic).

For all numbers greater than 9 the digit must be off. All these 6 cases may be covered in a single assignment under the default case.

Because seg values are easier to handle in binary, the assigned values for seg should be given as binary constants. A number in binary format (or a combination of bit values) must be preceded by the base specificator, 'b, according to the template numberOfBits'bvalue as in the following examples:

8'b11 |

3, in binary format on 8 bits |

8'b00000011 |

3, in binary format on 8 bits. Leading zeros are explicitly written |

8'b0000_0011 |

when there are many bits, the underline, _, may be used to split bits into smaller groups that are easier to read |

module transcoder(

input logic [3:0] value,

output logic [6:0] seg

);

always_comb begin

case (value)

4'd0: seg = 7'b1000000;

4'd1: seg = 7'b1111001;

4'd2: seg = 7'b0100100;

// other 7 cases (for value = 3, 4, ... , 9

default: seg = 7'b1111111; // all segments are off

endcase

end

endmodule

Coding style:

- case statements should always include the default case.

Open the transcoder VPL activity on Moodle, upload the source file of the transcoder, run the test and check the results. In case of errors fix the design and retry. After you get TEST PASS on Moodle, proceed to implementation.

top design module

The transcoder is wrapped in a top module that takes care also of the digits control. A digit is active (the segments are displayed) if its common anode (the anode common to all segments of the digit) is connected to the power supply through a controlled switch. The digit is enabled if the corresponding control bit is 0. There are 4 digits in a display bloc, each with its control signal. These digits share the segment 7-bit control signal. To display different values on those digits, the digit segment combinations should be multiplexed in time. For this exercise only the rigthmost digit is active.

module top(

input logic [3:0] num,

output logic [6:0] seg,

output logic [7:0] anode

);

transcoder transcoder(

.value (num),

.seg (seg)

);

assign anode = 8'b11111110; // activate the rightmost digit

endmodule

implementation

Test the transcoder by connecting its 4 bit input to SW3, SW2, SW1, SW0, and displaying the output on the rightmost digit of a 7-segment display.

hexadecimal digit

The transcoder may be extended to show hexadecimal digits greater than 9. Use the most common 7-segment symbols for them:

Exercise 2

Implement a 3 bit adder whose result is displayed as a hexadecimal digit.

The result of the 3 bit addition is an integer in the range [0 ... 14], and it may be written in the hexadecimal base using only one digit. The transcoder must be extended to show all hexadecimal digits, including those greater than 9.

- change the transcoder description such that to display all hexadecimal digits

- the top-level module instantiates the adder and the transcoder, and generates the 8-bit combination that controls all 8 digits

- assign switches SW15, SW14 and SW13 for the input a, SW2, SW1, SW0 for the input b.

Exercise 3

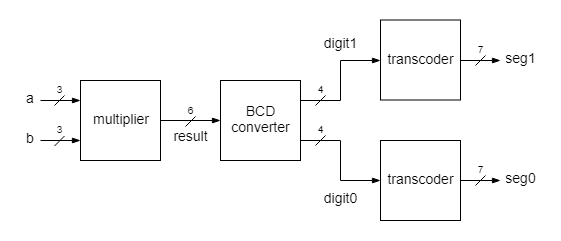

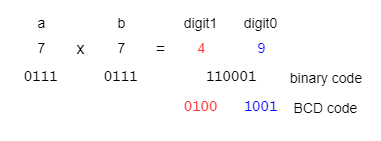

Implement a 3 x 3 bits multiplier, with the result shown in decimal base as a 2 digits number.

This project comprises a top module with 4 blocks. The first block, multiplier, takes in two 3 bit numbers, a and b, and delivers the result of their multiplication in binary format. The input operands and the result are treated as unsigned integers (natural numbers). The next block, BCD converter, converts the result from the binary format to the decimal. The decimal digits are coded in binary, therefore a multidigit number is coded in the so called BCD format (Binary-coded decimal), where each decimal digit is represented as a 4 bit number.

Exercise 4

Caesar cipher

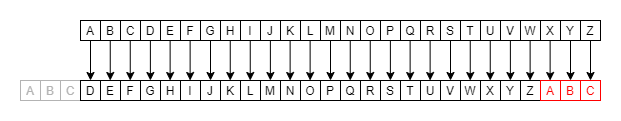

The Caesar cipher is the simplest substitution cipher. A plain text message is encrypted by replacing each letter from the message by another one that is some fixed number of positions down the alphabet. All letters of the alphabet are changed using the same fixed number of positions. The letters are “shifted” down the alphabet, this code being also named shift cipher. In this exercise and the following ones, we assume that the plain and encoded messages contain only ASCII uppercase letters A to Z, without blank spaces between words. The encryption is done such that A-Z set of letters are translated to letters from the same set A-Z. For example, if the shift is of 3 positions down the alphabet, A translates to D, B to E, C to F, a.s.o. To achieve the circularity of the encoding, W translates to Z, X to A, Y to B and Z to C.

ASCII code

The ASCII code is the widest used character encoding standard in digital technology. Originally limited to 7 bits it usually uses 8 bits to code for the Latin alphabet letters, uppercase and lowercase, digits, punctuation marks, some special symbols, and some commands. We need to know the ASCII codes for the uppercase letters of the alphabet:

| Letter | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z |

| hex code | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4a | 4b | 4c | 4d | 4e | 4f | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 5a |

Caesar encoder

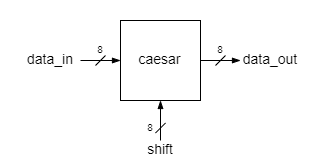

Your goal is to design a configurable Caesar encoder, where the shift is set from the outside. The circuit receives an ASCII letter on data_in input, shifts it by a number of positions given by the key input and outputs the resulting letter as data_out. It is supposed that the input data are restricted to the A-Z ASCII codes and the shift is an unsigned integer no greater than 26 (the length of the alphabet)

The implementation adds the shift number to the ASCII code of the input letter and corrects the sum such that the output ASCII code is also in the A-Z range of ASCII codes.

assign data_out = data_in + shift > 8'd90 ?

data_in + shift - 8'd26 :

data_in + shift;

Caesar decoding

The Caesar encrypted message is easy to decode: we need only to shift back all letters to undo the coding. Of course the decoder needs to know the shift number (by the way, the Caesar code may be easily broken by trying for the encrypted message various shifts until a meaningful message is found). To reverse the coding of our Caesar encoder, the decoder uses shift_decode = 26 - shift_code

Testbench

The testbench instantiates two Caesar encoder modules. The first one is the encoder itself, that generates the encoded message. The second instance uses the reversed shift to decode the encrypted message. The shift value (for example 13) may be assigned directly to the shift port of the instance as a literal constant:

caesar encoder (

.shift (8'd13),

// other port connections

);

The constant value assigned to an input port is actually a hardwired connection of its bits to the power supply and to the ground.

The testbench generates a sequence of ASCII values for the data_sent input of the encoder. The verilog language allows you to assign to an 8-bit logic variable an ASCII value as a character:

initial begin

#0 data_sent = "C";

#1 data_sent = "O";

#1 data_sent = "M";

#1 data_sent = "B";

#1 data_sent = "I";

#1 data_sent = "N";

#1 data_sent = "A";

#1 data_sent = "T";

#1 data_sent = "I";

#1 data_sent = "O";

#1 data_sent = "N";

#1 data_sent = "A";

#1 data_sent = "L";

#1 $stop;

end

To display the ASCII values on the waveforms in simulation, right-click the name of the variable in the Simulation panel and select from the pop-up menu radix -> ASCII