Diferență între revizuiri ale paginii „SystemVerilog”

De la WikiLabs

Jump to navigationJump to search (Pagină nouă: == Module == Limabjul Verilog este structurat pe module. Fiecare modul reprezintă un circuit care implementează o anume funcție. Spre exemplu un modul poate reprezenta un sumator,...) |

(→Module) |

||

| Linia 6: | Linia 6: | ||

Interfața modulului '''Adder''' este prezentată mai jos. | Interfața modulului '''Adder''' este prezentată mai jos. | ||

| + | [[Fișier:Adder_interface.svg|thumb|Reprezentarea interfetei modulului "Adder" (black box)]] | ||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

module Adder( | module Adder( | ||

Versiunea de la data 19 ianuarie 2012 18:00

Module

Limabjul Verilog este structurat pe module. Fiecare modul reprezintă un circuit care implementează o anume funcție. Spre exemplu un modul poate reprezenta un sumator, adică un circuit care are două intrări ce specifică cei doi operanzi și o ieșire ce reprezintă rezultatul adunării. Conținutul modulului reprezintă descrierea (structurală sau comportamentală) a porților care calculeaza suma celor două intrări. Prin urmare, definiția unui modul Verilog are două părți:

- interfață - lista tuturor porturilor de intrare și ieșire ale circuitului, specificate prin nume și dimensiune;

- implementare - descrierea efectivă a circuitului care se folosește de valorile de intrare pentru a calcula valorile de ieșire;

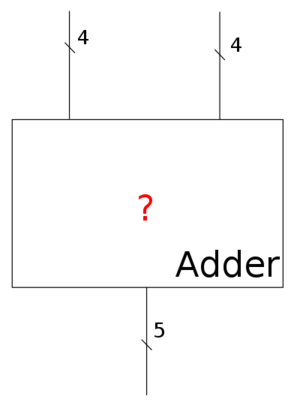

Interfața modulului Adder este prezentată mai jos.

module Adder(

output [4:0] out,

input [3:0] in0,

input [3:0] in1

);

//implementare

endmodule

Cuvintele cheie module și endmodule sunt folosite pentru a începe și a încheia definirea unui modul.