Diferență între revizuiri ale paginii „SystemVerilog”

(→Module) |

(→Module) |

||

| Linia 20: | Linia 20: | ||

Cuvintele cheie '''''module''''' și '''''endmodule''''' sunt folosite pentru a începe și a încheia definirea unui modul. Imediat după cuvântul cheie '''''module''''' urmează numele modulului. | Cuvintele cheie '''''module''''' și '''''endmodule''''' sunt folosite pentru a începe și a încheia definirea unui modul. Imediat după cuvântul cheie '''''module''''' urmează numele modulului. | ||

| + | <div style="border:thin dashed blue;"> | ||

'''''Convenție:''''' Numele unui modul va începe cu literă mare. | '''''Convenție:''''' Numele unui modul va începe cu literă mare. | ||

| + | </div> | ||

În continuare, urmează lista porturilor modulului. Cuvintele cheie acceptate sunt '''''output''''' (reprezentând un port de ieșire), '''''input''''' (reprezentând un port de intrare) și '''''inout''''' (reprezentând un port bidirecțional). | În continuare, urmează lista porturilor modulului. Cuvintele cheie acceptate sunt '''''output''''' (reprezentând un port de ieșire), '''''input''''' (reprezentând un port de intrare) și '''''inout''''' (reprezentând un port bidirecțional). | ||

| + | <div style="border:thin dashed red;"> | ||

<font color="#AA0000">'''''Sfat:'''''</font> Se evită utilizarea semnalelor de tip '''''inout'''''. O alternativă acceptată este definirea a două porturi, unul de intrare și unul de ieșire, cu nume similare (ex: ''data_in'' și ''data_out''). | <font color="#AA0000">'''''Sfat:'''''</font> Se evită utilizarea semnalelor de tip '''''inout'''''. O alternativă acceptată este definirea a două porturi, unul de intrare și unul de ieșire, cu nume similare (ex: ''data_in'' și ''data_out''). | ||

| + | </div> | ||

Versiunea de la data 20 ianuarie 2012 11:27

Module

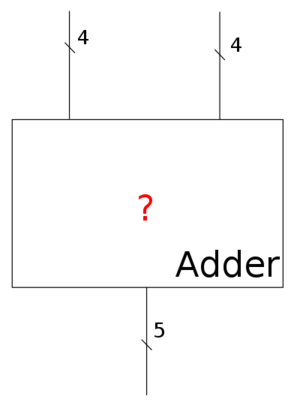

Limabjul Verilog este structurat pe module. Fiecare modul reprezintă un circuit care implementează o anume funcție. Spre exemplu un modul poate reprezenta un sumator, adică un circuit care are două intrări ce specifică cei doi operanzi și o ieșire ce reprezintă rezultatul adunării. Conținutul modulului reprezintă descrierea (structurală sau comportamentală) a porților care calculeaza suma celor două intrări. Prin urmare, definiția unui modul Verilog are două părți:

- interfață - lista tuturor porturilor de intrare și ieșire ale circuitului, specificate prin nume și dimensiune;

- implementare - descrierea efectivă a circuitului care se folosește de valorile de intrare pentru a calcula valorile de ieșire;

Interfața modulului Adder este prezentată mai jos.

module Adder(

output [4:0] out,

input [3:0] in0,

input [3:0] in1

);

//implementare

endmodule

Cuvintele cheie module și endmodule sunt folosite pentru a începe și a încheia definirea unui modul. Imediat după cuvântul cheie module urmează numele modulului.

Convenție: Numele unui modul va începe cu literă mare.

În continuare, urmează lista porturilor modulului. Cuvintele cheie acceptate sunt output (reprezentând un port de ieșire), input (reprezentând un port de intrare) și inout (reprezentând un port bidirecțional).

Sfat: Se evită utilizarea semnalelor de tip inout. O alternativă acceptată este definirea a două porturi, unul de intrare și unul de ieșire, cu nume similare (ex: data_in și data_out).