Diferență între revizuiri ale paginii „CID Seminar 3”

| Linia 12: | Linia 12: | ||

Să se descrie în Verilog un bistabil D cu următoarele caracteristici: | Să se descrie în Verilog un bistabil D cu următoarele caracteristici: | ||

* semnal de ceas activ pe frontul pozitiv | * semnal de ceas activ pe frontul pozitiv | ||

| − | * | + | * semnal de reset sincron cu ceasul, activ pe palierul de 0 |

<u>Explicaţie suplimentară</u> | <u>Explicaţie suplimentară</u> | ||

Versiunea de la data 21 martie 2015 23:46

În acest seminar veţi învăţa ce este un ciruit secevențial și cum se descrie acesta în Verilog.

Cuvinte cheie: clock, flip-flop, circuit sincron/ asincron, atribuire blocking/ non-blocking

Sintaxă Verilog: always, initial, forever

Circuitele digitale pot fi de două tipuri:

- circuite logice combinaționale (CLC) - pot fi descrise fie folosind instrucțiuni de tip assign, fie folosind procese de tip always

- circuite secvențiale - pot fi descrise folosind doar procese de tip always

Exerciţiul 1

Să se descrie în Verilog un bistabil D cu următoarele caracteristici:

- semnal de ceas activ pe frontul pozitiv

- semnal de reset sincron cu ceasul, activ pe palierul de 0

Explicaţie suplimentară

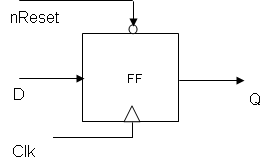

Circuitul cel mai des folosit pentru a sincroniza un semnal oarecare cu ceasul este bistabilul D (numit și flip-flop FF). Bistabilul D din exemplul 3 are următoarele porturi:

- Clk – intrarea de ceas, activă pe frontul pozitiv

- D – intrarea de date

- nReset – intrare asincronă/sincronă cu semnalul de ceas; nReset activ pe palierul de 0

- Q – ieşirea circuitului

Faptul că nReset e o intrare asincronă cu ceasul, în contextul procesului always, înseamnă că atunci când nReset devine activ (adică 0), indiferent de valoarea prezentă pe intrarea de date D, ieşirea circuitului va deveni 0 instantaneu.

În schimb, dacă nReset e o intrare sincronă cu ceasul, în contextul procesului always, acest lucru înseamnă că, atunci când nReset devine activ (adică 0), indiferent de valoarea prezentă pe intrarea de date D, ieşirea circuitului va deveni 0 doar în momentul când apare frontul activ al ceasului.

Observație: Semnalul de reset va fi întotdeauna sincron cu ceasul, adica își va schimba valoarea din 1 în 0 sau invers întotdeauna pe frontul activ al ceasului!!!

Descrierea unui bistabil în Verilog la nivel RTL este posibilă doar folosind procese de tip always, având în lista de sensitivități cel puțin frontul pozitiv al ceasului.

Mai mult, în procesele cu ceas, se atribuie valori semnalelor folosind atribuirea de tip non-blocking (cu operatorul <=, care în acest context înseamnă "ia valoarea", şi NU mai mic sau egal!!!), spre deosebire de procesele always ce descriu circuite pur combinaționale și unde atribuirea de valori noi se face folosind doar atribuirea de tip blocking (cu operatorul =).

Exerciţiul 2

Descrieți în Verilog un semnal de ceas cu perioada 6 unități de timp.

Explicaţie suplimentară

Pe ieșirile unui CLC poate să apară hazard. Pentru a elimina hazardul, ieșirile unui CLC pot fi sincronizate cu un semnal suplimentar, numit semnal de ceas (clock). Semnalul de ceas are următoarele proprietăți:

- Este semnal dreptunghiular (la fel ca toate celelalte semnale digitale)

- Este un semnal periodic

- Este singurul semnal dintr-un sistem digital care este activ pe front. Toate celelalte semnale prezente într-un sistem digital sunt active pe palier.

Exerciţiul 3

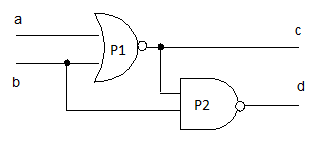

Descrieți în Verilog circuitul din figura 1, folosind o instrucțiune assign, respectiv un proces always.

Explicaţie suplimentară

Când utilizați assign - semnalul trebuie declarat de tip wire.

Când utilizați always - semnalul trebuie declarat de tip reg.

Exerciţiul 4

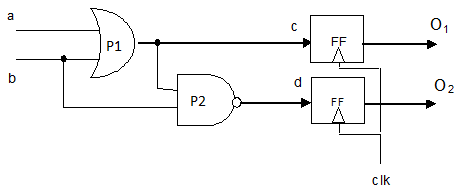

Să se descrie în Verilog circuitul din figura 3 în două moduri:

- separând partea combinațională de cea secvențială (folosind 2 procese always)

- folosind un singur proces always

Exemplul 5

Să se descrie în Verilog un numărător complet (in, reset, load, enable, up/down, out). Simulați acest numărător. Considerați intrarile pe 4 biți.

Evidențiați formele de unda de pe iesirea numaratorului! Ce observați?

Exerciţiul 6

Simulați și comparați următoarele circuite (refolosiți un testbench din exemplul 7):

Circuitul 1:

always@(posedge clk) begin

if (nReset == 0) begin

b <= 0;

c <= 0;

end else begin

b <= a;

c <= b;

end

end

Circuitul 2:

always@(posedge clk) begin

if (nReset == 0) begin

b = 0;

c = 0;

end else begin

b = a;

c = b;

end

end

Observație: Pentru descrierea circuitelor sincrone cu ceasul se folosește întotdeauna atribuirea non-blocking <=.

Explicatii suplimentare

Mai mult, modalitatea in care se atribuie valori semnalelor este recomandata a fi de tip non-blocking (cu operatorul <=, care în acest context înseamnă săgeată spre stânga, adică “ia valoarea”, şi NU mai mic sau egal!!!), spre deosebire de procesele always ce descriu circuite pur combinationale si unde atribuirea de valori noi se face folosind doar atribuirea de tip blocking (cu operatorul =).

Iata diferenta intre tipul de atribuire blocking si cea non-blocking:

Spre deosebire de atribuirea blocking (=), atribuirea non-blocking (<=) nu actualizeaza imediat semnalul reg din stânga, ci doar la sfârşitul pasului de simulare curent.

Iata un exemplu: descrierea mai multor bistabili în procese diferite, folosind atribuirea blocking:

always @(posedge clock)

b = a;

always @(posedge clock)

c = b;

În acest caz particular, la sosirea unui front pozitiv al ceasului în simulare ambele procese sunt executate. Este însă imposibil de spus care va fi primul proces executat de simulator. Apar două cazuri posibile: Fie cele două procese sunt executate în ordinea în care au fost scrise. În acest caz, B va fi updatat primul şi noua valoare a lui B va fi folosită pentru a-l updata pe C. Deci B şi C vor avea aceeaşi valoare, mai exact valoarea A!

Fie cele două procese always vor fi executate în ordinea inversă. În acest caz, lui C i se va atribui vechea valoare a lui B, apoi B va fi updatat cu valoarea A.

Astfel, pot apărea diferenţe între rezultatele obţinute în urma simulării folosind tool-uri de simulare diferite, dar pot apărea diferenţe şi între rezultatele simulării descrierii RTL şi a simulării post-layout! Iata ce se intampla insa, daca implementam cei doi FFs folosind atribuiri non-blocking:

always @(posedge clock)

b <= a;

always @(posedge clock)

c <= b;

In acest caz, B şi C nu primesc valori noi decât după cele ambele atribuiri au fost executate, adică pe frontul pozitiv următor! Astfel, schema ce va fi simulată va fi identică cu cea generată în urma sintezei codului RTL.

Temă

- Descrieți în Verilog și simulați un circuit de numărare folosind un bistabil cu intrare de Set asincronă cu ceasul şi activă pe palierul de 1 și intrare de Load sincronă cu ceasul, activă pe palierul de 1. Când Load este activ, numărătorul se încarcă cu o valoare Data_In.

- Descrieți și simulați funcționarea unui registru de deplasare la stânga, folosind operatorul de shiftare <<, respectiv cel de concatenare {}.

- Descrieți și simulați un registru de deplasare la stânga circular (MSB devine LSB).