Diferență între revizuiri ale paginii „Tutorial Xilinx ISim”

| Linia 17: | Linia 17: | ||

[[Fișier:isim4.png|500px]] | [[Fișier:isim4.png|500px]] | ||

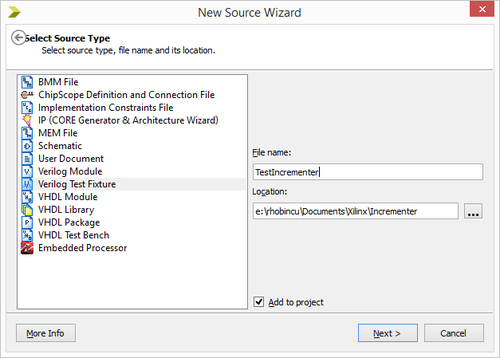

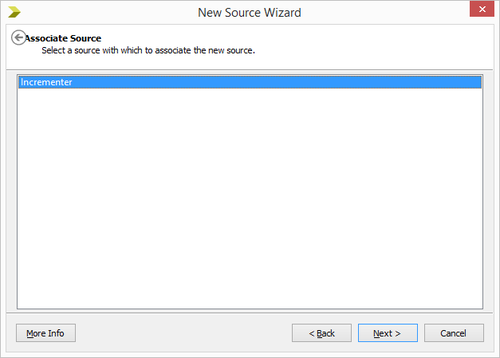

| − | În continuare vi se va cere tipul de sursă pe care doriți să o creați (selectați '''Verilog Module'''), numele fișierului (vom tasta '''Incrementer'''), și calea până la directorul în care se va salva (îl vom lăsa implicit). Apoi se | + | În continuare vi se va cere tipul de sursă pe care doriți să o creați (selectați '''Verilog Module'''), numele fișierului (vom tasta '''Incrementer'''), și calea până la directorul în care se va salva (îl vom lăsa implicit). Apoi se dă click pe '''Next >''': |

[[Fișier:isim5.png|500px]] | [[Fișier:isim5.png|500px]] | ||

| + | |||

| + | Vor mai apărea două ferestre în care se pot configura din interfață numărul și tipul porturilor modulului. Cum noi vom face asta manual, nu completați nimic și dați click pe '''Next >''', iar apoi pe '''Finish'''. | ||

| + | |||

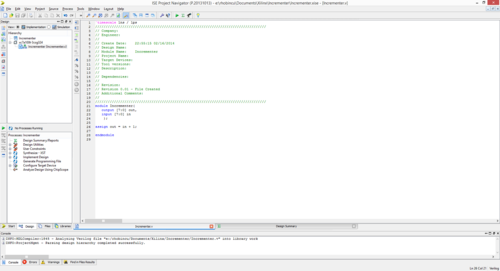

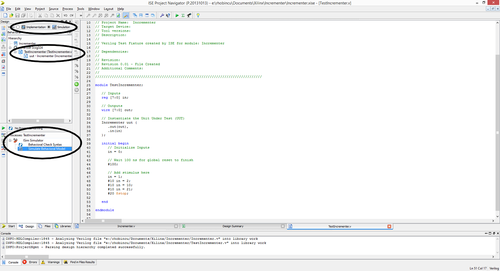

| + | În acest moment noua sursă este adăugată la proiect (și se vede în zona de ierarhie din stânga sus) iar fișierul este deschis automat pentru editare. Completați codul astfel încât să arate ca în figură: | ||

| + | |||

[[Fișier:isim6.png|500px]] | [[Fișier:isim6.png|500px]] | ||

| + | |||

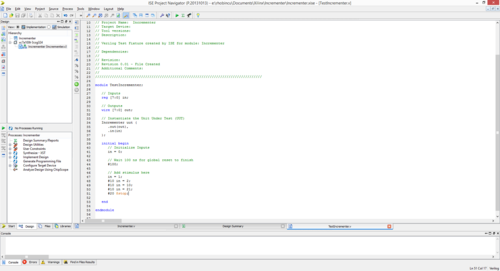

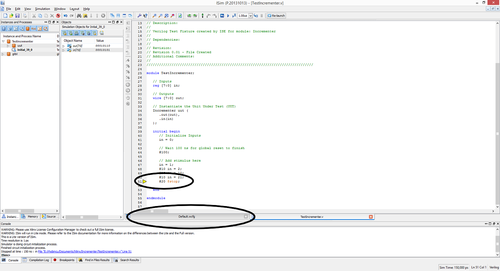

| + | După salvarea fișierului sursă, în continuare trebuie să realizâm un modul de test. Pentru asta, vom repeta operația de adăugarea a unei noi surse (prin click-dreapta pe fereastra de ierarhie, unde acum exisă modulul '''Incrementer'''), doar că acum vom selecta tipul '''Verilog Test Fixture''', iar numele fișierului va fi '''TestIncrementer''': | ||

| + | |||

[[Fișier:isim7.png|500px]] | [[Fișier:isim7.png|500px]] | ||

| + | |||

| + | |||

| + | |||

[[Fișier:isim8.png|500px]] | [[Fișier:isim8.png|500px]] | ||

[[Fișier:isim9.png|500px]] | [[Fișier:isim9.png|500px]] | ||

Versiunea de la data 16 februarie 2014 21:53

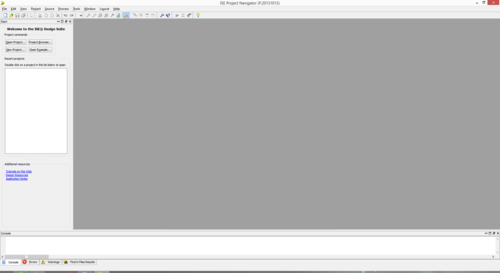

Orice simulare în Xilinx ISim începe cu un nou proiect, fie prin selectarea File->New Project, fie prin apăsarea butonului New Project de pe fereastra inițială:

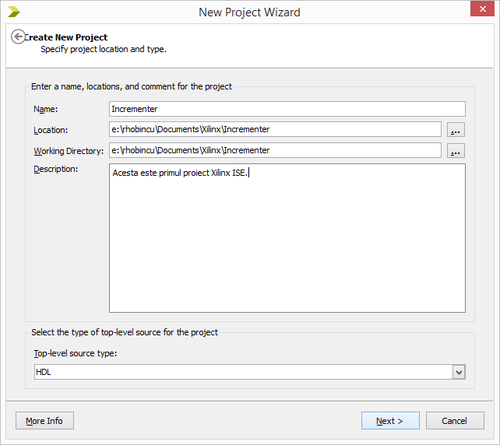

În fereastra care se deschide, sunteți invitați să completați numele proiectului, calea până la directorul în care vor fi salvate fișierele (pentru laborator, selectati /home/student/ise), precum și o scurtă descrie opțională. Apoi apăsați Next >:

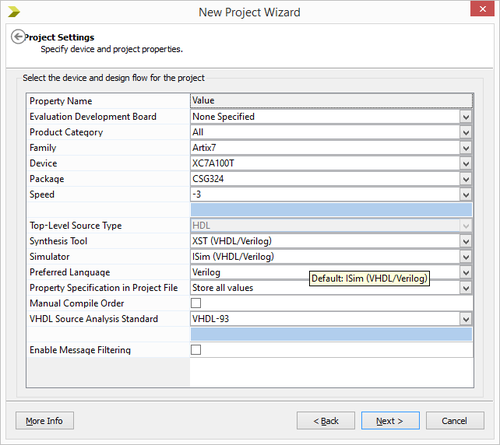

Următoarea fereastră conține un număr de setări ce au legătură cu modelul de FPGA folosit pentru sinteză. Aceste setări vor fi relevante pentru laborator. Acum, verificați doar că simulatorul ales este ISim, apoi dați click pe Next >:

Va apărea o nouă fereastă cu un sumar al opțiunilor alese, după care, apăsând pe Finish, proiectul se va crea efectiv.

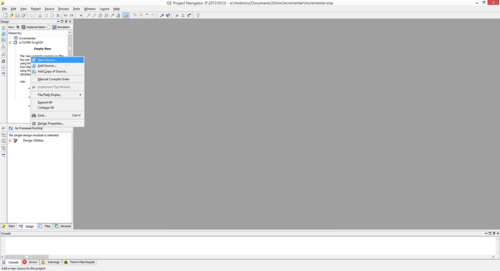

Următorul pas este să adăugăm fișiere la proiect. Acest lucru se realizează simplu, dând click-dreapta pe zona ierarhiei din stânga sus, acolo unde acum scrie Empty View și selectând New Source... din meniul contextual:

În continuare vi se va cere tipul de sursă pe care doriți să o creați (selectați Verilog Module), numele fișierului (vom tasta Incrementer), și calea până la directorul în care se va salva (îl vom lăsa implicit). Apoi se dă click pe Next >:

Vor mai apărea două ferestre în care se pot configura din interfață numărul și tipul porturilor modulului. Cum noi vom face asta manual, nu completați nimic și dați click pe Next >, iar apoi pe Finish.

În acest moment noua sursă este adăugată la proiect (și se vede în zona de ierarhie din stânga sus) iar fișierul este deschis automat pentru editare. Completați codul astfel încât să arate ca în figură:

După salvarea fișierului sursă, în continuare trebuie să realizâm un modul de test. Pentru asta, vom repeta operația de adăugarea a unei noi surse (prin click-dreapta pe fereastra de ierarhie, unde acum exisă modulul Incrementer), doar că acum vom selecta tipul Verilog Test Fixture, iar numele fișierului va fi TestIncrementer: