Diferență între revizuiri ale paginii „CID Seminar 1”

| Linia 1: | Linia 1: | ||

În acest seminar veţi învăţa să descrieţi unele circuite digitale simple în limbajul Verilog şi să folosiţi programul Xilinx ISim pentru a simula funcţionarea acestora. | În acest seminar veţi învăţa să descrieţi unele circuite digitale simple în limbajul Verilog şi să folosiţi programul Xilinx ISim pentru a simula funcţionarea acestora. | ||

| + | Un scurt tutorial pentru folosirea programului Xilinx ISim găsiţi [[Tutorial Xilinx ISim|aici]]. | ||

| − | '''Cuvinte cheie:''' formă de undă, proiect, modul, instanţiere, testbench | + | '''Cuvinte cheie:''' porți logice, porturi, formă de undă, proiect, modul, instanţiere, testbench |

| − | '''Sintaxa Verilog:''' ''module'', '' | + | '''Sintaxa Verilog:''' ''module'', ''wire'', ''reg'', ''initial'', ''$stop'' |

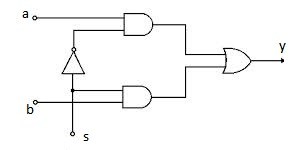

| − | + | Verilog este un limbaj de descriere hardware (hardware description language). În acest limbaj putem descrie circuite digitale precum cel din figura 1. | |

| − | |||

| − | |||

| − | == | + | == Exercițiul 1== |

| − | + | În figura 1 este reprezentată schema unui circuit digital care conține porți logice. Descrieți această schemă în limbajul Verilog. | |

[[Fișier:sem1ex1.png|Schema bloc pentru exemplul 1]] | [[Fișier:sem1ex1.png|Schema bloc pentru exemplul 1]] | ||

| − | < | + | '''Explicații''': Porțile logice sunt predefinite în Verilog: '''not''', '''and''', '''nand''', '''or''', '''nor''', '''xor''', '''nxor'''. Sintaxa corectă este, pentru poarta '''and''': |

| + | |||

| + | <syntaxhighlight lang="verilog"> | ||

| + | and nume_poarta (iesire, intrare_1, intrare_2, …. intrare_n); | ||

| + | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | |||

| − | + | ==Exercițiul 2== | |

| − | |||

| − | |||

| − | + | Creați un fișier Verilog care descrie circuitul de la exercițiul 1. | |

| − | |||

| − | |||

| − | + | '''Explicații:''' | |

| − | + | Descrierea unui circuit include: | |

| + | *interfața (declararea porturilor de intrare și ieșire) | ||

| + | *descrierea funcției sau a schemei circuitului | ||

| + | |||

| + | În Verilog, descrierile circuitelor sunt alcătuite din module. Sintaxa este următoarea: | ||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

module circuitul_meu(lista_porturi); /* porturile sunt conexiunile externe ale circuitului*/ | module circuitul_meu(lista_porturi); /* porturile sunt conexiunile externe ale circuitului*/ | ||

| − | + | //declaraţi mai întâi porturile | |

| − | + | //apoi daţi detaliile funcţionale sau structurale | |

endmodule | endmodule | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ==Exercițiul 3== | |

| − | |||

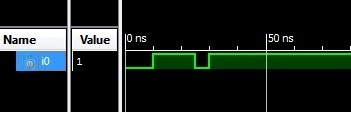

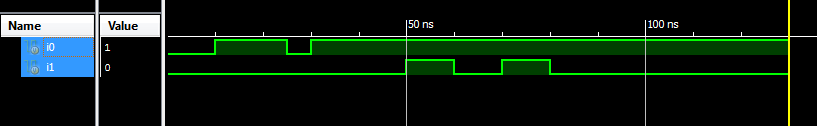

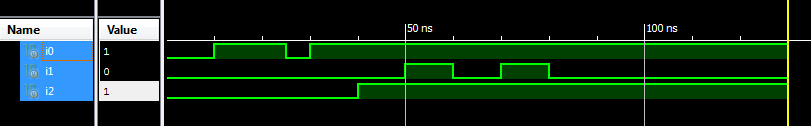

| − | + | Generați formele de undă din figurile următoare în simulatorul ISim. | |

| + | # Semnalul i0: | ||

| + | [[Fișier:cid_sem1_img2.png|Semnal i0]] | ||

| + | # Două semnale, i0 și i1: | ||

| + | [[Fișier:cid_sem1_img3.png|Semnale i0 și i1]] | ||

| + | # Trei semnale: | ||

| + | [[Fișier:cid_sem1_img4.png|Trei semnale]] | ||

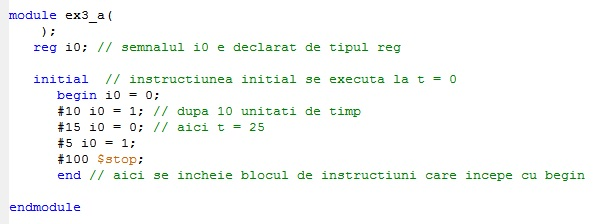

| − | + | <u>Rezolvare punctul 1:</u> | |

| − | + | Se va scrie un fișier sursă nou, care nu are porturi exterioare (deoarece nu descrie un circuit). | |

| + | [[Fișier:cid_sem1_img5.png|Cod sursă exercițiul 3]] | ||

| − | |||

| − | |||

| − | + | ==Exemplul 4== | |

| + | Simulați funcționarea modulului de la exercițiul 2, aplicând pe intrare semnalele de la exercițiul 3 – punctul 3. | ||

| + | Știind că acest circuit este un multiplexor (circuit de selecție), analizați formele de undă pentru a vedea dacă sunt corecte. Modificați eventual forma de undă pe intrarea s și verificați funcționarea corectă. | ||

| − | + | '''Explicații:''' Pentru a simula funcționarea unui circuit, trebuie să realizăm o platformă de test (Testbench) descrisă într-un nou modul. Aplicăm semnalele respective pe intrarea circuitului testat – instanțiem circuitul respectiv. Simulăm modulul de test și apoi analizăm formele de undă pentru a vedea dacă acestea corespund funcției implementate. | |

| − | + | ==Exercițiul 5== | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | Desenaţi schema descrisă de următorul cod Verilog: | |

| − | + | <syntaxhighlight lang="verilog"> | |

| + | circuit1 ana (.in1(a), .in2 (b), .out1(int), .out2(en)); | ||

| + | circuit2 doru(.in3(int), .in4 (b), .out(c)); | ||

| + | circuit3 zuzu(.in0(en), .in1(c), .out(out)); | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ... unde modulele au porturile declarate astfel: | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

| − | module | + | module circuit1 ( |

| − | + | input [3:0] in1, in2, | |

| − | + | output [3:0] out1, | |

| − | + | output out2); | |

| + | ... | ||

endmodule | endmodule | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | module circuit2 ( | |

| − | module | + | input [3:0] in3, in4, |

| − | + | output [3:0] out); | |

| − | |||

| − | |||

| − | |||

... | ... | ||

endmodule | endmodule | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | module circuit3 ( | |

| − | module | + | input [3:0] in1, |

| − | + | input in0, | |

| − | + | output [3:0] out); | |

... | ... | ||

endmodule | endmodule | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ===Porţi logice în Verilog=== | |

| + | În Verilog, porțile logice elementare sunt predefinite ca primitive, există deci cuvinte speciale de limbaj. | ||

| − | + | Pentru funcția ŞI: | |

| − | + | <syntaxhighlight lang="verilog"> | |

| − | + | and (out, in1, in2,..., ink); // intotdeauna prima e iesirea | |

| − | + | and P1(out, in1, in2); // este bine sa dam si un nume fiecarei porti | |

| − | + | </syntaxhighlight> | |

| − | + | ||

| − | + | Celelalte porţi logice sunt: ''nand'', ''or'', ''nor'', ''xor'', ''xnor''. | |

| − | + | La toate aceste porţi, implicit prima este ieşirea şi se pot pune oricâte intrări. | |

'''Observaţie''': Notaţiile simple folosite pentru funcţii logice în scrierea curentă nu sunt identice cu simbolurile operatorilor din Verilog. | '''Observaţie''': Notaţiile simple folosite pentru funcţii logice în scrierea curentă nu sunt identice cu simbolurile operatorilor din Verilog. | ||

| Linia 149: | Linia 128: | ||

| NOT || ' || ~ | | NOT || ' || ~ | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==Temă== | ==Temă== | ||

Versiunea de la data 23 februarie 2015 10:42

În acest seminar veţi învăţa să descrieţi unele circuite digitale simple în limbajul Verilog şi să folosiţi programul Xilinx ISim pentru a simula funcţionarea acestora.

Un scurt tutorial pentru folosirea programului Xilinx ISim găsiţi aici.

Cuvinte cheie: porți logice, porturi, formă de undă, proiect, modul, instanţiere, testbench

Sintaxa Verilog: module, wire, reg, initial, $stop

Verilog este un limbaj de descriere hardware (hardware description language). În acest limbaj putem descrie circuite digitale precum cel din figura 1.

Exercițiul 1

În figura 1 este reprezentată schema unui circuit digital care conține porți logice. Descrieți această schemă în limbajul Verilog.

Explicații: Porțile logice sunt predefinite în Verilog: not, and, nand, or, nor, xor, nxor. Sintaxa corectă este, pentru poarta and:

and nume_poarta (iesire, intrare_1, intrare_2, …. intrare_n);

Exercițiul 2

Creați un fișier Verilog care descrie circuitul de la exercițiul 1.

Explicații: Descrierea unui circuit include:

- interfața (declararea porturilor de intrare și ieșire)

- descrierea funcției sau a schemei circuitului

În Verilog, descrierile circuitelor sunt alcătuite din module. Sintaxa este următoarea:

module circuitul_meu(lista_porturi); /* porturile sunt conexiunile externe ale circuitului*/

//declaraţi mai întâi porturile

//apoi daţi detaliile funcţionale sau structurale

endmodule

Exercițiul 3

Generați formele de undă din figurile următoare în simulatorul ISim.

- Semnalul i0:

- Două semnale, i0 și i1:

- Trei semnale:

Rezolvare punctul 1:

Se va scrie un fișier sursă nou, care nu are porturi exterioare (deoarece nu descrie un circuit).

Exemplul 4

Simulați funcționarea modulului de la exercițiul 2, aplicând pe intrare semnalele de la exercițiul 3 – punctul 3. Știind că acest circuit este un multiplexor (circuit de selecție), analizați formele de undă pentru a vedea dacă sunt corecte. Modificați eventual forma de undă pe intrarea s și verificați funcționarea corectă.

Explicații: Pentru a simula funcționarea unui circuit, trebuie să realizăm o platformă de test (Testbench) descrisă într-un nou modul. Aplicăm semnalele respective pe intrarea circuitului testat – instanțiem circuitul respectiv. Simulăm modulul de test și apoi analizăm formele de undă pentru a vedea dacă acestea corespund funcției implementate.

Exercițiul 5

Desenaţi schema descrisă de următorul cod Verilog:

circuit1 ana (.in1(a), .in2 (b), .out1(int), .out2(en));

circuit2 doru(.in3(int), .in4 (b), .out(c));

circuit3 zuzu(.in0(en), .in1(c), .out(out));

... unde modulele au porturile declarate astfel:

module circuit1 (

input [3:0] in1, in2,

output [3:0] out1,

output out2);

...

endmodule

module circuit2 (

input [3:0] in3, in4,

output [3:0] out);

...

endmodule

module circuit3 (

input [3:0] in1,

input in0,

output [3:0] out);

...

endmodule

Porţi logice în Verilog

În Verilog, porțile logice elementare sunt predefinite ca primitive, există deci cuvinte speciale de limbaj.

Pentru funcția ŞI:

and (out, in1, in2,..., ink); // intotdeauna prima e iesirea

and P1(out, in1, in2); // este bine sa dam si un nume fiecarei porti

Celelalte porţi logice sunt: nand, or, nor, xor, xnor. La toate aceste porţi, implicit prima este ieşirea şi se pot pune oricâte intrări.

Observaţie: Notaţiile simple folosite pentru funcţii logice în scrierea curentă nu sunt identice cu simbolurile operatorilor din Verilog.

| Funcţie logică | Simbol | operator Verilog |

|---|---|---|

| ȘI | • (se poate omite) | & |

| SAU | + | | |

| XOR | ⊕ | ^ |

| NOT | ' | ~ |

Temă

- Descrieţi structural în Verilog circuitul din figură (veţi descrie efectiv schema cu porţi logice). Atenţie! trebuie definite toate interconexiunile ca wire.

- Descrieţi comportamental acelaşi circuit (folosind operatori logici şi instrucţiunea assign).

- Descrieţi în Verilog modulele componente ale circuitului din exemplul 5 (diferența, complement, mux) astfel încât să realizeze funcţiile precizate şi testaţi distinct fiecare modul în parte. Indicaţie: Modulul pentru multiplexor poate fi descris folosind instrucţiunea de atribuire condiţionată care este explicată în seminarul 2 (dar o puteţi găsi şi aici)

- Simulaţi funcţionarea întregului circuit din exemplul 5. Indicaţie: Trebuie să descrieti mai întâi modulul Top, care cuprinde cele trei instanţieri.

Reguli de bună practică

Organizarea fişierelor

- Salvaţi modulele pe care le scrieţi în fişiere distincte.

- Numele fişierului să fie identic cu numele modulului.

- Pentru simulare, folosiţi un folder distinct.

Scrierea codului

- Daţi nume sugestive modulelor, porturilor şi semnalelor.

- Introduceţi comentarii pentru documentarea codului.

- Folosiţi tab-uri şi linii goale pentru alinierea şi gruparea blocurilor de instrucţiuni.