Diferență între revizuiri ale paginii „Laboratorul 4”

(Pagină nouă: == Arhitectura Harvard == Arhitectura de calculator Harvard are magistrale distincte pentru accesul la program și la date, permițând astfel citirea unei instrucțiuni în paral...) |

|||

| Linia 4: | Linia 4: | ||

[[Fișier: asc_lab4_harvard.png]] | [[Fișier: asc_lab4_harvard.png]] | ||

| + | |||

| + | == Procesorul pipeline == | ||

| + | |||

| + | Procesorul are o structură pipeline cu trei niveluri: | ||

| + | # FETCH - citirea instrucțiunii din memoria de program | ||

| + | # READ - citirea operanzilor din setul de registre | ||

| + | # EXECUTE - execuția operației instrucțiunii/accesul în memoria de date | ||

| + | |||

| + | [[Fișier: asc_lab4_procesor.png]] | ||

| + | |||

| + | În această lucrare de laborator se va implementa un procesor pipeline fără gestiunea dependențelor de date sau de control, ce procesează setul de instrucțiuni din laboratoarele precedente. Implementarea va reutiliza integral blocurile ALU și REGS proiectate în laboratorul 1, și cu mici modificări memoria din laboratorul 2. | ||

| + | |||

| + | Schema detaliată a structurii pipeline pune în evidență căile de date și semnalele de control. | ||

Versiunea de la data 7 noiembrie 2019 01:20

Arhitectura Harvard

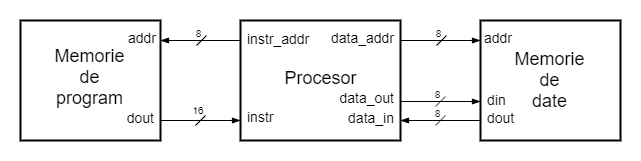

Arhitectura de calculator Harvard are magistrale distincte pentru accesul la program și la date, permițând astfel citirea unei instrucțiuni în paralel cu citirea sau scrierea datei altei instrucțiuni. Programul și datele se află în memorii separate sau într-o memorie comună dar cu porturi multiple de acces.

Procesorul pipeline

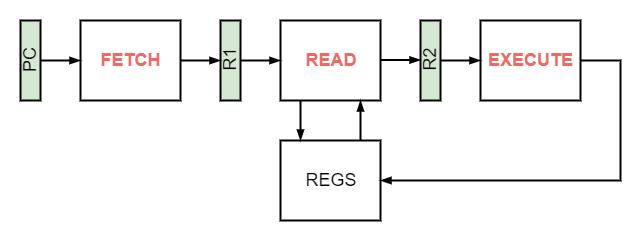

Procesorul are o structură pipeline cu trei niveluri:

- FETCH - citirea instrucțiunii din memoria de program

- READ - citirea operanzilor din setul de registre

- EXECUTE - execuția operației instrucțiunii/accesul în memoria de date

În această lucrare de laborator se va implementa un procesor pipeline fără gestiunea dependențelor de date sau de control, ce procesează setul de instrucțiuni din laboratoarele precedente. Implementarea va reutiliza integral blocurile ALU și REGS proiectate în laboratorul 1, și cu mici modificări memoria din laboratorul 2.

Schema detaliată a structurii pipeline pune în evidență căile de date și semnalele de control.