CID Seminar 1

În acest seminar veţi învăţa să descrieţi unele circuite digitale simple în limbajul Verilog şi să folosiţi programul Xilinx ISim pentru a simula funcţionarea acestora.

Cuvinte cheie: formă de undă, proiect, modul, instanţiere, testbench

Sintaxa Verilog: module, assign, initial, $stop

În domeniul digital, toate sistemele, circuitele şi blocurile funcţionale sunt conectate între ele numai prin semnale digitale, adică dreptunghiulare (care pot lua doar două valori, 0 si 1).

Cum obţinem formele de undă de la ieşirea unui circuit?

Descriem circuitul într-o manieră inteligibilă (folosind un HDL – în cazul nostru, Verilog). Aplicăm semnale pe intrare şi apoi simulăm funcţionarea, folosind un simulator (aici, Xilinx ISim).

Exemplul 1

Descrieţi în Verilog un circuit de incrementare pentru numere binare pe 4 biţi şi testaţi funcţionarea acestui circuit, folosind modulul test_inc, cu ajutorul programului Model Sim.

Explicaţii suplimentare

Descrierea unui circuit include:

- descrierea interfetei (declararea porturilor)

- descrierea funcţiei (ce face circuitul? în esenţă, cum depind ieşirile de intrări)

Circuitul din acest exemplu are o intrare (in), pe 4 biţi şi o ieşire (out), pe 5 biţi. Bus-urile sunt semnale pe mai mulţi biţi care au o semnificaţie comună, este mai avantajos să îi definim împreună. Funcţia realizată de circuit este out = in + 1.

Regulă: Descrierile circuitelor în Verilog sunt alcătuite din module.

Intrările în Verilog se definesc cu cuvântul input, ieşirile sunt output. Orice modul începe cu cuvântul module şi se termină cu endmodule. Modulele nu se pot suprapune şi nu pot fi incluse unele în altele.

module circuitul_meu(lista_porturi); /* porturile sunt conexiunile externe ale circuitului*/

……//declaraţi mai întâi porturile

……//apoi daţi detaliile funcţionale

endmodule

Liniile de cod în Verilog se încheie cu ";" (există şi excepţii pe care le vom menţiona explicit, de exemplu după ultima linie – endmodule – de mai sus. În principiu, ";" determină o acţiune). Comentariile se introduc cu // sau cu /*....*/, vor apărea scrise în editorul programului cu verde şi sunt ignorate la compilare.

Un scurt tutorial pentru folosirea programului Xilinx ISim găsiţi aici.

Simularea funcţionării circuitelor

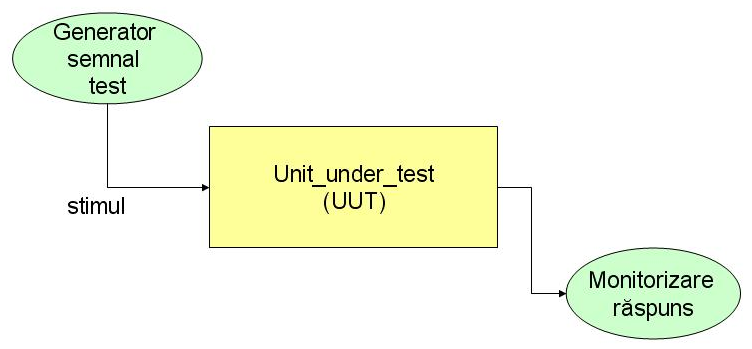

Pentru a verifica funcţionarea corectă a unui circuitul trebuie să îi aplicăm semnale pe intrare şi să verificăm dacă ieşirea este aşa cum ne-am aşteptat, altfel spus simulăm fucţionarea acestuia. Definim un circuit care este de fapt o platformă de testare (testbench).

Acesta circuit este un modul distinct, special pentru testare, numit de obicei modul de test. Modulul de test nu are conexiuni externe, dar face referinţă la modulul pe care l-am descris anterior.

module test_inc (); //nu are porturi externe, “()” poate lipsi

reg [3:0] a; // aici am definit o variabila pe 4 biti

wire [4:0] b; // aici am definit o conexiune, un “fir” pe 5 biti

//urmeaza generarea semnalelor care vor fi aplicate pe INTRARI

initial begin // intructiunile initial se executa la t = 0

a=0;

#10 a=5; /* #10 reprezinta o intarziere de 10 unitati timp, care se

aduna la intarzierea anterioara, in acest caz la t=0. Deci t

devine t = 10 */

#10 a=8; // aici suntem la t = 20

#15 a=15;

#5 a=4’b0001; // a este de fapt un semnal pe patru biti

#5 a=4’b0100;

#30 $stop; // va opri simularea, este bine sa nu lipseasca

end // dupa begin si end nu se pune “;”

inc dut(a, b); // atentie! modulul de incrementare trebuie denumit inc

endmodule

Exemplul 2

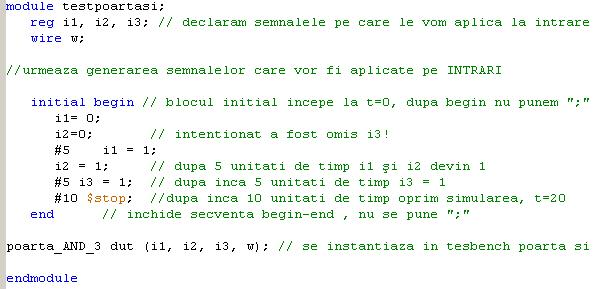

- Descrieţi în Verilog o poartă ŞI cu trei intrări.

- Testaţi funcţionarea acestei porţi.

Explicaţii suplimentare

Principalele funcţii logice (şi porţile logice corespunzătoare) sunt prezentate aici. Funcţia ŞI (AND) cu trei intrări ia valoarea 1 numai dacă toate intrările sunt 1, în rest ia valoarea 0.

Definirea porturilor unui circuit se poate face:

- în corpul modulului

- compactat, în lista porturilor

Varianta1 (Verilog '95)

module poarta_AND_3 (a, b, c, out);

input a, b, c; // putem pune mai multe pe aceeasi linie, separate cu ,

output out;

.....

endmodule

Varianta 2. (Verilog 2001)

module poarta_AND_3 (

input a, // scriem cu tab-uri ca sa fie vizibile

input b,

input c,

output out);

...

endmodule

Aici avem mai multe intrări pe 1 bit deci putem scrie şi

module poarta_AND_3 (

input a, b, c, // scriem cu tab-uri ca sa fie vizibile

output out);

...

endmodule

Vom verifica funcţionarea corectă cu modulul de test.

Completaţi formele de undă la intrare cu mai multe combinaţii logice. Simulaţi funcţionarea circuitului.

Exemplul 3

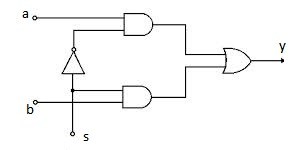

Folosiţi modulul anterior de test pentru a testa funcţionarea unui circuit care calculează funcţia logică out=ac+b.