CID Lab Lucrarea 1

Noțiuni și cunoștințe necesare

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Logică booleană și sisteme de numerație

- Noțiuni de sintaxă Verilog

Exemplu

Creați un proiect nou în Xilinx ISE, pentru dispozitivul FPGA de pe placa Nexys2. Creați un fișier sursă Verilog în cadrul proiectului, și copiați modulul următor în fisier.

module OrGate(

output out,

input in1,

input in2

);

assign out = in1 | in2;

endmodule

Creați un fișier de constrângeri și scrieți constrângerile necesare pentru ca intrările și ieșirile circuitului să fie conectate astfel:

- in1 conectat la SW0: "NET in1 LOC=G18;"

- in2 conectat la SW7: "NET in2 LOC=R17;"

- out conectat la LD3: "NET out LOC=K14;"

Implementați proiectul pe placa Nexys și observați funcționalitatea circuitului descris de proiectul Xilinx ISE.

Exercițiul 1

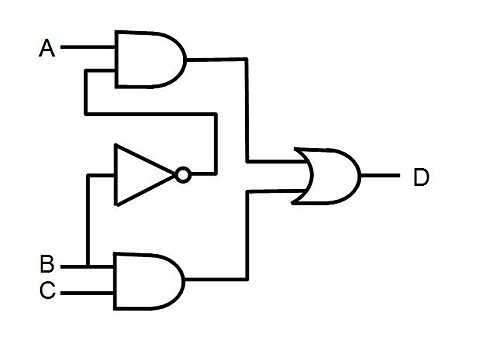

Realizați descrierea în Verilog a modulului cu intrările A, B, C și ieșirea D, cu funcționalitatea conform schemei alăturate. Implementați circuitul pe placa Nexys2 conectând intrările A, B, C la SW2, SW4, respectiv SW6, iar ieșirea D la LD2.

Exercițiul 2

Realizați descrierea în Verilog a modulului cu intrările A, B, C și ieșirea D, cu funcționalitatea conform schemei alăturate. Implementați circuitul pe placa Nexys2 conectând intrările A, B, C la SW3, SW4, respectiv SW7, iar ieșirea D la LD7.

Exercițiul 3

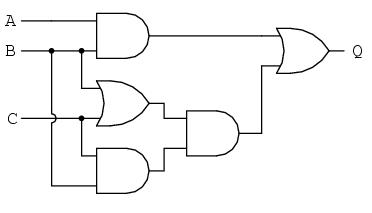

Realizați descrierea în Verilog a modulului cu intrările A, B, C și ieșirea Q, cu funcționalitatea conform schemei alăturate. Implementați circuitul pe placa Nexys2 conectând intrările A, B, C la SW1, SW6, respectiv SW7, iar ieșirea Q la LD3.

Exercițiul 4

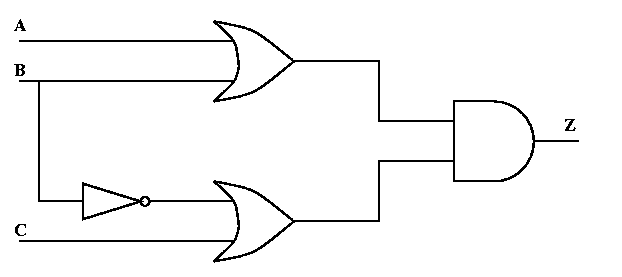

Realizați descrierea în Verilog a modulului cu intrările A, B, C și ieșirea Z, cu funcționalitatea conform schemei alăturate. Implementați circuitul pe placa Nexys2 conectând intrările A, B, C la SW3, SW4, respectiv SW5, iar ieșirea Z la LD6.

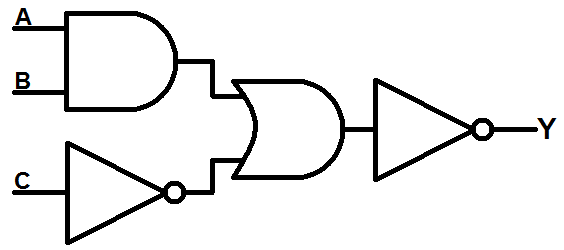

Exercițiul 5

Realizați descrierea în Verilog a modulului cu intrările A, B, C și ieșirea Y, cu funcționalitatea conform schemei alăturate. Implementați circuitul pe placa Nexys2 conectând intrările A, B, C la SW5, SW6, respectiv SW7, iar ieșirea Y la LD4.

Recomandări pentru cadrele didactice

- Parcurgerea tutorialului Introducere în sinteza pe FPGA. Xilinx ISE, răspunzându-se la întrebările studenților.

- Implementarea unui exemplu de proiect Xilinx ISE, parcurgându-se tutorialul Xilinx ISE.