Tutorial Xilinx ISE (14.7)

Crearea unui proiect

Pentru a porni programul Xilinx ISE în laborator, apăsați tasta F12, în consola care apare tastați comanda ise&, și mai apăsați o data F12. Odată pornită aplicația, aceasta va arăta într-un mod similar cu cel de mai jos:

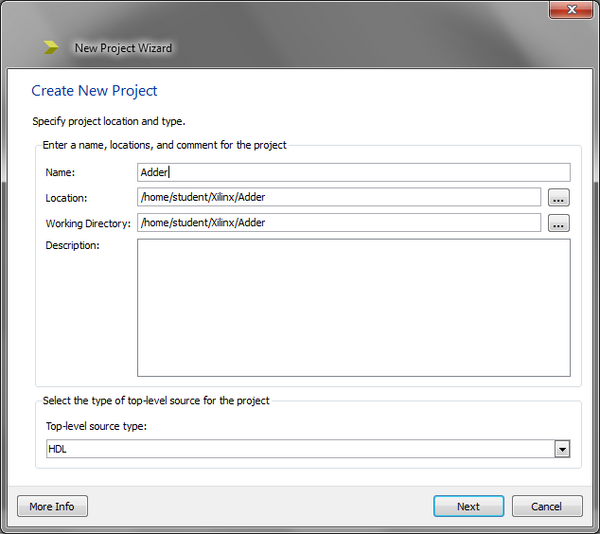

Vom continua acest tutorial cu sinteza circuitului de adunare a cărui simulare a fost prezentată în lucrarea de laborator precedentă. Ca şi în cazul programului Modelsim, prima operație este de a creea un proiect nou. După ce dați click pe File -> New Project vi se va deschide următoarea fereastră:

Modifcați întâi locația proiectului să fie /home/student/Xilinx și apoi dați un nume proiectului, în cazul nostru Adder. Mai departe vi se va afișa următoarea fereastră:

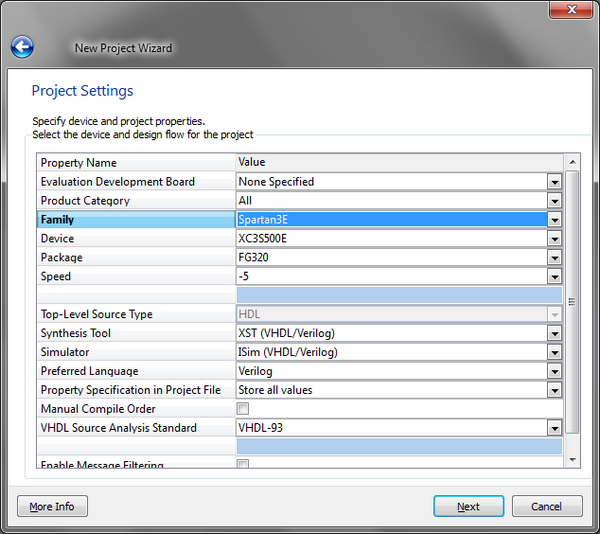

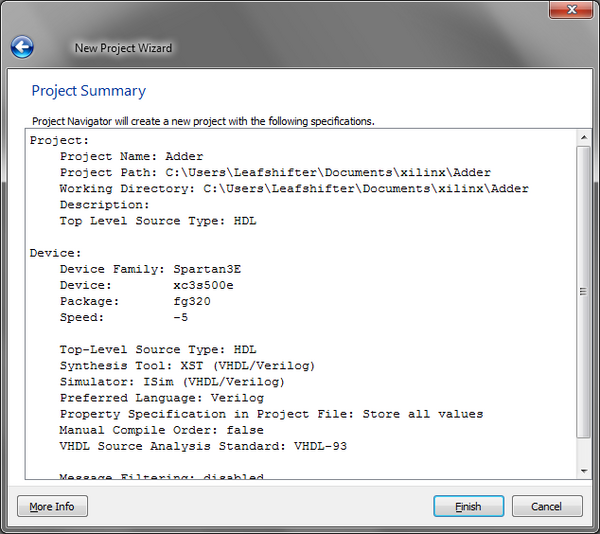

În funcție de placa cu care lucrați, selectați întâi familia de FPGA-uri (Spartan2, Spartan3 sau Spartan3E), apoi alegeți dispozitivul și pachetul conform codurilor pe care le vedeți pe cip. Restul opțiunilor le puteți ignora deocamdată. Ultima fereastă va conține cuprinsul setărilor folosite, unde veți da click pe butonul Finish:

Adăugarea de fișiere noi la proiect

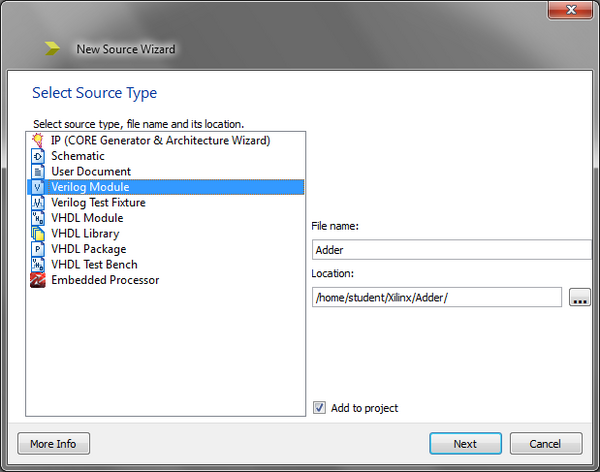

Din meniul Project selectați opțiunea New Source... și va apărea următoarea fereastră:

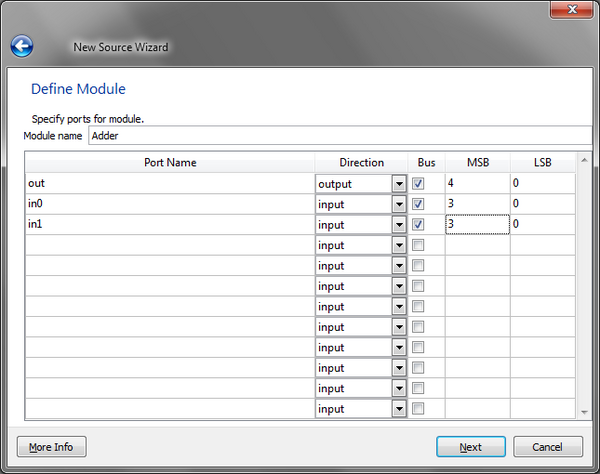

Selectați tipul fișierului ca modul Verilog și dați-i un nume (în cazul de față, Adder). În continuare va apărea fereastra de configurare a modulului:

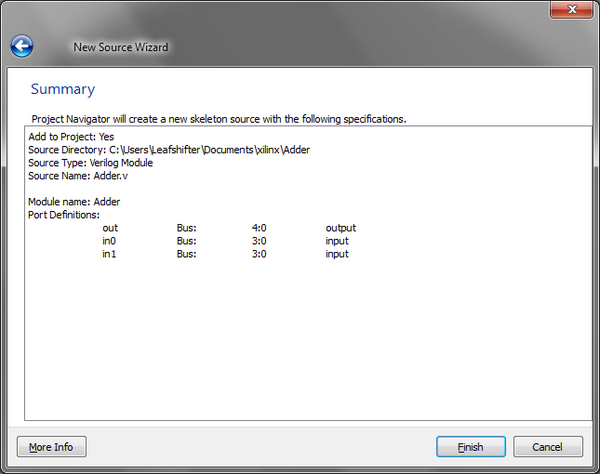

Aici puteți completa detaliile cerute, conform figurii, pentru a genera în mod automat interfața modulului, sau puteți selecta Next și scrie interfața manual, ca și în Modelsim. Celula Bus se bifează dacă portul are mai mult de un bit. Pentru semnale de un singur bit, se lasă ne-bifat. Ultima fereastră vă face un sumar al opțiunilor alese:

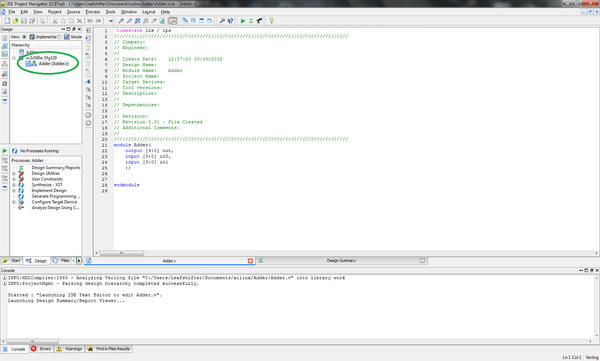

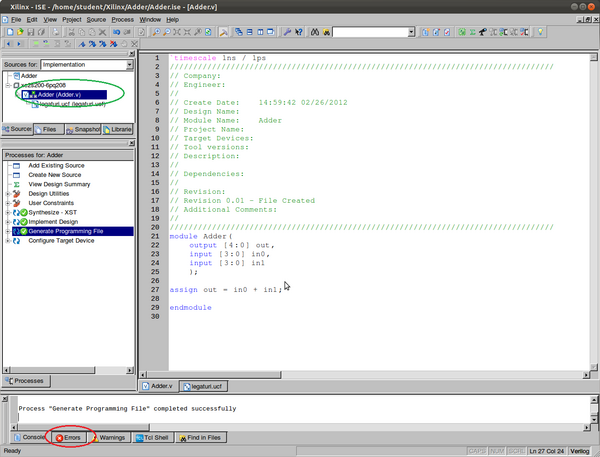

După apăsarea butonului Finish, o sa apară următoarea fereastră, unde se observă că a apărut noul fișier în lista proiectului (vezi cerc verde) și acesta s-a și deschis pentru a putea fi editat. Adăugați blocul assign care implementează funcționalitatea modulului, conform lucrării de laborator 1.

Dacă fișierul Verilog există deja, puteți alege din meniul Project opțiunea Add Copy of Source... care va copia fișierul deja existent în folder-ul proiectului.

Adăugarea fișierului de constrângeri

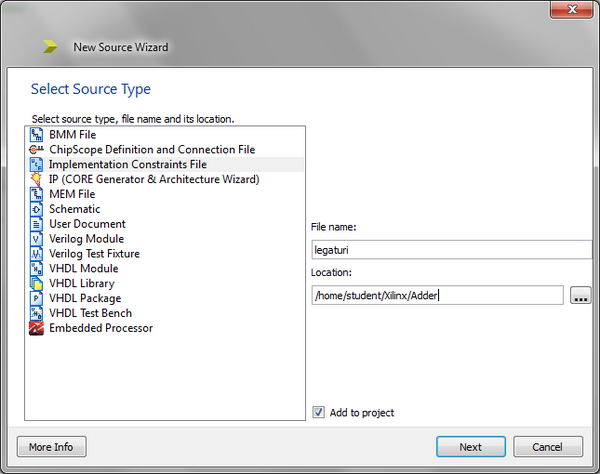

Odată ce există în proiect cel puțin un fișier HDL, se poate adăuga în continuare fișierul de constrângeri, care va fi subordonat fișierului Verilog principal. Adăugarea lui se face tot prin opțiunea New Source... din meniul Project:

După selectarea tipului de fișier (Implementation Constraints File) și numirea acestuia dați click pe Next, apoi pe Finish. În continuare va apărea fișierul de constrângeri sub fișierul Verilog în lista de proiect (vezi cerc verde), și vi se va deschide fișierul pentru editare. Faceți toate legăturle de care este nevoie. În cazul de față, vom lega intrarea in0 la switch-urile SW0 - SW3, intrarea in1 la switch-urile SW4 - SW7 și ieșirea out la ledurile LD0 - LD4:

net "out[0]" loc = "J14";

net "out[1]" loc = "J15";

net "out[2]" loc = "K15";

net "out[3]" loc = "K14";

net "out[4]" loc = "E17";

net "in0[0]" loc = "G18";

net "in0[1]" loc = "H18";

net "in0[2]" loc = "K18";

net "in0[3]" loc = "K17";

net "in1[0]" loc = "L14";

net "in1[1]" loc = "L13";

net "in1[2]" loc = "N17";

net "in1[3]" loc = "R17";

Atenție: Ca și în cazul codului Verilog, dacă portul are un singur bit, atunci va lipsi și paranteza dreaptă cu indexul acestuia, deci:

net "port_de_un_bit" loc = "p46";

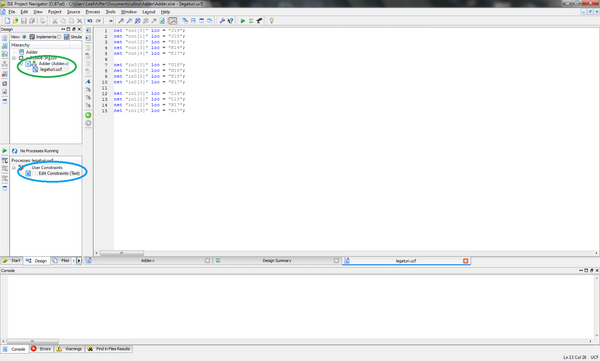

Observație: Pentru a deschide ulterior fișierul de constrângeri pentru editare, acesta trebuie selectat din lista de fișiere ale proiectului (vezi cerc verde), iar după ce îl selectați, în lista de procese va apărea o nouă opțiune User Constraints -> Edit Contraints (Text) (vezi cerc albastru) pe care trebuie să dați dublu-click.

Sinteza și programarea plăcii FPGA

Pentru a începe etapele procesului de programare a plăcii, veți selecta din nou fișierul Verilog în lista de proiect (vezi cerc verde) și selectați din lista de procese opțiunea Generate Programming File. Dacă nu există nici o greșeală, în dreptul fiecărei etape va apărea un cerc verde. Dacă aveți erori, în tabul numit Errors (vezi cerc roșu) puteți afla mai multe detalii ca să vă ajute în procesul de depanare:

Dacă nu există erori, în continuare puteți da click pe opțiunea Configure Target Device din lista de procese.

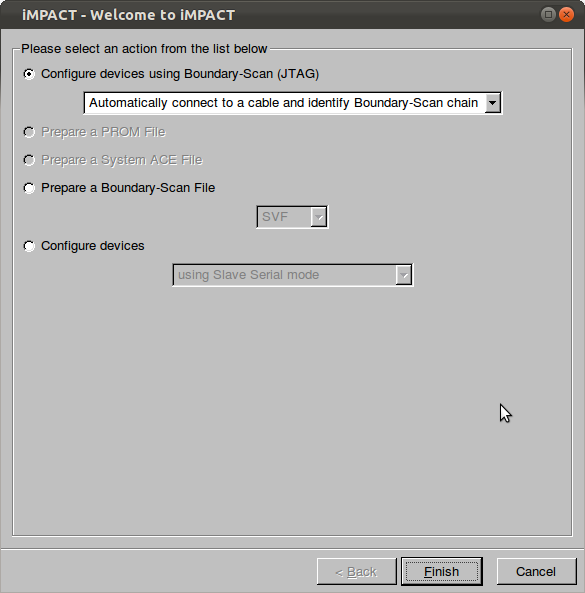

Vi se va deschide o fereastră care vă va anunța că nu există definit un proiect iMPACT, iar după ce dați ok, va porni aplicația iMPACT, care este folosită pentru configurarea plăcii și va apărea următoarea fereastră:

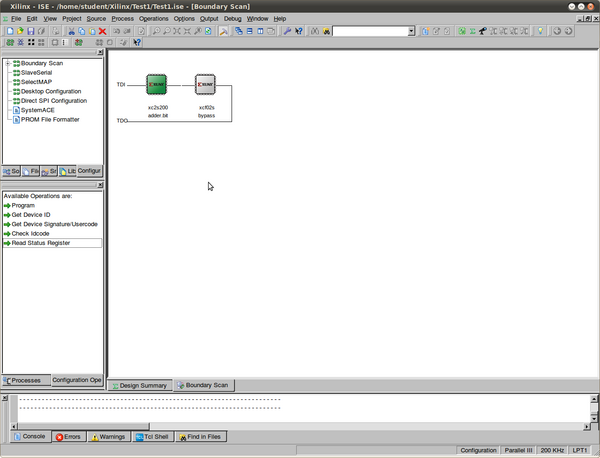

În continuare, dați click pe Finish. Va apărea o fereastră cu două cipuri verzi, fiecare cu un cod de dispozitiv, conform ferestrei de mai jos. Primul are codul FPGA-ului (cel selectat la crearea proiectului și care este scris pe FPGA), iar al doilea are un alt cod. Primul pătrat reprezintă FPGA-ul, iar al doilea o memorie flash pe care nu o vom utiliza și căreia nu-i vom asocia nici un fișier de programare:

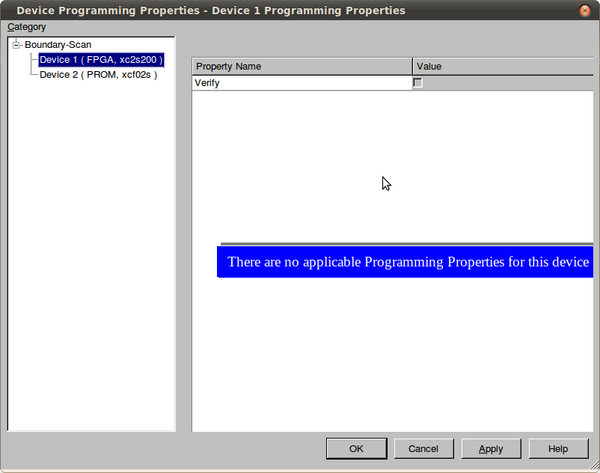

Vi se va cere să selectați un fișier de configurare pentru fiecare din cele două cipuri. Pentru FPGA selectați fișierul .bit obținut la pasul anterior, care poartă numele proiectului (în cazul de față adder.bit) și pentru memoria flash selectați opțiunea Bypass, sau Cancel. Vi se va deschide o fereastră ca cea de mai jos, utilizată pentru modificarea opțiunilor de configurare. Puteți da click pe Ok fără a modifica nimic. Pentru a configura efectiv placa, dați click dreapta pe pătratul reprezentând FPGA-ul și selectați opțiunea Program.