Laboratorul 1

Arhitectura von Neumann

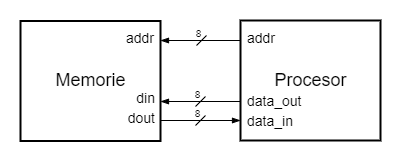

Arhitectura de calculator von Neumann este caracterizată printr-o memorie unică, în care se află atât programul cât și datele, și o magistrală unică, folosită pentru transferul instrucțiunilor de la memorie la procesor, a datelor între procesor și memorie sau între procesor și oricare din dispozitivele de intrare/ieșire conectate la magistrală.

În această lucrare de laborator se va realiza un calculator simplu, având doar procesorul și memoria.

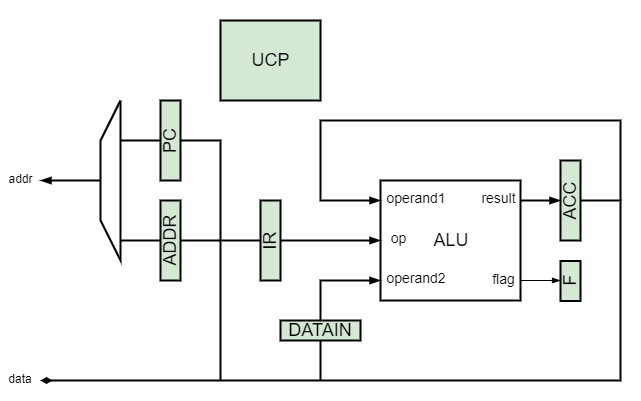

Având o singură cale de acces atât pentru instrucțiuni, cât și pentru date, arhitectura von Neumann procesează o instrucțiune în mai mulți pași, în fiecare pas magistrala comună fiind configurată pentru un anumit transfer între blocurile și registrele conectate la aceasta. Secvențierea procesării instrucțiunilor se face cu ajutorul unității de control al procesorului (UCP), aceasta fiind implementată fie ca o mașină de stări, fie ca o structură microprogramabilă.

Pentru a menține simplitatea la un nivel adecvat unui laborator introductiv, se va considera o arhitectură de procesor cu acumulator, fără set de registre, ale cărui instrucțiuni folosesc cel mult un operand din memorie, prin adresare imediată sau adresare directă.

Schema bloc a procesorului conține o unitate aritmetico-logică (ALU), un contor de program (PC) ce se poate incrementa sau încărca cu o valoare dată, un registru pentru adresarea memoriei (ADDR), registrul instrucțiunii (IR) ce păstrează codul instrucțiunii pe toată durata procesării acesteia, un registru pentru operandul adus din memorie (DATAIN), registrul acumulator (ACC), câțiva biți pentru indicații despre rezultatul ultimei operații efectuate de ALU (F) și unitatea de control a procesorului (UCP). Pentru a nu complica desenul, în schema bloc au fost schițate doar traseele principale (magistrala de date, calea de adresare):

PC

Contorul de program este folosit pentru citirea instrucțiunilor din memorie. Acesta poate fi incrementat sau încărcat cu valoarea de pe magistrala de date, dar numai la comanda UCP.

always @(poosedge clk) begin

if(rst)

pc <= 0;

else begin

if(pc_load)

// PC ia valoarea de pe magistrala comună de date

else if (pc_incr)

pc <= pc + 1;

else

pc <= pc;

end

end

ADDR

Registrul de adresare a memoriei pentru citirea datelor este un registru elementar ce poate fi doar încărcat:

always @(poosedge clk) begin

if(rst)

raddr <= 0;

else begin

if(raddr_load)

// ADDR ia valoarea de pe magistrala comună de date

else

raddr <= raddr;

end

end

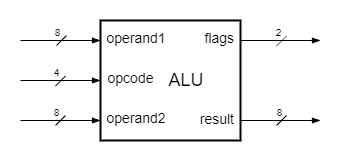

ALU

Unitatea aritmetico-logică, ALU, este responsabilă de execuţia instrucţiunilor. În primul rând, după cum ne şi sugerează numele, instrucţiunile aritmetice şi cele logice, dar şi celelalte categorii de instrucţiuni, în execuţia cărora intervin operaţii precum calculul unor adrese pentru instrucţiunile de acces la memorie sau pentru instrucţiunile de salt relativ. Concret, ALU primeşte operanzii unei instrucţiuni şi oferă rezultatul operaţiei specificate în codul instrucţiunii. De exemplu instrucţiunea de adunare determină în ALU adunarea celor doi operanzi de la intrare, suma acestora (rezultatul) apărând la ieşirea ALU. Un alt exemplu, instrucţiunea de salt relativ determină în ALU adunarea a două numere, valoarea contorului de program (PC) şi valoarea saltului relativ specificată în corpul instrucţiunii, rezultatul fiind noua valoare de contor de program, ce va fi încărcată în contorul de program.

Complexitatea ALU este determinată în primul rând de complexitatea operaţiilor aritmetice ale instrucţiunilor din setul de instrucţiuni, însă depinde, uneori semnificativ, şi de performanţele avute în vedere (viteză, paralelism, consum redus) ce pot modifica radical structura aleasă. La nivel funcţional, fără a fi preocupaţi de implementarea efectivă, ALU poate fi privit ca un bloc multifuncţional a cărui funcţie este selectată de codul operaţiei instrucţiunii:

always @(*) begin

case(opcode)

`ADD: rezultat = operand1 + operand2;

`SUB: rezultat = operand1 - operand2;

// urmeaza implementarea altor operatii

endcase

end

Descrieți funcțional (comportamental) un ALU de 8 biți ce execută operațiile din tabelul 1.

| opcode | operație | detalii |

|---|---|---|

ADD |

adunare | |

SUB |

scădere | operandul 2 se scade din operandul 1 |

AND |

ȘI logic | fiecare bit al rezultatului este ȘI logic între biții corespunzători ai operanzilor |

CMP |

comparație | Z și N se modifică conform tabelului 2 |

Rezultatul operației de comparație este semnalizat prin biții indicatori ai rezultatului:

| Z | N | |

|---|---|---|

| operand1 > operand2 | 0 | 0 |

| operand1 = operand2 | 1 | 0 |

| operand1 < operand2 | 0 | 1 |

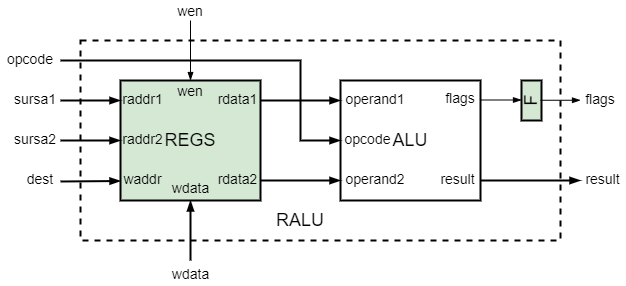

RALU

Unitatea aritmetico-logică împreună cu setul de registre formează RALU (Register and ALU). În funcție de arhitectură, registrele din setul de registre pot fi speciale sau de uz general. Procesorul implementat în acest laborator are un set de 8 registre de uz general. Fiecare registru poate fi sursa oricărui operand și poate fi destinație. Setul de registre poate avea porturi distincte pentru scriere și pentru citire, precum și porturi separate pentru fiecare operand citit. Implementarea aleasă pentru acest laborator are un set de registre cu trei porturi, un port pentru citirea primului operand (raddr1, rdata1), altul pentru citirea celui de al doilea operand (raddr2, rdata2) și un port pentru scriere (waddr, wdata). Portul de scriere folosește un semnal de control, wen, ce activează scrierea numai pentru anumite instrucțiuni.

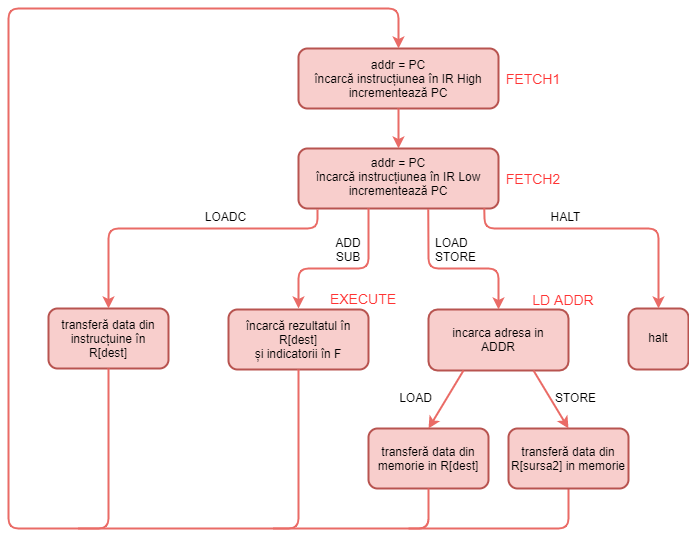

UCP

Unitatea de control a procesorului controlează actualizarea fiecărui registru din procesor, accesul la magistrala comună de date și multiplexarea adreselor spre memorie. Ea se implementează ca un FSM cu câteva stări și tranziții ce depind de tipul instrucțiunii. Pentru o instrucțiune aritmetico-logică secvența de procesare are 4 pași, necesitând 4 cicuri de ceas: