CID Seminar 3

În acest seminar veţi învăţa ce este un ciruit secevențial și cum se descrie acesta în Verilog.

Cuvinte cheie: clock, flip-flop, circuit sincron/ asincron, atribuire blocking/ non-blocking

Sintaxă Verilog: always, initial, forever

Circuitele digitale pot fi de două tipuri:

- circuite logice combinaționale (CLC) - sunt circuite asincrone - pot fi descrise fie folosind instrucțiuni de tip assign, fie folosind procese de tip always

- circuite secvențiale - sunt circuite sincrone cu ceasul - pot fi descrise folosind doar procese de tip always

Exemplul 1

Descrieți în Verilog un semnal de ceas cu perioada 6 unități de timp.

Explicaţie suplimentară

Pe ieșirile unui CLC poate să apară hazard. Pentru a elimina hazardul, ieșirile unui CLC pot fi sincronizate cu un semnal suplimentar, numit semnal de ceas (clock). Semnalul de ceas are următoarele proprietăți:

- Este semnal dreptunghiular (la fel ca toate celelalte semnale digitale)

- Este un semnal periodic

- Este singurul semnal dintr-un sistem digital care este activ pe front. Toate celelalte semnale prezente într-un sistem digital sunt active pe palier.

Exemplul 2

Să se descrie în Verilog un bistabil D cu următoarele caracteristici:

- semnal de ceas activ pe frontul pozitiv

- intrare de reset sincronă cu ceasul şi semnal de reset activ pe palierul de 0

Exemplul 3

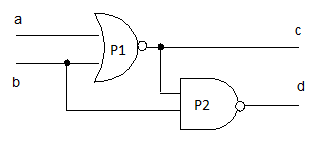

Descrieți în Verilog circuitul din figura 1, folosind o instrucțiune assign, respectiv un proces always.

Explicaţie suplimentară

Când utilizați assign - semnalul trebuie declarat de tip wire.

Când utilizați always sau initial - semnalul trebuie declarat de tip reg.

Exemplul 5

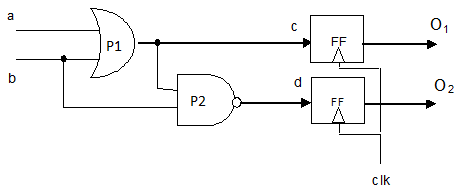

Să se descrie în Verilog circuitul din figura 3 în două moduri:

- separând partea combinațională de cea secvențială (folosind 2 procese always)

- folosind un singur proces always

Exemplul 6

Descrieți în Verilog un numărător cu intrare de reset sincronă cu ceasul, reset activ pe palierul de 0 şi enable sincron cu ceasul și activ pe 1.

Exemplul 7

Scrieți 3 testbench-uri, pentru a putea simula funcționarea pentru: un bistabil / circuitul din exemplul 5/ circuitul din exemplul 6.

Exemplul 8

Simulați și comparați următoarele circuite (refolosiți un testbench din exemplul 7):

Circuitul 1:

always@(posedge clk) begin

if (nReset == 0) begin

b <= 0;

c <= 0;

end else begin

b <= a;

c <= b;

end

end

Circuitul 2:

always@(posedge clk) begin

if (nReset == 0) begin

b = 0;

c = 0;

end else begin

b = a;

c = b;

end

end

Observație: Pentru descrierea circuitelor sincrone cu ceasul se folosește întotdeauna atribuirea non-blocking <=.

Exemplul 9

Comparați funcționarea unui bistabil descris folosind un proces always care are lista de sensitivități de forma: (posedge clock, nReset) cu cea a unui bistabil descris folosind un proces always care are lista de sensitivități de forma: (posedge clock, negedge nReset). Ce diferențe observați în simularea celor doi bistabili?

Temă

- Descrieți în Verilog și simulați un circuit de numărare folosind un bistabil cu intrare de Set asincronă cu ceasul şi activă pe palierul de 1 și intrare de Load sincronă cu ceasul, activă pe palierul de 1. Când Load este activ, numărătorul se încarcă cu o valoare Data_In.

- Descrieți și simulați funcționarea unui registru de deplasare la stânga, folosind operatorul de shiftare <<, respectiv cel de concatenare {}.

- Descrieți și simulați un registru de deplasare la stânga circular (MSB devine LSB).