DIC Seminar 1

In this seminar you will learn to describe some simple digital circuits in Verilog language and use the Quartus II and ModelSim programs.

'Keywords:' logical gates, ports, waveform, project, mode, instantiation, testbench

Verilog syntax: 'module' ',' 'wire' ',' 'reg' ',' 'initial' ',' 'stop' '

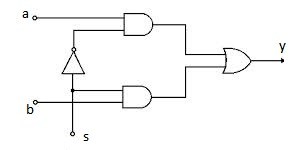

Verilog is a hardware description language. In this language we can describe digital circuits as in Figure 1.

Notions and Knowledge Required

- Boolean Logic and Numerical Systems

- Syntax notions Verilog

Exercise 1

Figure 1 is a schematic diagram of a digital circuit containing logical gates. Describe this schema in Verilog.

'Explanations' : The elementary logic gates are predefined in Verilog: 'not' , 'and' , 'nand' 'nor' , 'xor' , 'nxor' . The correct syntax is, for instantiating a 'and' gate:

<syntaxhighlight lang = "verilog"> and node_name (output, input_1, input_2, ...) entry_n); </ Syntaxhighlight>

Exercise 2

Create a Verilog file describing the circuit from exercise 1.

Explanations: The description of a circuit includes:

- interface (input and output ports declaration)

- description of the function or circuit diagram

In Verilog, circuit descriptions are made up of modules. The syntax is the following:

<syntaxhighlight lang = "verilog"> module_meu (port_port) module; / * ports are external circuit connections * /

// first report ports // Then give the functional or structural details endmodule </ Syntaxhighlight>

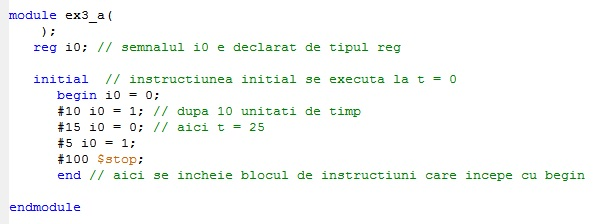

Exercise 3

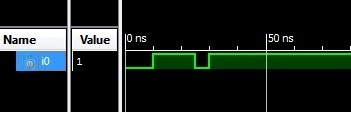

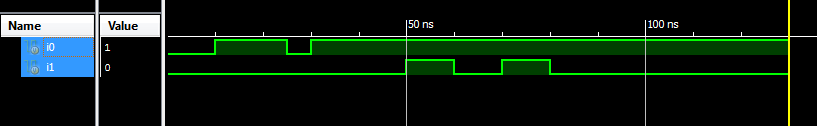

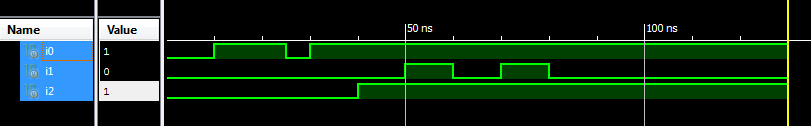

Generate the waveforms in the following figures in the simulator.

1. Signal i0:

2. Two signals, i0 and i1:

Three signals:

Resolve Item 1: </ u>

It will write a new source file that has no external ports (because it does not describe a circuit).

Example 4

Simulate the operation of the module from exercise 2 by applying the signals from exercise 3 - point 3. Knowing that this circuit is a multiplexer (circuit selection), analyze the waveforms to see if they are correct. Modify the waveform at input s and check the correct operation.

'Explanation:' To simulate the operation of a circuit, we need to build a testbench described in a new module. We apply the respective signals to the input of the tested circuit - we instantiate that circuit. We simulate the test module and then analyze the waveforms to see if they correspond to the implemented function.

Exercise 5

Draw the schema described by the following Verilog code:

<syntaxhighlight lang = "verilog"> circuit1 ana (.in1 (a), .in2 (b), .out1 (w), .out2 (en)); circuit2 doru (.in3 (w), .in4 (b), .out (c)); circuit3 zuzu (.in0 (en), .in1 (c), .out (out)); </ Syntaxhighlight>

... where modules have ports declared as follows:

<syntaxhighlight lang = "verilog"> module circuit1 (

input in1, in2,

output out1,

output out2);

... endmodule

module circuit2 (

input in3, in4,

output out);

... endmodule

module circuit3 (

input in1,

input in0,

output out);

... endmodule </ Syntaxhighlight>

The main concepts of Verilog introduced in this seminar

1. 'Circuit descriptions in Verilog are made up of' 'modules. Any module starts with the module word and ends with endmodules. Modules can not overlap and can not be included in each other.

<syntaxhighlight lang = "verilog"> module_meu (port_port) module; / * ports are external circuit connections * /

...... // first report ports ...... then give the functional or structural details endmodule </ Syntaxhighlight>

2. The ports of a circuit can be declared

- in the module body

- Compact in the port list.

Entries to Verilog are declared with the word input , outputs are output .

Version 1 (Verilog '95) </ u> <syntaxhighlight lang = "verilog"> module circuit (a, b, c, out);

input a, b, c; // we can put more on the same line, separated by, output out;

..... endmodule </ Syntaxhighlight>

Option 2 (Verilog 2001) </ u> <syntaxhighlight lang = "verilog"> module circuit ( input a, // write with tabs to be visible input b, input c, output out); ... endmodule </ Syntaxhighlight>

If we have several similar entries we can also write: <syntaxhighlight lang = "verilog"> module circuit ( input a, b, c, output out); ... endmodule </ Syntaxhighlight>

3. 'The code lines in Verilog end with'; (there is also excellent

A