Laboratorul 1

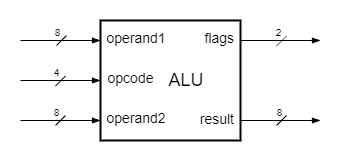

ALU

Unitatea aritmetico-logică, ALU, este responsabilă de execuţia instrucţiunilor. În primul rând, după cum ne şi sugerează numele, instrucţiunile aritmetice şi cele logice, dar şi celelalte categorii de instrucţiuni, în execuţia cărora intervin operaţii precum calculul unor adrese pentru instrucţiunile de acces la memorie sau pentru instrucţiunile de salt relativ. Concret, ALU primeşte operanzii unei instrucţiuni şi oferă rezultatul operaţiei specificate în codul instrucţiunii. De exemplu instrucţiunea de adunare determină în ALU adunarea celor doi operanzi de la intrare, suma acestora (rezultatul) apărând la ieşirea ALU. Un alt exemplu, instrucţiunea de salt relativ determină în ALU adunarea a două numere, valoarea contorului de program (PC) şi valoarea saltului relativ specificată în corpul instrucţiunii, rezultatul fiind noua valoare de contor de program, ce va fi încărcată în contorul de program.

Complexitatea ALU este determinată în primul rând de complexitatea operaţiilor aritmetice ale instrucţiunilor din setul de instrucţiuni, însă depinde, uneori semnificativ, şi de performanţele avute în vedere (viteză, paralelism, consum redus) ce pot modifica radical structura aleasă. La nivel funcţional, fără a fi preocupaţi de implementarea efectivă, ALU poate fi privit ca un bloc multifuncţional a cărui funcţie este selectată de codul operaţiei instrucţiunii:

always @(*) begin

case(opcode)

4'b0001: rezultat = operand1 + operand2;

4'b0010: rezultat = operand1 - operand2;

// urmeaza implementarea altor operatii

endcase

end

Descrieți funcțional (comportamental) un ALU de 8 biți ce execută operațiile din tabelul 1.

| opcode | operație | detalii |

|---|---|---|

ADD |

adunare | |

SUB |

scădere | operandul 2 se scade din operandul 1 |

AND |

ȘI logic | fiecare bit al rezultatului este ȘI logic între biții corespunzători ai operanzilor |

OR |

SAU logic | fiecare bit al rezultatului este SAU logic între biții corespunzători ai operanzilor |

XOR |

XOR logic | fiecare bit al rezultatului este SAU-EXCLUSIV logic între biții corespunzători ai operanzilor |

CMP |

comparație | Z și N se modifică conform tabelului 2 |

LOAD |

transfer | operandul1 este transferat la ieșirea ALU |

STORE |

transfer | operandul1 este transferat la ieșirea ALU |

Tabelul 1 nu conține toate instrucțiunile setului de instrucțiuni, ci numai instrucțiunile care folosesc ALU. Pentru instrucțiunile ce nu folosesc ALU implementarea execuției lor în ALU poate fi ignorată, dar rezultatul de la ieșirea ALU nu trebuie scris în vreun registru.

Rezultatul operației de comparație este semnalizat prin biții indicatori ai rezultatului:

| Z | N | |

|---|---|---|

| operand1 > operand2 | 0 | 0 |

| operand1 = operand2 | 1 | 0 |

| operand1 < operand2 | 0 | 1 |

Biții indicatori sunt calculați pentru fiecare operație și reflectă starea rezultatului. Procesorul implementat în laborator are doi indicatori, Z și N. Dacă rezultatul este zero se activează bitul Z (zero). Dacă rezultatul este negativ se activează ieșirea N (negativ). Operația de comparație poate fi implementată ca o operație de scădere fără destinație (se salvează în procesor doar biții indicatori nu și rezultatul):

assign Z = (result == 0);

assign N = result[7]; // în complement față de 2 bitul MSB este bit de semn

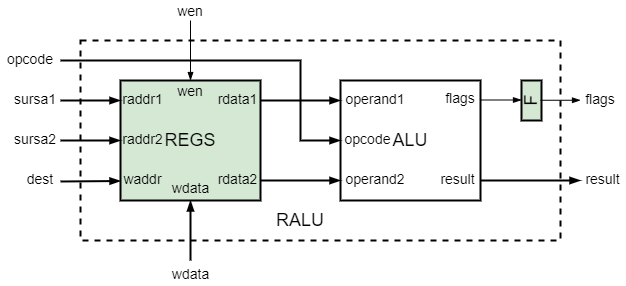

RALU

Unitatea aritmetico-logică împreună cu setul de registre formează RALU (Register and ALU). În funcție de arhitectură, registrele din setul de registre pot fi speciale sau de uz general. Procesorul implementat în acest laborator are un set de 16 registre de uz general. Fiecare registru poate fi sursa oricărui operand și poate fi destinație. Setul de registre poate avea porturi distincte pentru scriere și pentru citire, precum și porturi separate pentru fiecare operand citit. Implementarea aleasă pentru acest laborator are un set de registre cu trei porturi, un port pentru citirea primului operand (raddr1, [rdata1), altul pentru citirea celui de al doilea operand (raddr2, rdata2) și un port pentru scriere (waddr, wdata). Portul de scriere folosește un semnal de control, wen, ce activează scrierea numai pentru anumite instrucțiuni.

Setul de registre având 16 registre, pentru accesul la un registru este nevoie de o adresă de 4 biți. Semnalele de adresă raddr1, raddr2 și waddr sunt fiecare de 4 biți. Datele sunt pe 8 biți, prin urmare registrele și ieșirile de date rdata1, rdata2 și wdata sunt fiecare de câte 8 biți.

validare RALU

Scrieti un module de testare ce instantiază setul de registre și ALU, generează ceasul și semnalul de reset și o secvență de instrucțiuni.

generarea ceasului

initial begin

clk = 0; // initialization at time 0

forever #10 clk = ~clk; // toggle the clock at each 10 simulation steps

end

generarea semnalului de reset

initial begin

rst = 0;

#13 rst = 1; // reset activ în 1 logic

#13 rst = 0;

end

Întîrzierile sunt alese astfel încât fronturile semnalului de reset să nu coincidă cu fronturile ceasului.

generarea secvenței de instrucțiuni

La fiecare ceas se setează valorile intrărilor opcode, sursa1, sursa2, dest și wen cu valori care să corespundă instrucțiunii dorite.

Pentru a ne asigura că toate semnalele se modifică numai după frontul activ al ceasului, vom aștepta de fiecare dată acest front folosind instrucțiunea @(posedge clk);

Semnalul wen se setează la 1 sau la 0 după cum dorim ca rezultatul să se salveze sau nu în registrul destinație.

Semnalul wen nu face parte din instrucțiune. În laboratorul 2 el va fi generat de unitatea de control a procesorului (UCP) în funcție de codul instrucțiunii. De exemplu instrucțiunea CMP nu modifică niciun registru ci doar biții indicatori, prin urmare wen va fi în permanență 0 pe durata procesării acestei instrucțiuni.

initial begin

opcode = 4'b0000; dest = 4'd0; sursa1 = 4'd0; sursa2 = 4'd0; wen = 1'b0;

#26 // se așteaptă finalizarea resetului

@(posedge clk);

opcode = 4'b0001; dest = 4'd7; sursa1 = 4'd6; sursa2 = 4'd5; wen = 1'b1; // ADD R7 R6 R5 // R7 <- R6 + R5

@(posedge clk);

opcode = 4'b0010; dest = 4'd7; sursa1 = 4'd7; sursa2 = 4'd4; wen = 1'b1; // SUB R7 R7 R4 // R7 <- R7 - R4

// alte instrucțiuni

end