CID Lab Lucrarea 2

Noțiuni și cunoștințe necesare

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Logică booleană și sisteme de numerație

- Noțiuni de sintaxă Verilog

- Afișajul cu 7 segmente

Exemplul 1

Realizați un decodor de doi biți folosind un bloc case. Testați decodorul legând intrările la switch-uri și ieșirile la led-uri.

Exemplul 2

Realizați un transcodor pentru afișajul cu 7 segmente, folosind un bloc case, care să poată afișa valorile de la 0 la 3. Intrarea modulului se va numi value iar ieșirea out_seg.

Exercițiu

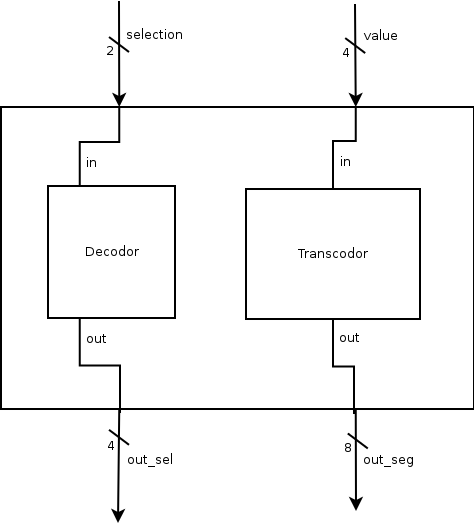

Completați transcodorul de la exemplul 2 astfel încât să poată afișa valorile de la 0 la 15, în baza 16 (10 = A, 11 = b, 12 = C, 13 = d, 14 = E, 15 = F). Adăugați circuitului un decodor folosit pentru a selecta care din cele 4 cifre să afișeze valoarea selctată. Intrarea pentru selecția cifrei se va numi selection, iar ieșirea out_sel.

Intrarea value se va conecta la switchurile SW3-SW0 (corespunzător biților 3->0 ai value, în această ordine), intrarea selection la SW7-SW6 (corespunzător biților 1->0 ai selection, în această ordine), iar ieșirile la pinii corespunzători pentru afișajul cu 7 segmente.

Modulul top-level se va numi afisaj7seg.

Submiterea Exercițiilor

Pentru notare, se vor submite următoarele fișiere, către adresa de e-mail indicată de cadrul didactic și către adresa cid_lab_homework@dcae.pub.ro

O arhivă zip ce va conține:

- Toate fișierele Verilog (cu extensia .v) care conțin descrierea circuitului de afișare pe 7 segmente

- Un fișier de constrângeri, cu extensia .ucf

- Un fișier de tip proiect Xilinx ISE, cu extensia .xise

Atenție, arhiva va conține doar fișiere (fără directoare).

Subiectul mesajului de e-mail trebuie să respecte formatul [Nume]_[Prenume]_[Grupa]_7seg.

Recomandări pentru cadrele didactice

- Se vor introduce noțiunile necesare folosirii afișajului cu 7 segmente