FPGA - Introducere (2023)

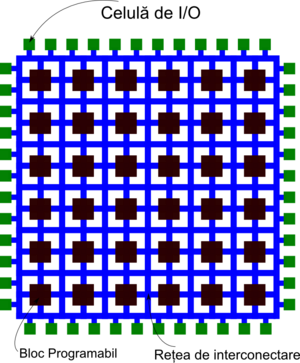

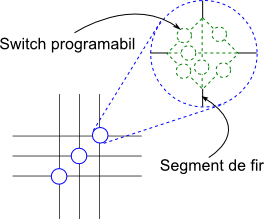

FPGA-ul (Field-programmable gate array) este un circuit programabil, capabil sa implementeze un anumit circuit definit de utilizator si este format dintr-o matrice de blocuri programabile, interconectate intre ele printr-o serie de conexiuni programabile. Aceste blocuri pot implementa atat functii logice, cat si memorii.

Cand se doreste implementarea unui circuit pe FPGA, acesta urmeaza mai multe etape: elaborarea, sinteza, implementarea, generarea fisierului de implementare si programarea.

Elaborarea este procesul prin care codul Verilog este transformat intr-un circuit la nivel de porti si registre (netlist) si este independent de modelul de FPGA folosit.

Sinteza este procesul în care se realizează transformarea circuitului descris într-un netlist dependent de tehnologie. Se vor folosi la acest pas primitivele disponibile pe FPGA.

Implementarea este procesul în care se preia netlist-ul ce conține primitivele FPGA și modul lor de interconectare realizat la pasul de sinteză și se realizează maparea lor efectivă în FPGA (place and route).

Registrul de Tip D sau bistabilul, este un circuit de memorie ce poate memora date la momentul aparitiei unui eveniment front crescator de ceas (vom discuta despre acesta in detaliu mai tarziu). MUX este un multiplexor si este capabil sa selecteze pentru iesire datele de la bistabil, sau datele de la LUT (Look-Up Table). Acest LUT este o memorie ROM capabila sa stocheze date ce vor fi accesate cu ajutorul intrarilor (intrarile au rol de adresa). LUT-ul este secretul din spatele implementarii functiilor logice. Circuitele implementate pe FPGA nu sunt efectiv porti interconectate intre ele, ci memorii ROM (LUT) care stiu sa memoreze iesirile asociate unor combinatii de intrare.

Asadar, in timpul sintezei, functiile logice sunt transformate in tabele de adevar (pentru fiecare combinatie de intrare se calculeaza iesirea iesirea), care sunt implementate prin LUT-uri.

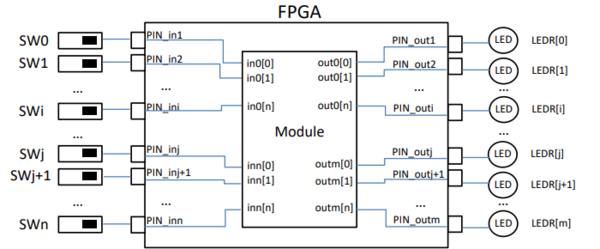

Circuitul dezvoltat de utilizator trebuie legat apoi la pini fizici ai FPGA-ului, pentru a putea stimula intrarile si a observa starile iesirilor. Aceasta legare la pinii fizici este posibila, deoarece, asa cum am mentionat si mai sus, conexiunile in interiorul FPGA-ului sunt programabile. Pe placa, avem comutatoare si butoane pentru a controla starea intrarilor si LED-uri si afisaje pentru a observa starea iesirilor.

In figura de mai jos este prezentata o schema simplificata a conectarii modulului implementat pe FPGA la pinii fizici. Fiecare pin fizic este codat in tool-ul de sinteza cu un anumit cod. Mentionand in fisierul de constrangeri in dreptul fiecarui bit al fiecarei intrari si iesiri codul aferent pinului fizic, tool-ul va programa conexiunile programabile astfel incat portul modulului sa fie conectat la pinul fizic ales. Mai departe, pe placa de dezvoltare ce contine si FPGA-ul, pinii fizici sunt conectati prin trasee metalice la dispozitivele de control si observatie.

Folosind toate aceste informatii (implementarea circuitului si modul de conectare la porturile fizice ale FPGA-ului) se va genera fisierul de implementare, ce va fi apoi descarcat in memoria SRAM a FPGA-ului, configurand astfel dispozitivul.

Observatii:

- Conexiunile dintre comutatorare si pinii FPGA sunt fixe. La fel si cele intre pinii FPGA si LED-uri.

- Conexiunile dintre porturile modulului Module si pinii FPGA sunt configurabile.

- Legarea porturilor modulului Module la pinii fizici ai FPGA se realizeaza prin configurarea conexiunilor din FPGA conform contrangerilor de I/O pe care le vom mentiona in proiect, inainte de sinteza.