Applications 3: Diferență între versiuni

Fără descriere a modificării |

Fără descriere a modificării |

||

| Linia 63: | Linia 63: | ||

''block of instructions''<br /> | ''block of instructions''<br /> | ||

'''end''' | '''end''' | ||

For combinational circuits the safest way to declare the sensitivity list is to use the wildcard ('''*'''). | |||

It stands for all variables that appear on RHS expressions and in evaluation expressions. | |||

<syntaxhighlight lang="Verilog"> | |||

always @(*) begin | |||

if(s) | |||

c = in[1]; | |||

else | |||

c = in[0]; | |||

end | |||

</syntaxhighlight> | |||

== Exercise 3 == | == Exercise 3 == | ||

Versiunea de la data 4 martie 2019 21:12

Behavioral descriptions, continuous assignment, conditional instructions, use of blocks always for describing combinational circuits.

Structural descriptions, logic gates, verilog gate primitives.

Exercise 1

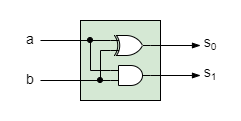

gate-level description of the 1-bit half adder

Use data flow description (a simpler kind of behavioral description that uses logic expressions). Logic expressions employ only logic operators.

| operator | function |

|---|---|

| ~ | not |

| & | and |

| | | or |

| ^ | xor |

One assign instruction for each output. Concurrent assignments.

assign c[0] = a ^ b;

assign c[1] = a & b;

Use gate-level description (a structural description with gate primitives). Verilog gate primitives: not, and, nand, or, nor, xor and xnor. Except for the not gate, all other primitive gates may have 2, 3 or more inputs.

They are all instantiated using the same template: gate primitive myGate(outputWire, inputWire1, inputWire2 ...) as in the following examples:

not g1(dout, din); is a not gate with dout at output and din connected at its input.

nand g2(dout, d1, d2); is a nand gate with dout at output and two wires, d1 and d2, connected to its inputs.

nand g3(dout, d1, d2, d3, d4); is a nand gate with dout at output and for inputs, connected to d1, d2, d3 and d4.

Using gate primitives, a possible structural description of the half-adder may be:

xor g1(c[0], a, b);

and g2(c[1], a, b);

Write a simple testbench for the half-adder and simulate both descriptions, data-flow and gate-level with primitives.

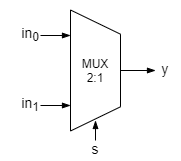

Exercise 2

2 to 1 multiplexer, behavioral description

always block. Used for behavioral descriptions. Template:

always @(sensitivity list) begin

block of instructions

end

For combinational circuits the safest way to declare the sensitivity list is to use the wildcard (*). It stands for all variables that appear on RHS expressions and in evaluation expressions.

always @(*) begin

if(s)

c = in[1];

else

c = in[0];

end

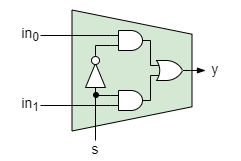

Exercise 3

The same 2 to 1 multiplexer, described at the gate level

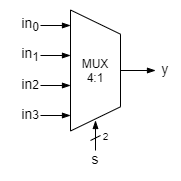

Exercise 4

4 to 1 multiplexer

case instruction. Selects between multiple cases. Template

case(selectVariable)

value1 : instruction block 1

value2 : instruction block 2

a.s.o.

endcase

value1, value2 a.s.o. are integer values of the selectVariable

case(s)

0: c = in[0];

1: c = in[1];

2: c = in[2];

3: c = in[3];

endcase