CID Lab Lucrarea 4: Diferență între versiuni

De la WikiLabs

Jump to navigationJump to search

| Linia 13: | Linia 13: | ||

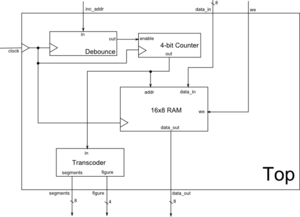

[[Fișier:lab4.png|thumb|Schema bloc a circuitului]] | [[Fișier:lab4.png|thumb|Schema bloc a circuitului]] | ||

* Descrieți în Verilog o memorie RAM 16x8 cu un port de citire-scriere. Scrieți un modul de test pentru acest circuit. Simulați memoria RAM în Modelsim. | * Descrieți în Verilog o memorie RAM 16x8 cu un port de citire-scriere sincron. Scrieți un modul de test pentru acest circuit scriind anumite adrese cu anumite valori si apoi citindu-le. Simulați memoria RAM în Modelsim. | ||

* Modificați modulul de control pentru afișajul cu 7 segmente din lucrarea 3 de laborator, astfel încât acesta să afișeze simbolurile hexazecimale (A,b,C,d,E,F) pentru valorile 10 - 15. | * Modificați modulul de control pentru afișajul cu 7 segmente din lucrarea 3 de laborator, astfel încât acesta să afișeze simbolurile hexazecimale (A,b,C,d,E,F) pentru valorile 10 - 15. | ||

* Descrieți in Verilog un modul de debounce. Scrieți un modul de test pentru acest circuit. Simulați memoria RAM în Modelsim. | * Descrieți in Verilog un modul de debounce. Scrieți un modul de test pentru acest circuit. Simulați memoria RAM în Modelsim. | ||

Versiunea de la data 25 martie 2012 11:54

Noțiuni și cunoștințe necesare

- Logică booleană și sisteme de numerație

- Sintaxă Verilog

- Utilizarea programului de simulare ModelSim

- Introducere în sinteza pe FPGA. Xilinx ISE

- Utilizarea programului de sinteză Xilinx ISE

- Memorii ROM, Dispozitiv de IO: Afișajul cu 7 segmente, Circuite secvențiale, Numărătorul

- Memorii RAM, Circuitul de debounce

Cerințe

- Descrieți în Verilog o memorie RAM 16x8 cu un port de citire-scriere sincron. Scrieți un modul de test pentru acest circuit scriind anumite adrese cu anumite valori si apoi citindu-le. Simulați memoria RAM în Modelsim.

- Modificați modulul de control pentru afișajul cu 7 segmente din lucrarea 3 de laborator, astfel încât acesta să afișeze simbolurile hexazecimale (A,b,C,d,E,F) pentru valorile 10 - 15.

- Descrieți in Verilog un modul de debounce. Scrieți un modul de test pentru acest circuit. Simulați memoria RAM în Modelsim.

- Modificați numărătorul de la lucrarea 3 astfel încât să fie pe 4 biți, eliminați portul de reset și adăugați un port enable care să permită incrementarea doar când acesta este 1.

- Folosind modulele anterioare și blocuri de instanțiere, descrieți în Verilog un circuit (numit Top) în care să utilizați un numărător care să dea adresa memoriei, iar numărarea să se facă doar la apăsarea unui buton (folosiți pentru buton un modul de debounce). Legați ieșirea numărătorului la intrarea de adresă a memoriei și la intrarea modulului de control al afișajului (transcodor), portul de date de intrare la switch-uri, portul de date de ieșire la leduri, portul de write-enable (we) la unul din butoane. Sintetizați circuitul în Xilinx ISE și configurați placa de FPGA.