Circuite secvențiale: Diferență între versiuni

De la WikiLabs

Jump to navigationJump to search

| Linia 16: | Linia 16: | ||

<div class="regula"><font color="red">'''Regulă:'''</font> Încărcarea unei valori într-un registru se face doar pe frontul de ceas.</div> | <div class="regula"><font color="red">'''Regulă:'''</font> Încărcarea unei valori într-un registru se face doar pe frontul de ceas.</div> | ||

<div class="regula"><font color="red">'''Regulă:'''</font> În [[Verilog#Blocuri always secvențiale|Verilog]], încărcarea cu o valoare a unui registru se face exclusiv în blocuri '''always'''.</div> | <div class="regula"><font color="red">'''Regulă:'''</font> În [[Verilog#Blocuri always secvențiale. Asignări non-blocante (non-blocking assignments)|Verilog]], încărcarea cu o valoare a unui registru se face exclusiv în blocuri '''always'''.</div> | ||

Versiunea de la data 10 martie 2012 19:31

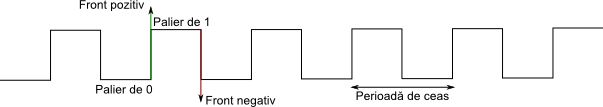

Circuitele secvențiale sunt circuitele care sunt sincronizate de un semnal de ceas, adică ale căror ieșiri nu se modifică decât pe frontul pozitiv (sau negativ, în funcție de descriere) de ceas.

Semnalul de ceas

Semnalul de ceas este un semnal periodic, care oscilează cu o anumită frecvență, numită frecvența de ceas.

Observație: Vezi sintaxa Verilog pentru a afla cum se generează un semnal de ceas în simulare.

Circuite de memorare. Registrul

Registrul este celula elementară de memorare și baza circuitelor secvențiale. Odată o valoare încarcată într-un registru, aceasta se păstrează până la suprascrierea ei cu o altă valoare.

Regulă: Încărcarea unei valori într-un registru se face doar pe frontul de ceas.

Regulă: În Verilog, încărcarea cu o valoare a unui registru se face exclusiv în blocuri always.