Circuite secvențiale

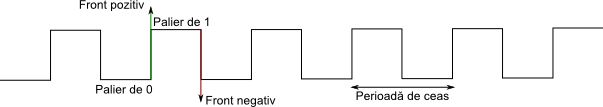

Circuitele secvențiale sunt circuitele care sunt sincronizate de un semnal de ceas, adică ale căror ieșiri nu se modifică decât pe frontul pozitiv (sau negativ, în funcție de descriere) de ceas.

Semnalul de ceas

Semnalul de ceas este un semnal periodic, care oscilează cu o anumită frecvență, numită frecvența de ceas.

Observație: Vezi sintaxa Verilog pentru a afla cum se generează un semnal de ceas în simulare.

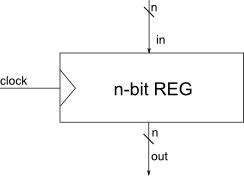

Circuite de memorare. Registrul

Registrul este celula elementară de memorare și baza circuitelor secvențiale. Odată o valoare încarcată într-un registru, aceasta se păstrează până la suprascrierea ei cu o altă valoare.

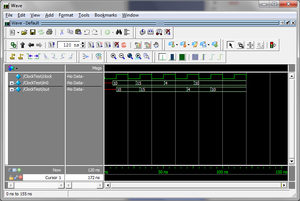

Aceasta este implementarea în Verilog a unui registru pe 4 biți care nu face decât să propage intrarea la ieșire și nimic mai mult iar în imagine puteți vedea o simulare Modelsim care arată că ieșirea nu se schimbă decât pe frontul pozitiv de ceas care urmează schimbării intrării:

module Register(

input clock,

input [3:0] in,

output reg [3:0] out

);

always@(posedge clock) begin

out <= in;

end

endmodule