CID Aplicatii 1

In aceasta sesiune de aplicatii, vom invata cum sa generam semnale digitale cu ajutorul limbajului Verilog. Generarea de semnale este utilizata in testarea prin simulare a circuitelor digitale. Semnalele generate sunt injectate la intrarea circuitului, observandu-se apoi cum se modifica starea iesirilor acestuia.

Notiuni si cunostinte necesare

- Introducere. Verilog HDL (Sintaxa Verilog)

Exemplul 1: Generarea a doua semnale digitale de 1 bit

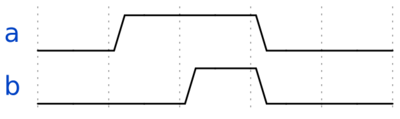

Sa se genereze doua semnale digitale de 1 bit, care sa aiba urmatoarea variatie in timp (unitatea de timp este de 1ns):

`timescale 1ns/1ps // setam unitatea de timp la 1ns, cu o precizie de 1ps

module waveform1(); // modulul nu are nicio intrare si nicio iesire. Semnalele de test generate sunt semnale interne ale modulului de test.

reg a, b; // cele doua semnale de test sunt modificate intr-un bloc de tip initial si trebuie declarate ca elemente de tip reg.

initial begin

$monitor("time = %2d, a = %b, b=%b", $time, a, b); // monitorizam in consola starea semnalelor a si b

a = 0; // semnalul a va avea valoarea 0 la momentul initial de timp (la momentul t = 0)

b = 0; // semnalul b va avea valoarea 0 la momentul initial de timp (la momentul t = 0)

#1 a = 1; // dupa 1ns de la momentul initial, a se face 1

#1 b = 1; // dupa 2ns de la momentul initial, b se face 1

#1 a = 0; // dupa 3ns de la momentul initial, a se face 0

b = 0; // dupa 3ns de la momentul initial, b se face 0

#2 $stop(); // simularea este oprita

end

endmodule // incheiem descrierea modulului de generare de semnale digitale

Exemplul 2: Generarea unui semnal periodic de 1 bit

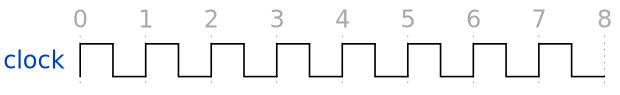

Sa se genereze un semnal digital periodic de 1 bit, cu perioada egala cu 2ns:

`timescale 1ns/1ps // setam unitatea de timp la 1ns, cu o precizie de 1ps

module waveform2(); // modulul se numeste waveform2 si nu are nicio intrare si nicio iesire

reg clock; // semnalul de test se va modifica intr-un bloc initial, asadar este declarat de tip reg

initial begin

clock = 0; // valoarea initiala a semnalului va fi 0 (la momentul t = 0)

forever #1 clock = ~clock; // forever indica faptul ca ce urmeaza se va repeta intr-o bucla continua.

// La trecea unui timp egal cu unitatea de timp definita, semnalul clock isi va nega valoarea

end

initial begin

#20 $stop(); // La 20 de unitati de timp (aici, 20 ns), simularea se va opri.

// Punem $stop intr-un bloc separat, deoarece forever blocheaza blocul initial in care se afla

// Toate blocurile initial incep la acelasi moment de timp (t = 0) si au efect in paralel

end

endmodule

Exemplul 3: Generarea unui semnal digital de 8 biti aliniat la fronturile crescatoare ale unui semnal de ceas

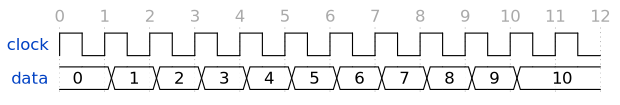

Sa se genereze un semnal digital de 8 biti aliniat la fronturile crescatoare ale unui semnal de ceas, ce are perioada de 2ns:

`timescale 1ns/1ps // setam unitatea de timp la 1ns, cu o precizie de 1ps

module waveform3(); // numele modulului este waveform3 si nu are nicio intrare si nicio iesire.

reg clock; // clock isi va modifica intr-un bloc initial, asadar este declarat de tip reg

reg [7:0] data; // data are 8 biti isi va modifica intr-un bloc initial, asadar este declarat de tip reg

integer i; // i este un index ce va fi folosit in blocul for si este declarat de tip integer

initial begin

$monitor("time = %2d, count = %b", $time, data); // monitorizam in consola starea semnalelor a si b

data = 0; // valoarea initiala (la momentul t = 0) a lui data este 0

for(i=0;i<10;i=i+1) begin // instructiunea for determina repetarea secventei urmatoare de 10 ori

@(posedge clock) // se asteapta frontul crescator al clock

data = i; // la fiecare front crescator al clock, data ia valoarea lui i

end

#2 $stop(); // dupa un timp egal cu doua unitati de timp de la ultima actualizare a lui data, simularea se opreste

end

initial begin

clock = 0; // valoarea initiala (la momentul t = 0) a lui clock este 0

forever #1 clock = ~clock; // La trecea unui timp egal cu unitatea de timp definita, semnalul clock isi va nega valoarea

end

endmodule

Exercitii suplimentare

1. Generati doua semnale digitale a si b de 1 bit, astfel incat sa se formeze cu ele toate cele 4 combinatii posibile:

t = 0ns: a = 0, b = 0 t = 1ns: a = 0, b = 1 t = 2ns: a = 1, b = 0 t = 3ns: a = 1, b = 1

2. Generati un semnal digital clock cu dimensiunea de 1 bit si perioada de 2ns si un semnal digital data, cu dimensiunea de 4 biti, aliniat la fronturile crescatoare ale semnalului clock. Semnalul data va varia astfel: 0, 1, 2, 3, 0, 1, 2 ,3, 0, 1 ... . Opriti simularea dupa ce semnalul data a realizat 4 variatii complete (s-a generat secventa 0, 1, 2, 3 de 4 ori).