Lab 1 - Intro to High Level Synthesis. Simulation. Co-simulation. RTL generation

Introduction

High-Level Synthesis (HLS) is a design methodology that enables hardware description at a higher level of abstraction, typically using C, C++, or SystemC, rather than traditional register-transfer level (RTL) coding. HLS tools automatically translate high-level specifications into optimized RTL implementations, reducing development time while allowing for design space exploration.

Setup

For this lab, we will be using the AMD Vitis tool. In order to access the tool, login into your assigned machine using tigervnc-viewer (please see the tutorial.

Once the GUI is opened, open a terminal and type:

source /nfs/amd/Vitis/2024.2/settings64.sh

vitis

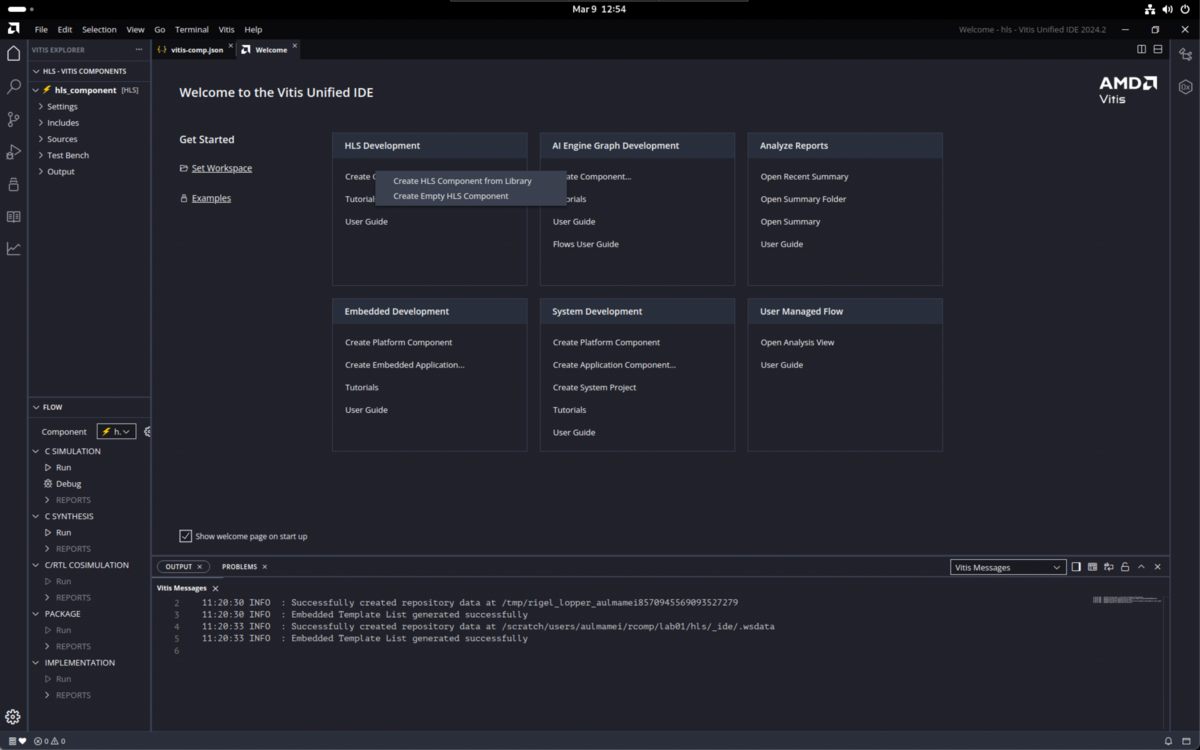

The Vitis window looks like this:

In order to create a new project, click on Create Component -> Create Empty HLS Component.

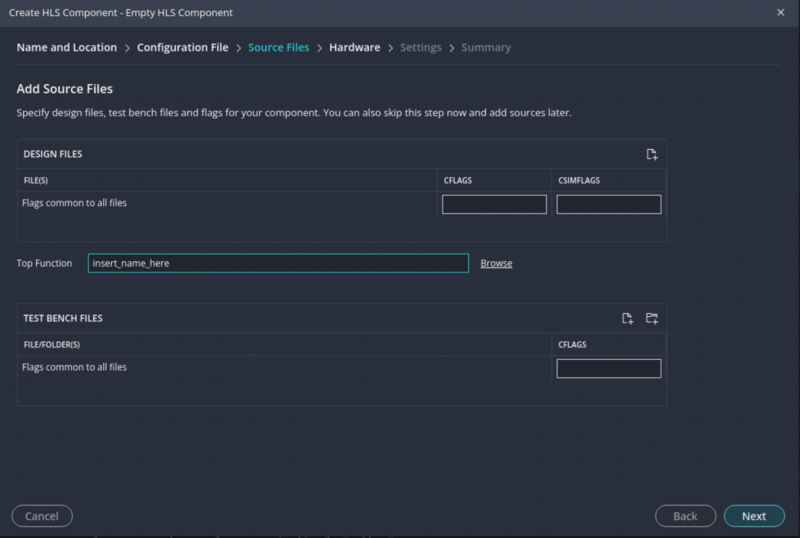

Follow the steps shown in the Vitis executable. At some point, you will have to pick a name for the top function. Beware that the function name should also appear in the declaration of it.

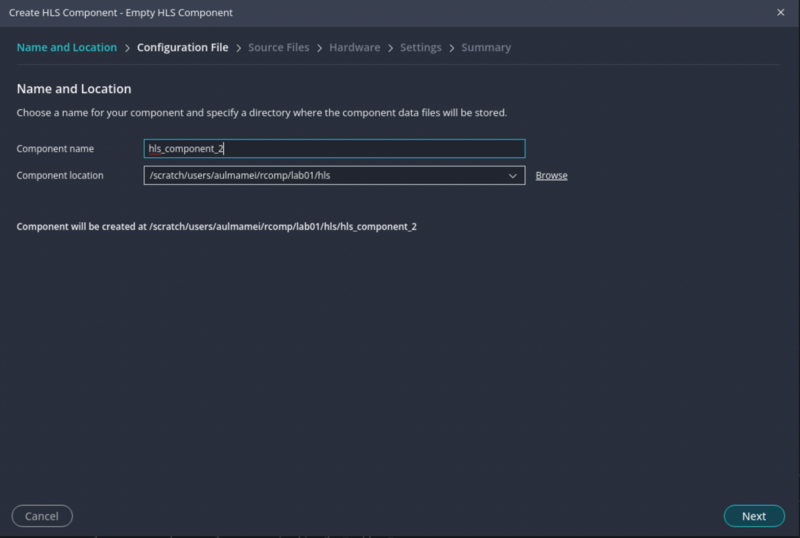

In Name and Location tab, choose a name for your HLS component and a location. In the Configuration File, leave everything as is. In Source Files, write your desired top level function under the textbox labeled Top Function.

Under the hardware section, select xc7z020iclg400-1l.

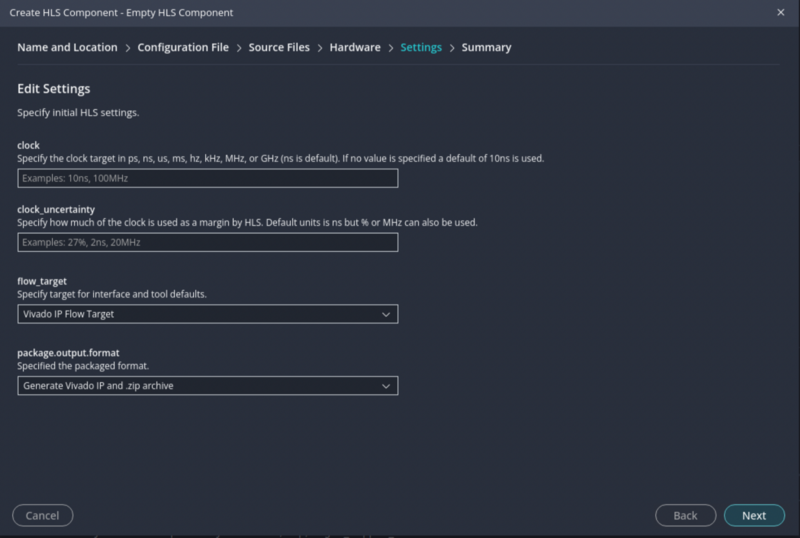

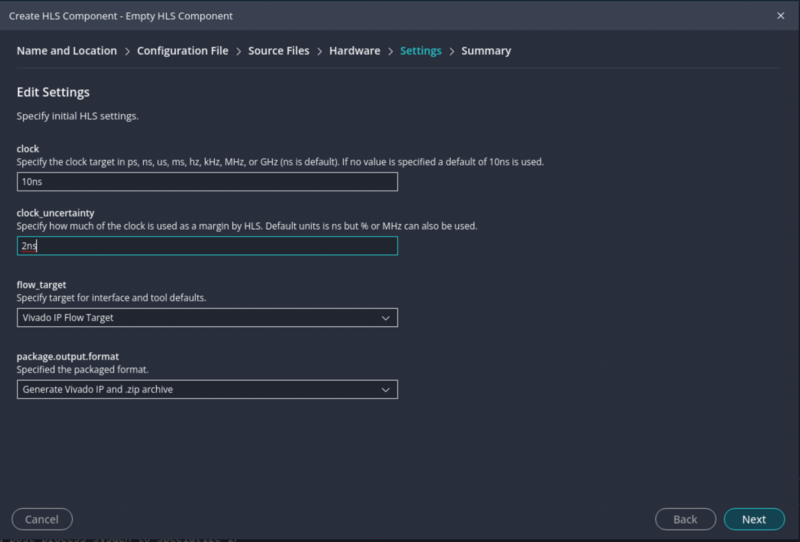

In the summary section, two pieces of information need to be provided:

- expected clock speed at which the circuit should operate: this constraints the tool to create a circuit that can function at that specific frequency

- clock uncertainty, how much the clock can vary around the expected value.

Next step, Settings, lets the user select the target operating frequency and clock uncertainty. For a safe design, we will choose 10ns for operating frequency and 2ns for clock uncertainty.

Now press next and finish. The project should be generated.

To create new sources, right click on Sources, then New Source File. To add C simulation testbench, right click on Test Bench, then New Test Bench File.