Diferență între revizuiri ale paginii „Circuitul de debounce”

| (Nu s-a afișat o versiune intermediară efectuată de același utilizator) | |||

| Linia 7: | Linia 7: | ||

<syntaxhighlight lang="Verilog"> | <syntaxhighlight lang="Verilog"> | ||

| − | module | + | module Debounce( |

output out, | output out, | ||

input clock, | input clock, | ||

| − | |||

input in | input in | ||

); | ); | ||

| Linia 22: | Linia 21: | ||

always@(posedge clock) begin | always@(posedge clock) begin | ||

| − | + | if(!in) begin | |

counter <= 0; | counter <= 0; | ||

| − | hit <= 0; | + | hit <= 0; |

| − | + | end else if(counter == limit) begin | |

hit <= 1; | hit <= 1; | ||

counter <= counter + 1; | counter <= counter + 1; | ||

| − | |||

| − | |||

| − | |||

end else if(in & !hit) begin | end else if(in & !hit) begin | ||

counter <= counter + 1; | counter <= counter + 1; | ||

Versiunea curentă din 28 martie 2012 08:30

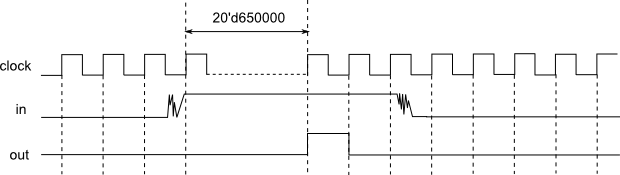

În circuitele secvențiale, orice variabilă de intrare care nu este dependentă de ceasul sistemului, este o intrare asincronă. Majoritatea acestor intrări asincrone provin de la dispozitive mecanice, cum ar fi cele patru butoane de pe placa de dezvoltare din laborator. Pe lângă faptul ca sunt asincrone, aceste semnale nu sunt perfect dreptunghiulare, elementele mecanice din interiorul butoanelor avand nevoie de un mic timp pentru a se stabiliza. In acest timp semnalul generat este format din multe spike-uri, care conduc la funcționarea gresită a circuitului nostru (se comportă ca un semnal dreptunghiular de frecvența foarte mare). Ne propunem să rezolvăm această problemă prin ignorarea acelei perioade din semnal (cateva milisecunde). Acest lucru îl face circuitul de Debounce, care primește la intrare un semnal, asemanator lui in din figura de mai jos și generează la ieșire un semnal perfect dreptunghiular, de durata unei singure perioade de ceas (out din figura de mai jos).

Implementarea unui circuit de debounce

module Debounce(

output out,

input clock,

input in

);

parameter limit = 20'd650000;

reg [19:0] counter;

reg hit;

assign out = (counter == limit);

always@(posedge clock) begin

if(!in) begin

counter <= 0;

hit <= 0;

end else if(counter == limit) begin

hit <= 1;

counter <= counter + 1;

end else if(in & !hit) begin

counter <= counter + 1;

end

end

endmodule