CID Lab Lucrarea 0: Diferență între versiuni

De la WikiLabs

Jump to navigationJump to search

Fără descriere a modificării |

|||

| Linia 27: | Linia 27: | ||

Schema electrică a plăcii de dezvoltare este disponibilă aici: [[Fișier:placa_integrate_cid_proiect.pdf]] | Schema electrică a plăcii de dezvoltare este disponibilă aici: [[Fișier:placa_integrate_cid_proiect.pdf]] | ||

== | == Exemplu == | ||

[[Image:Sem1tema1.png|thumb|right|300px|Schema de circuit a multiplexorului]] | |||

Se va implementa, cu ajutorul cadrului didactic dacă este necesar, un circuit de selecție (multiplexor) folosind placa de dezvoltare: | |||

* Se vor folosi combinațiile de porți ȘI-NU/SAU-NU și inversoare pentru realizarea porților ȘI/SAU din schema circuitului. | |||

* Se va folosi o poartă ȘI-NU pentru a implementa inversorul din schema circuitului, legând ambele intrări ale porții ȘI-NU la semnalul ce trebuie inversat. | |||

* Ieșirea circuitului va fi conectată la unul din LED-uri pentru a vizualiza valoarea sa logică | |||

== Cerințe == | |||

Versiunea de la data 22 februarie 2015 12:08

Noțiuni și cunoștințe necesare

Placa de dezvoltare

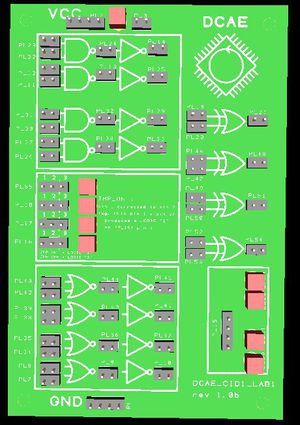

În acest laborator veti folosi o placa de dezvoltare echipată cu circuite integrate digitale ce oferă următoarele funcții logice:

- 4 porți ȘI-NU, la ale căror ieșiri sunt conectate inversoare, putând astfel fi folosite ca porți ȘI

- 4 porți SAU-NU, la ale căror ieșiri sunt conectate inversoare, putând astfel fi folosite ca porți SAU

- 4 porti XOR

- 4 intrări logice selectabile prin câte un jumper, și echipate cu câte un LED care indică valoarea logică selectată (LED aprins pentru 1 logic, stins pentru 0 logic)

- 4 conexiuni la alimentare (VCC de 5V)

- 4 conexiuni la masă

- 4 LED-uri ce pot fi folosite pentru a vizualiza valoarea logică a oricărui punct din circuit (LED aprins pentru 1 logic, stins pentru 0 logic)

Reguli de folosire a plăcii de dezvoltare:

- Placa trebuie alimentată folosind un cablu USB conectat la calculator, astfel încât LED-ul de alimentare să fie aprins

- Ieșirile unei porți pot fi conectate la intrările altei porți prin fire, ce vor fi puse la dispoziție împreună cu placa de dezvoltare

- Nu se vor lega între ele ieșirile a două porți

- Atenție, fiecare intrare de poartă logică are doi pini, dintre care maxim unul va fi conectat la ieșirea unei porți logice, celălalt putând fi legat la intrarea unei porți logice

- Inversoarele de pe placă au deja conectate intrările la ieșirile porților ȘI-NU/SAU-NU asociate, deci pinii de pe intrarile inversoarelor nu pot fi folosiți pentru a lega intrarea inversoarelor cu ieșirea unei alte porți de pe placă.

- Funcția de inversare poate fi implementată și prin intermediul porților ȘI-NU sau XOR de pe placă

- Nu se vor lega ieșirile porților la VCC sau masă

Schema electrică a plăcii de dezvoltare este disponibilă aici: Fișier:Placa integrate cid proiect.pdf

Exemplu

Se va implementa, cu ajutorul cadrului didactic dacă este necesar, un circuit de selecție (multiplexor) folosind placa de dezvoltare:

- Se vor folosi combinațiile de porți ȘI-NU/SAU-NU și inversoare pentru realizarea porților ȘI/SAU din schema circuitului.

- Se va folosi o poartă ȘI-NU pentru a implementa inversorul din schema circuitului, legând ambele intrări ale porții ȘI-NU la semnalul ce trebuie inversat.

- Ieșirea circuitului va fi conectată la unul din LED-uri pentru a vizualiza valoarea sa logică