Diferență între revizuiri ale paginii „Verilog EN”

Cbira (discuție | contribuții) |

Cbira (discuție | contribuții) |

||

| Linia 155: | Linia 155: | ||

endmodule | endmodule | ||

| − | <syntaxhighlight> | + | </syntaxhighlight> |

'''' 'Note:''''' Generally, a block '''assign''' will generate a synthesizable circuit. There are also exceptions when the desired operation is too complex to be implemented through a combinational circuit effectively. E.g: | '''' 'Note:''''' Generally, a block '''assign''' will generate a synthesizable circuit. There are also exceptions when the desired operation is too complex to be implemented through a combinational circuit effectively. E.g: | ||

| Linia 161: | Linia 161: | ||

<syntaxhighlight lang="Verilog"> | <syntaxhighlight lang="Verilog"> | ||

assign out=in0 /in1; | assign out=in0 /in1; | ||

| − | <syntaxhighlight> | + | </syntaxhighlight> |

is not a synthesizable code for most synthesis tools, but works fine in a simulation. | is not a synthesizable code for most synthesis tools, but works fine in a simulation. | ||

| Linia 175: | Linia 175: | ||

end | end | ||

| − | <syntaxhighlight> | + | </syntaxhighlight> |

As the name calls it, the list of sensitivities is the list of sensitive signals, that is, the registers described by the block '''always''' depend on. If only the name of a signal is passed in the list of sensitivities without any additional specifiers, then the block is sensitive to any change of this signal. If a block '''always''' has more signals to which it is sensitive, they split into the sensitivity list using the keyword '''or'''. | As the name calls it, the list of sensitivities is the list of sensitive signals, that is, the registers described by the block '''always''' depend on. If only the name of a signal is passed in the list of sensitivities without any additional specifiers, then the block is sensitive to any change of this signal. If a block '''always''' has more signals to which it is sensitive, they split into the sensitivity list using the keyword '''or'''. | ||

| Linia 195: | Linia 195: | ||

endmodule | endmodule | ||

| − | <syntaxhighlight> | + | </syntaxhighlight> |

==== Blocks '''always''' sequential. Non-blocking assignments ==== | ==== Blocks '''always''' sequential. Non-blocking assignments ==== | ||

[[Sequential Circuits | Sequential Circuits]] are circuits that are synchronized by [Sequence Circuits #Clock Signal | Clock Signal]. This signal is usually produced by a clock generator and is defined as input for each sequential module (in which there is at least one register). We can modify the previous example so that the output of the summation module is synchronous (that is, change only on the positive clock front). Thus, in | [[Sequential Circuits | Sequential Circuits]] are circuits that are synchronized by [Sequence Circuits #Clock Signal | Clock Signal]. This signal is usually produced by a clock generator and is defined as input for each sequential module (in which there is at least one register). We can modify the previous example so that the output of the summation module is synchronous (that is, change only on the positive clock front). Thus, in | ||

Versiunea de la data 11 aprilie 2018 23:38

Modules (synthesizable)

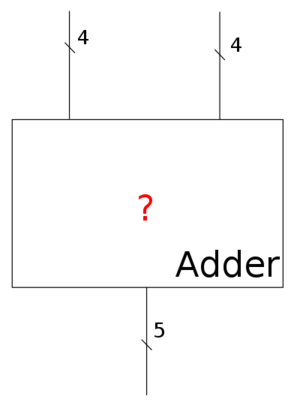

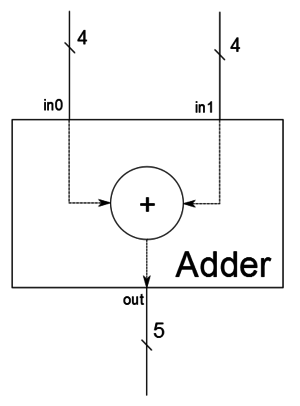

The Verilog language is structured on modules. Each module represents a circuit that implements a certain function. For example, a module may be a summation, ie a circuit that has two entries specifying the two operands and an output representing the result of the assembly. The content of the module is the (structural or behavioral) description of the gates that computes the sum of the two entries. Therefore, the definition of a Verilog module has two parts:

- interface - the list of all the input and output ports of the circuit, specified by name and size;

- implementation - actual circuit description using input values to calculate output values;

Verilog Module Interface

The Adder module interface is shown below. ' Note: ' As in the decimal system, where the sum of two numbers n digits needs n + 1 digits (9 + 9=18), and in the binary system, the sum of two n bits will be on n + 1 bits.

module Adder (

output [4: 0] out,

input [3: 0] in0,

input [3: 0] in1

)

//implementation

endmodule

The keywords module and endmodule are used to start and end defining a module. Immediately after the keyword module follows the module name.

Convention: The name of a module will begin with a large letter.

After defining the module name, the list of ports, placed between round brackets and separated by comma follows. Accepted keywords are output (representing an output port), input (representing an input port) and inout(representing a bidirectional port).

Tip: . They introduce Tri-state Buffer elements that are ineffective. A more efficient alternative is to define two ports, one input and one output, with similar names (ex: data_in and data_out ).

Convention: First the outputs, then the inputs of a module are defined.

Convention: module .

According to the port type, it follows its size, specified in the bit indexes, where the least significant bit has the index 0. For example, a 4 bit signal will have the following specification: [3:0] significantly has index 3, least significant 0, total 4 bits). Note: One-bit signals lack the size specification:

input signal_de_un_bit,

After the list of ports in brackets, the interface definition ends with the ; character.

<! -

- Remark: There are non-synthesizable modules (which do not have logical gaps), which are used as test programs in simulation environments and are called test modules. These modules have no input and output ports and are used only to give the input port values of the module to be tested, and to check the values on the output ports of the module. For these modules, the list of ports and their associated parentheses are missing:

Module TestModule;

//implementation

endmodule

->

Implementing Verilog Modules

The implementation of Verilog modules is done through blocks. These blocks may or may not correspond to a physical scent. If all blocks of a module have a correspondent in a physical circuit, then the module is synthesizable and can be transformed into a physical circuit. Blocks that can generate synthesizable constructions are of four types:

- blocks assign

- blocks always

- Instance blocks

- blocks generated

In addition, Verilog can define threads (wire) and registers (reg).

Blocks that are always unintelligible and are used exclusively for simulation:

- blocks initial

' Remark: ' Not any block assign or always is synthesizable. There are syntactic constructs that do not have a correspondent in the circuit. These blocks can be simulated but can not be used to program an FPGA board.

Note: The order of blocks in a module does not matter.

Wires (wire) and registers (reg)

The threads are used for linking modules and for assigning partial results to combinational circuits, therefore:

Rule: or as the output of a module (never both simultaneously).

The threads in a Verilog module are defined as follows:

wire [3:0] wire;

Registers are commonly used to implement sequential stumps, and then they define physical registers, but:

Remark: does not necessarily translate into a physical register. Translating it depends on how it is used.

A register is defined as follows:

reg [3:0] register;

Rule: or initial.

Rule: No element can change its value in more than one block. That is, for a wire ( wire ), there can not be two blocks assign' in which it takes values, and for the elements reg'always or initial in which it changes its value.

Note: An entry of a module is always wire. Thus, the statement

input [3:0] in0,

is equivalent to

input wire [3:0] in0,

Remark: An output of a module may be wire or reg. If not specified, it is a wiretype. Thus, the statement

output [4:0] out,

is equivalent to

output wire [4:0] out,

Blocks assign

Assign is a key word that generates combinational circuits. As the summator is a combinational circuit, and output is implicitly wire type, we can implement it with a block assign:

module Adder (

output [4: 0] out,

input [3: 0] in0,

input [3: 0] in1

)

assign out=in0 + in1;

endmodule

' 'Note: Generally, a block assign will generate a synthesizable circuit. There are also exceptions when the desired operation is too complex to be implemented through a combinational circuit effectively. E.g:

assign out=in0 /in1;

is not a synthesizable code for most synthesis tools, but works fine in a simulation.

Combined always' blocks

Always, a block always is used to give values of reg signals. A block always may translate into [combinational circuits]] or sequential circuits, depending on its list of sensitivities. The general format for a always block is the following:

always @ (<sensitivity list>) begin

//...

end

As the name calls it, the list of sensitivities is the list of sensitive signals, that is, the registers described by the block always depend on. If only the name of a signal is passed in the list of sensitivities without any additional specifiers, then the block is sensitive to any change of this signal. If a block always has more signals to which it is sensitive, they split into the sensitivity list using the keyword or.

' 'Note: If the list of sensitivities contains only signals without other specifiers, then the result of the block synthesis will be a combinational circuit.

In this case, we can redo the implementation of the summator using a block always as follows:

module Adder (

output reg [4: 0] out,

input [3: 0] in0,

input [3: 0] in1

)

always @ (in0 or in1) begin

out=in0 + in1;

end

endmodule

Blocks always sequential. Non-blocking assignments

Sequential Circuits are circuits that are synchronized by [Sequence Circuits #Clock Signal | Clock Signal]. This signal is usually produced by a clock generator and is defined as input for each sequential module (in which there is at least one register). We can modify the previous example so that the output of the summation module is synchronous (that is, change only on the positive clock front). Thus, in